- 全部

- 默认排序

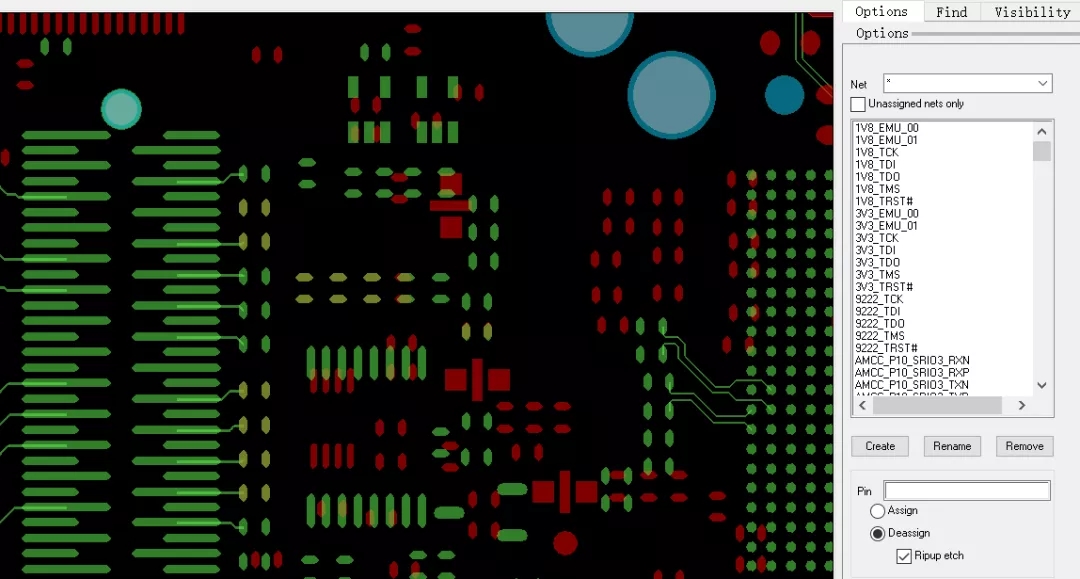

Allegro的全称是Cadence Allegro PCB Designer,是Cadence公司推出的一个完整的、高性能印制电路板设计套件。通过顶尖的技术,它为创建和编辑复杂、多层、高速、高密度的印制电路板设计提供了一个交互式、约束驱动的设计环境。它允许用户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住今天最具挑战性的设计问题。Allegro印制电路板设计提高了PCB设计效率和缩短设计周期,让您的产品尽快进入量产(目前高速PCB设计用的最多工具,就是Allegro)。

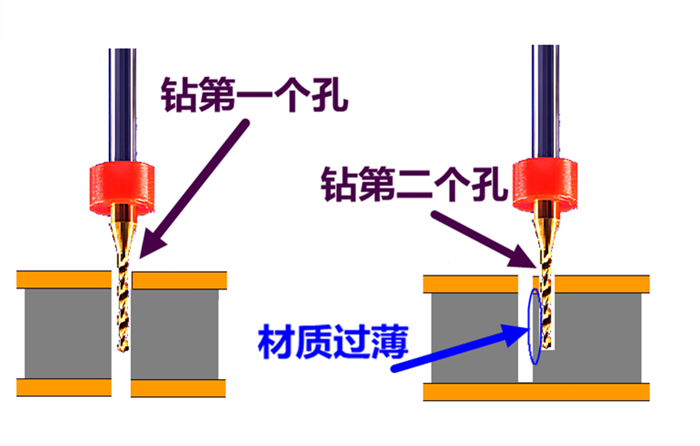

PCB板设计时,我们布线考虑最多的,是如何把各个层同网络信号线用最合理的方式连接,高速PCB板线路越密集过孔(VIA)放置的密度就越大,过孔能起到各层间电气连接的作用。多层线路板PCB打样经常会收到板厂反馈“孔到线过近,超出了制程能力”,那么过孔过近对生产会有什么难点,对产品可靠性又有什么影响呢?

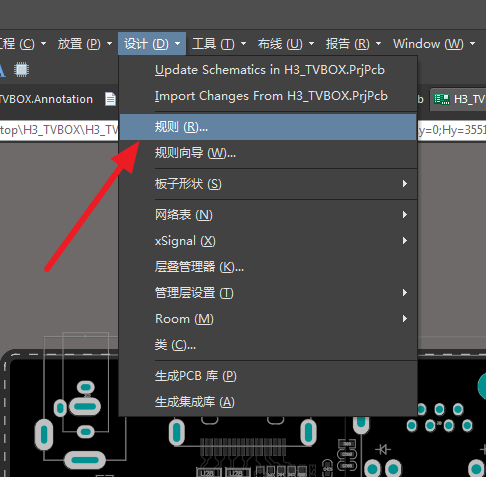

在我们进行PCB设计的时候,布线规则设置也是我们及其重要的一项。布线规则中着重关注的是线宽规则和过孔规则。因为在进行高速PCB设计的时候一般需要用到阻抗线,那么对于每层的线宽要求是不一致的。而且有时候又考虑到电源线的特殊性,对于电源线线宽有特殊的要求。所以我们的线宽规则的重要性不容置疑了。那么我们对于过孔规则就是考虑到在生产的时候不要过多的过孔属性类型,因为种类太多的话,生产的时候就要频繁的换钻头,所以一个PCB设计中不要超过两种过孔类型。

刚大学毕业或者已经参加工作 1-2 年的你,是否慢慢的发现了很多你当初进入的行业或者目前从事的 PCB 画板行业所设计的PCB 层级过于简单,一直在 2 层低速这类板卡转悠呢? 于个人发展,前景及钱景是否和之前想象的存在差距,可能目前公司上班所学到的技能对自己职业生涯的提高已经达到了瓶颈,如何突破是你现在阶段的你急需要思考的问 题,趁自己还年轻,趁自己还冲劲的时候努力给自己寻求另外一条道路呢,要么看到前景, 那么看到钱景,促使自我“价值”提高! &

判断一个信号是否为高速信号首先要区分几个误区。误区一:信号周期频率FCLOCK高的才属于高速电路设计其实我们在电路设计时考虑的最高频率往往取决于信号的有效频率(亦称转折频率)Fknee。 如上图信号周期频率与有效(转折)频率定义为:(实际中多数信号)误区二:电容、电感式理想器件在低速领域,电容、电感工作频段比较低,可以认为他们是理想器件。但在高速领域,PCB上的电容电感等已经不能简单的视为纯粹的电容电感了。例如:在低速领域电容我们可以视为断路,而在高速电路中,假设工作频率为F,则电容C

在高速PCB设计中,“信号”始终是工程师无法绕开的一个知识点。不管是在设计环节,还是在测试环节,信号质量都值得关注。在本文中,我们主要来了解下影响信号质量的5大问题。

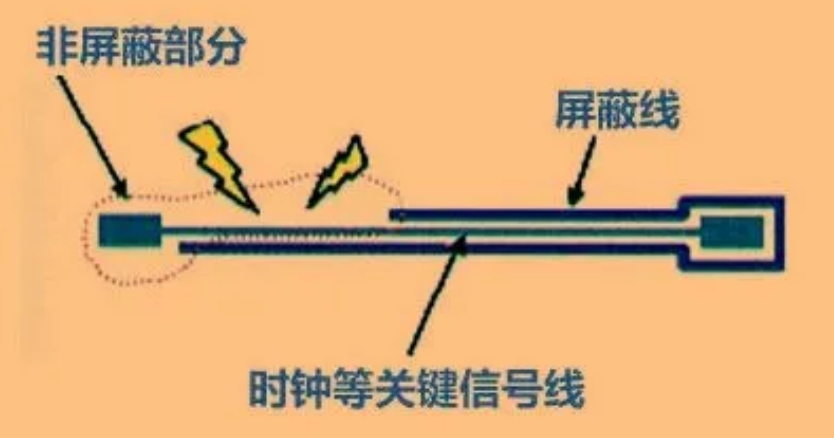

随着信号上升沿时间的减小及信号频率的提高,电子产品的EMI问题越来越受到电子工程师的关注,几乎60%的EMI问题都可以通过高速PCB来解决。以下是九大规则:

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:Ø 源端端接,接在信号源端或信号发送端的端接,一般与信号走线串接;Ø 终端端接,接在信号终端或信号接收端的端接,一般与信号走线并接。源端端接的优点是接供较慢的上升时间,减少反射量,产生更小的EMI,从而降低过冲,增加信号的传输质量。我们在PCB设计中处理源

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:

凡亿双十一第三场活动——F3系列88折限时开启~想学习高速PCB设计的小伙伴们,可以考虑考虑是否要报名学习一下呢?活动期间下单将赠送快捷键鼠标垫任意1款+7把趣味直尺,11号零点还能抢满200-30上不封顶的优惠券哦!心动的小伙伴们,赶紧行动起来吧!

扫码关注

扫码关注