- 全部

- 默认排序

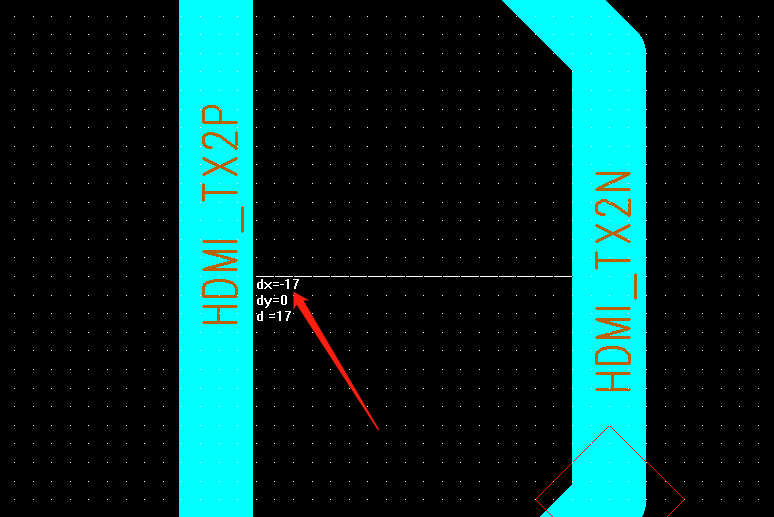

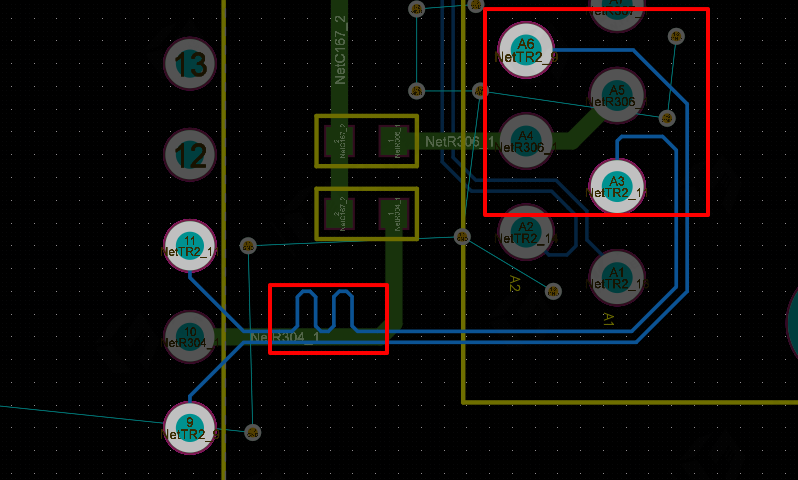

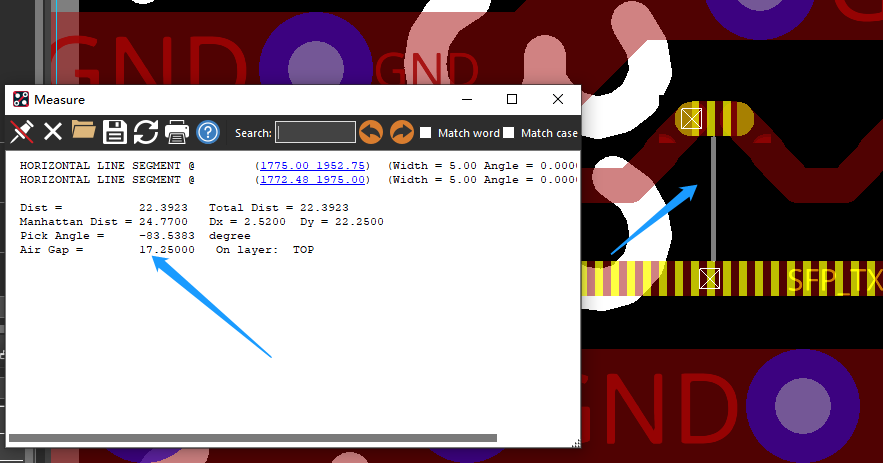

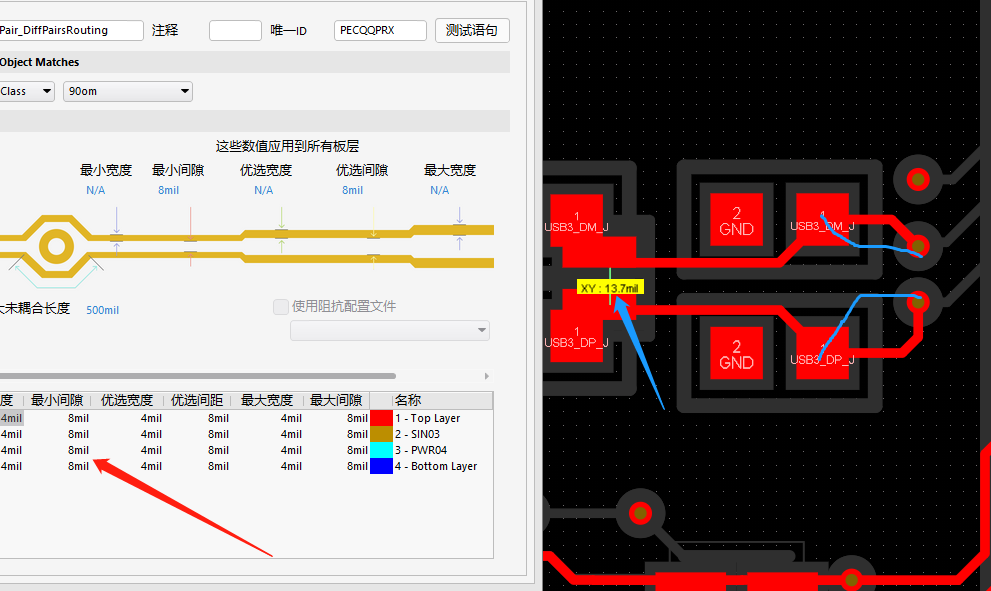

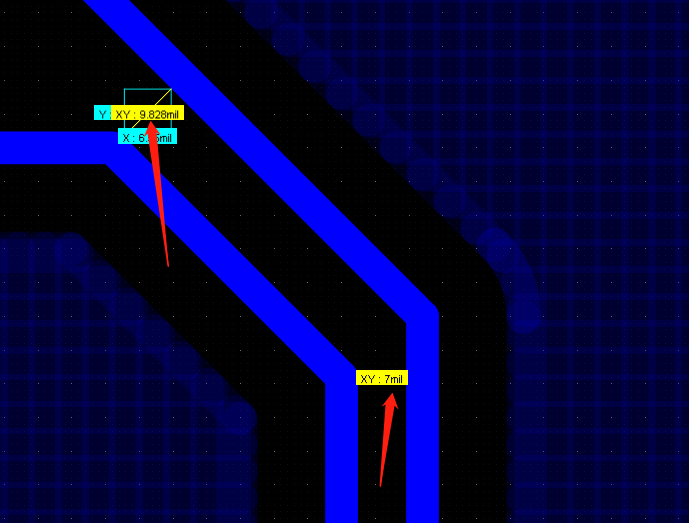

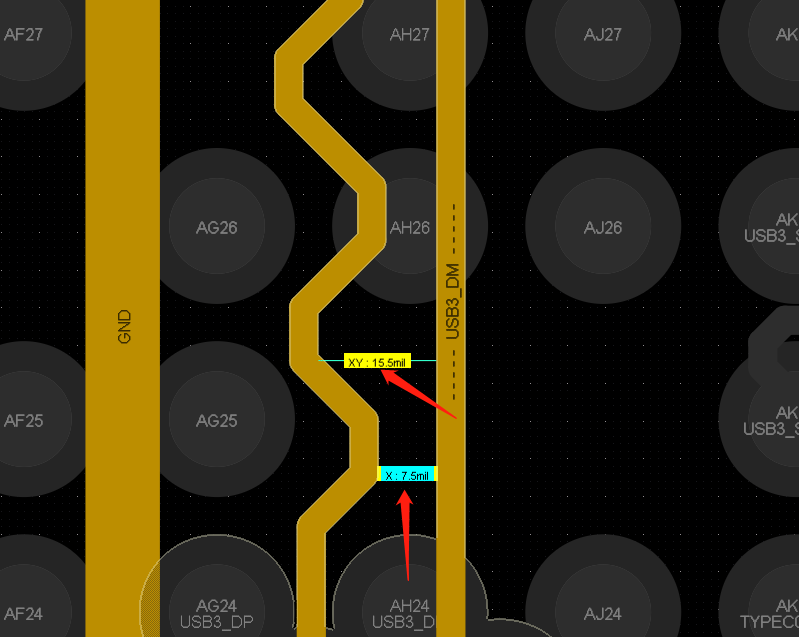

差分线对内等长凸起高度不能超过线距的两倍2.差分对内绕等长绕一边即可3.走线需要优化一下,尽量不要走任意角度4.差分出线需要优化一下5.存在开路6.地网络尽量就近打孔连接到地平面走线尽量不要超过器件外框丝印,走线离焊盘太近,后期容易短路差分

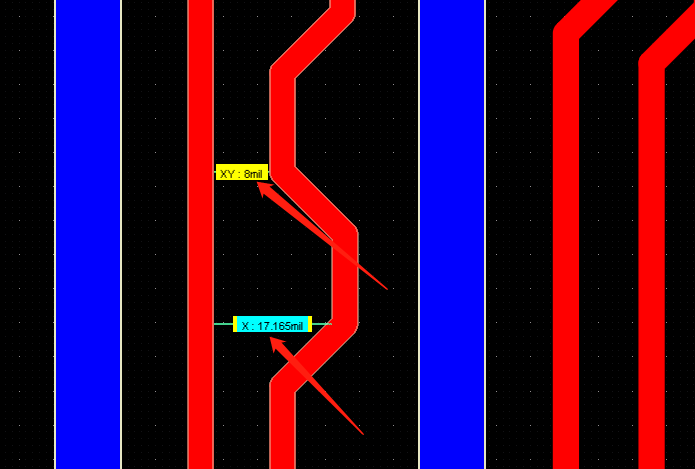

差分等长错误:1.尽量在引起不等长端绕线 2.差分对内等长绕线高度和间距不规范地址线要单根包地打孔处理tx、rx分别建立等长组等长,两组走线之间保持4w间距,有空间单组包地或两组包地以上评审报告

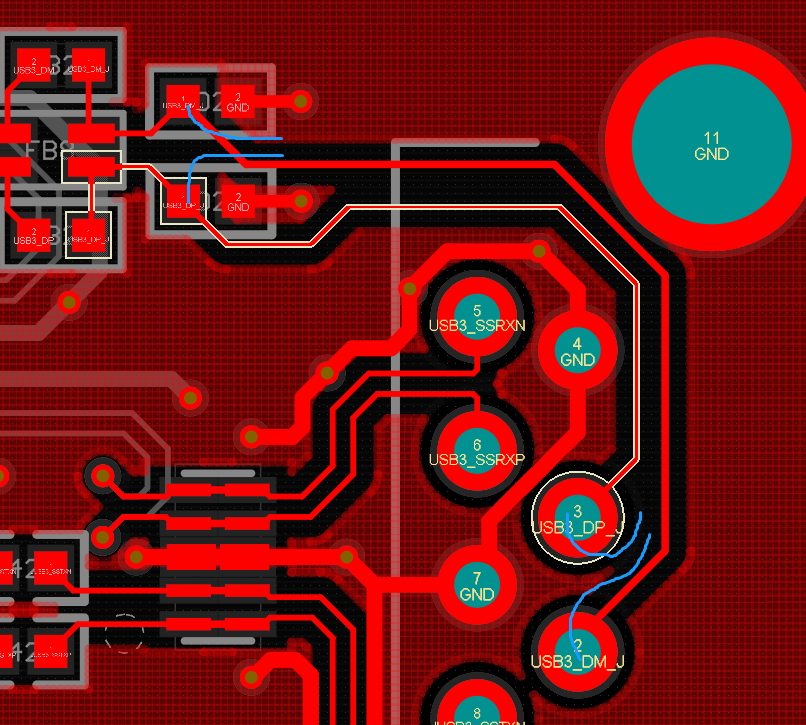

差分对内等长凸起高度不能超过线距的两倍差分走线不满足差分阻抗间距要求3.光口模块座子下面需要所有层挖空处理4.后期自己在电源层铺铜尽量连接差分出线方式需要再优化一下跨接地旁边可以尽量多打地过孔以上评审报告来源于凡亿教育90天高速PCB特训班

差分走线要按照阻抗间距走,差分出线要尽量耦合,后期自己优化一下有好几处差分没有按照阻抗线距走,后期自己调整一下2.差分对内等长凸起高度不能超过线距的两倍3.CC1和CC2属于重要信号,走线需要加粗4.走线需要优化一下,尽量不要有直角5.差分

差分需要按照阻抗线距走,后期埃及调整一下2.差分对内等长凸起高度不能超过线距的两倍网口座子需要靠近板框摆放3.差分出线要尽量耦合,走线需要优化一下4.时钟信号包地需要在地线上打孔,建议50mil-100mil一个以上评审报告来源于凡亿教育9

差分线对内等长凸起高度不能超过线距的两倍2.存在开路3.注意差分需要进行对内等长,误差5mil4.注意等长尽量不要直角,建议钝角,后期自己优化一下5.后期自己在地平面和电源平面指定网络进行连接6.差分需要按照阻抗线距走,后期自己注意一下以上

差分对内等长凸起高度不能超过线距的两倍2.焊盘出线可以在优化一下3.差分走线需要按照阻抗线宽线距进行走线4.pcb上不要存在stub线5.注意差分对内等长误差5mil6.存在多处开路,后期自己检查一下drc7.过孔到焊盘间距太近,间距最少6

注意差分出线要尽量耦合,走一起2.注意差分走线需要按照阻抗线宽线距走线,否则容易产生阻抗突变3.打孔要打在ESD器件前面4.走线一层连通不用打孔差分需要进行对内等长,误差5mil差分对内等长凸起高度不能超过线距的两倍注意器件摆放不要干涉一脚

注意差分凸起高度不能超过线距的两倍2.差分走线需要优化一下3.时钟信号尽量包地处理4.电容尽量靠近管脚均匀摆放5.差分出线要尽量耦合,后期自己优化一下6.存在多处开路后期自己在顶底层铺上电源和地铜皮7.变压器需要挖空所有层处理

电子人都知道,FPGA是高度集成的芯片,具有大量可配置逻辑块和I/O(输入/输出)接口,因此需要精确的电源管理来满足其运行需求,然而这并非容易得事情,在选择电源方案时需要考虑多种因素,以确保稳定、可靠的性能。1、为什么选择电源解决方案很重要

扫码关注

扫码关注