- 全部

- 默认排序

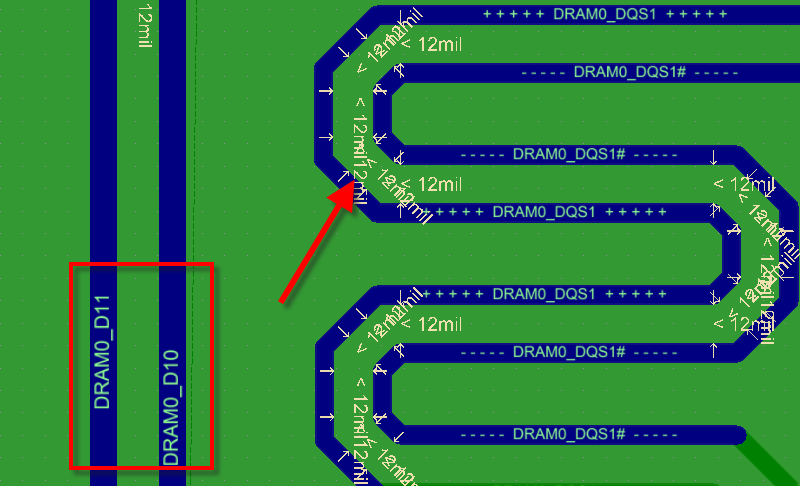

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

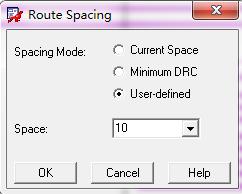

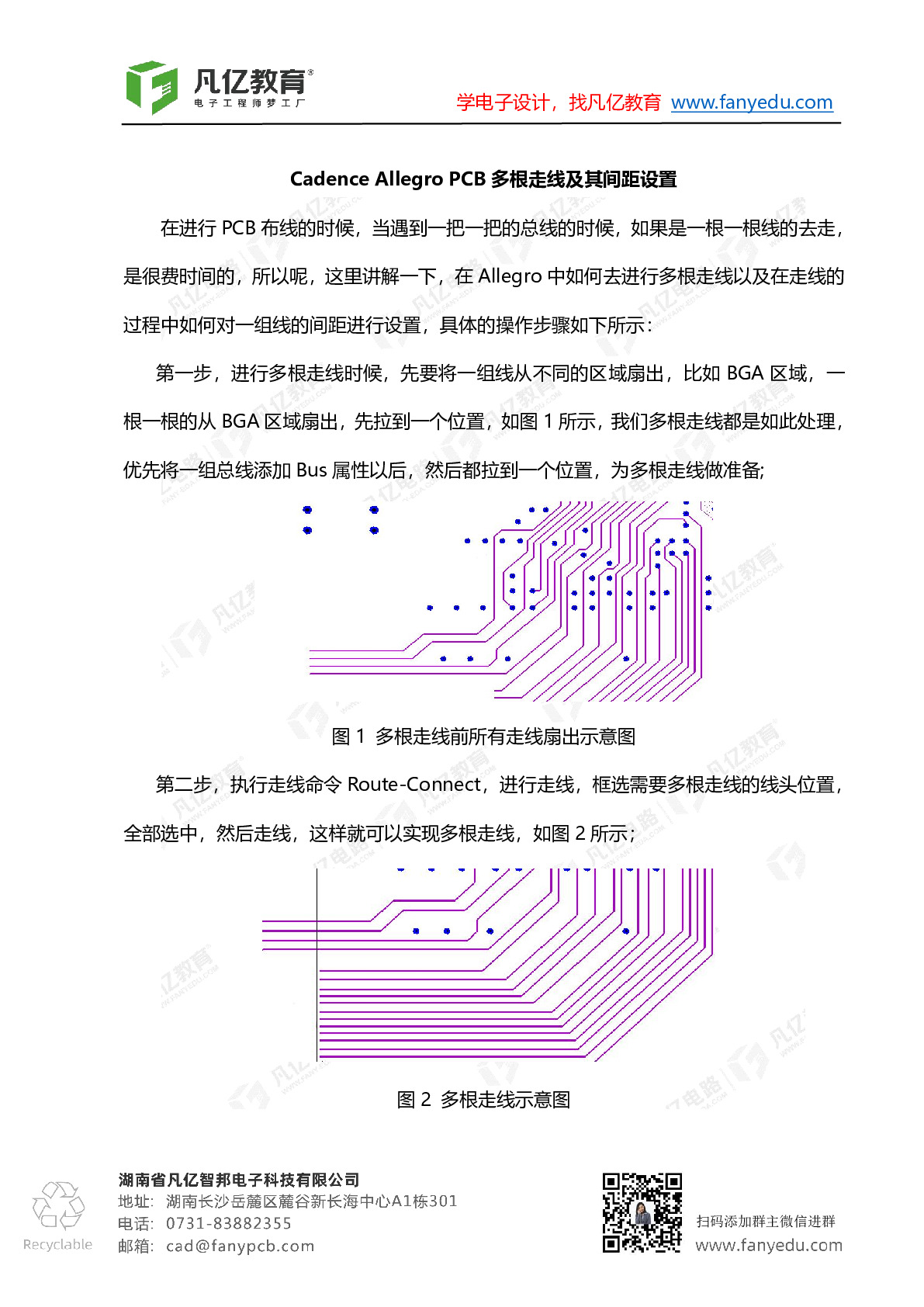

答:我们在进行PCB布线的时候,当遇到一把一把的总线的时候,如果是一根一根线的去走,是很费时间的,所以呢,这里我们讲解一下,在Allegro中如何去进行多根走线以及在走线的过程中如何对一组线的间距进行设置,具体的操作步骤如下所示:

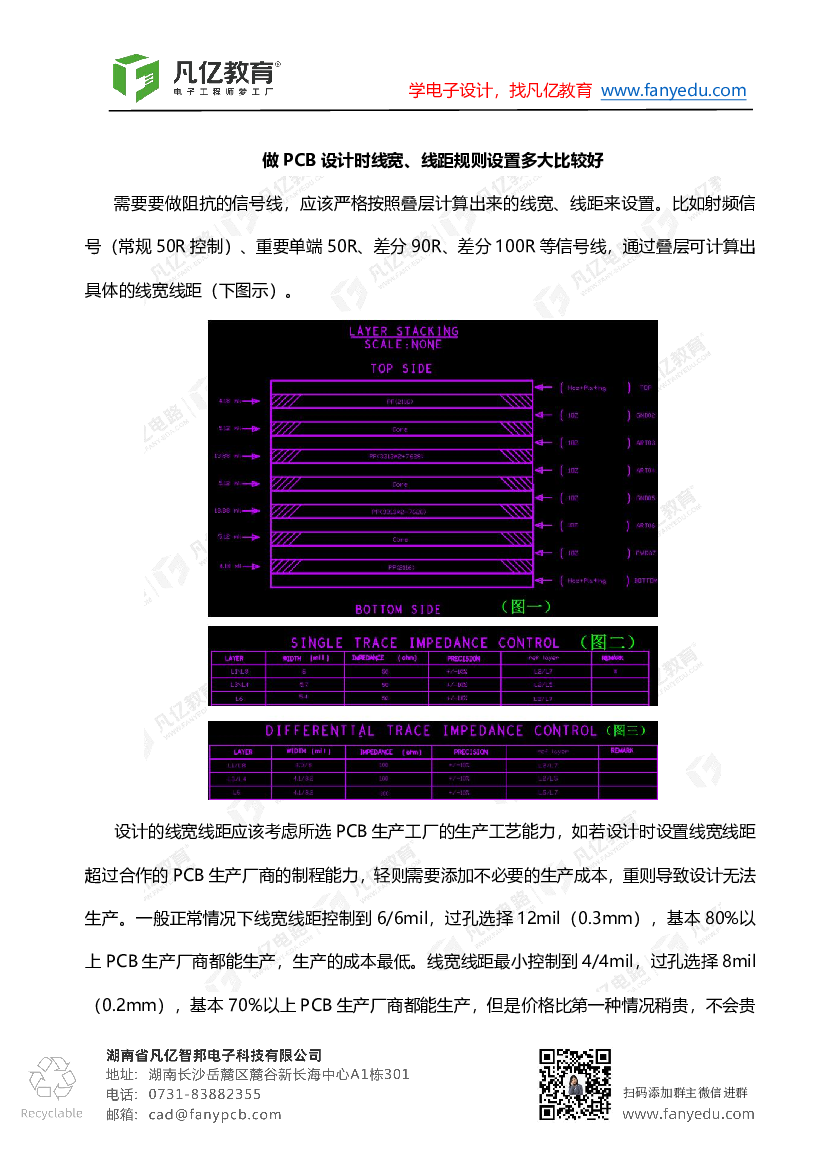

本文要点IPC 器件间距指南旨在确保器件和电路的间距足够大,以尽量减少物理重叠和电气干扰。钻孔的间距很重要,因为钻孔的功能会受到器件间距以及 PCB 本身所用材料的影响。IPC 器件间距指南会影响电路设计,因为其中规定了许多关于导体的具体要求。IPC 是一个国际电子组织,定义了制造 PCB 的标准。

2017-7-12 16:21 上传请教:管脚之间距离过短,这个在规则里面那个地方设置啊规则查了一遍,也没找到管脚到管脚之间的间距设置

电路中有许多网络NET, 然后我建立了class类来管理他们,我想对不同的类,设置不同的间距比如 VCC_1 类,我设置相同线直接的间距至少为1.524mm, 然后设置Vcc2类中相同类线的间距至少为1.08mm..点击确定,AD直接报错/ 这是怎么回事? 难道不可以对不同网络线中的相同网络设置不同的间距?

扫码关注

扫码关注