- 全部

- 默认排序

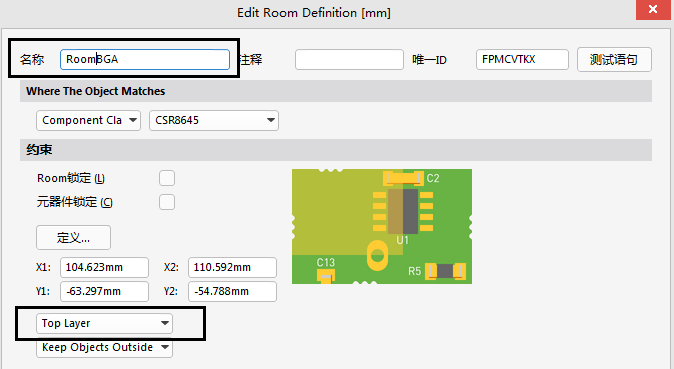

区域(Room)规则设置是针对某个区域来设置规则。为了满足设计阻抗和工艺能力的要求,需要对个别区域设置特殊的线宽走线或者间距或者过孔大小等,这时可以对这个区域进行特殊规则设置,常用于各类不同Pitch间距的BGA。

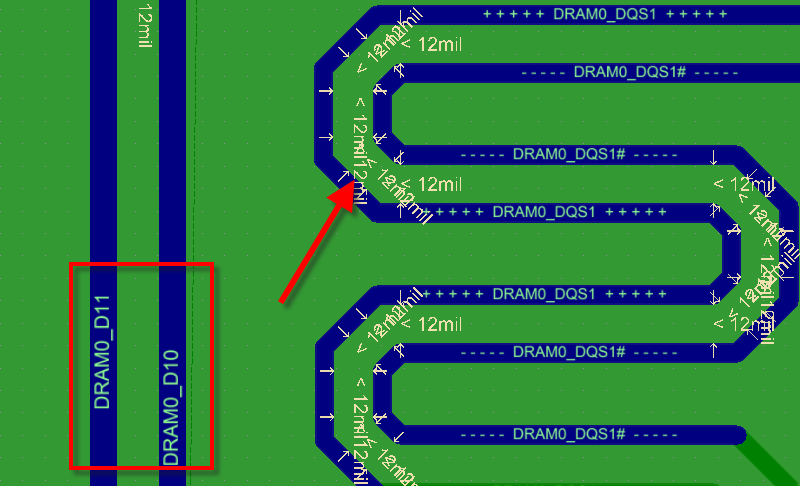

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

爬电距离:沿绝缘表面测得的两个导电零部件之间或导电零部件与设备防护界面之间的最短路径。 电气间隙:在两个导电零部件之间或导电零部件与设备防护界面之间测得的最短空间距离。即在保证电气性能稳定和安全的情况下,通过空气能实现绝缘的最短距离。

一般来说,影响PCB特性阻抗的因素:介质厚度H、铜的厚度T、走线的宽度W、走线的间距、叠层选取的材质的介电常数Er、阻焊的厚度。一般来说,介质厚度、线距越大阻抗值越大;介电常数、铜厚、线宽、阻焊厚度越大阻抗值越小。这些因素与特性阻抗的关系如图1-20所示。 图1-20 影响PCB特性阻抗分布图第一个:介质厚度,增加介质厚度可以提高阻抗,降低介质厚度可以减小阻抗;不同的半固化片有不同的胶含量与厚度。其压合后的厚度与压机的平整性、压板的程序有关;对所使用的任何一种板材,要取得其可生产的介质

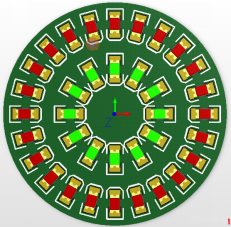

Altium极坐标的应用

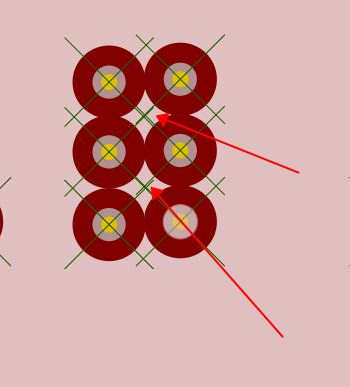

如图13,在PCB设计行业当中,特别是LED灯板行业,我们需要对LED灯珠进行圆弧等间距进行排列,如果我们每个器件都以计算清楚其坐标再进行放置的话会非常繁琐,那么我们有什么好的办法没有呢,Altium提供了一个非常简单的解决方案—极坐标

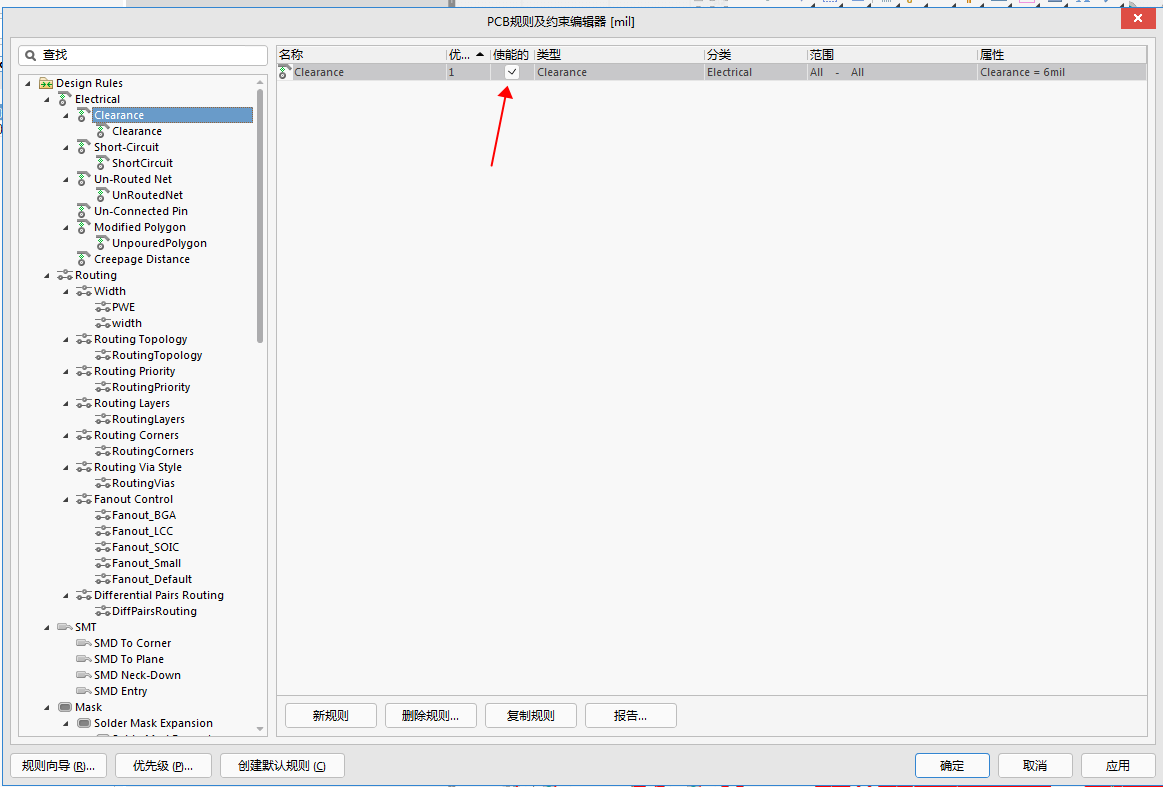

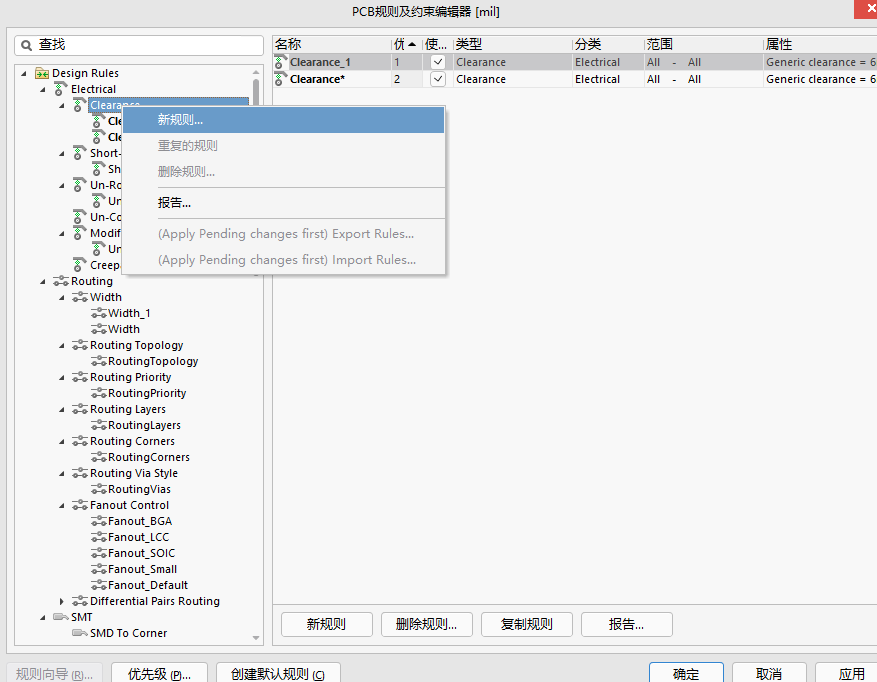

我们在根据PCB板的要求,在规则编辑器里面加入了很多对应的规则。比如:间距规则,线宽规则,短路等都是非常重要的电气规则规则,及其重要性是非常重要。

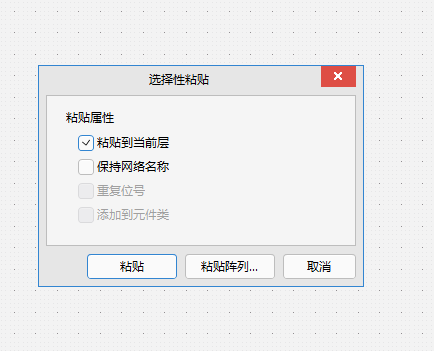

怎么样等间距的复制很多过孔?怎么带网络的复制走线?又或者是怎么样把元件的位号及网络从当前的这个PCB调用到另一个PCB板中呢?PCB设计当中经常会遇到这些问题,可以使用特殊粘贴也可以称为智能粘贴法来实现。

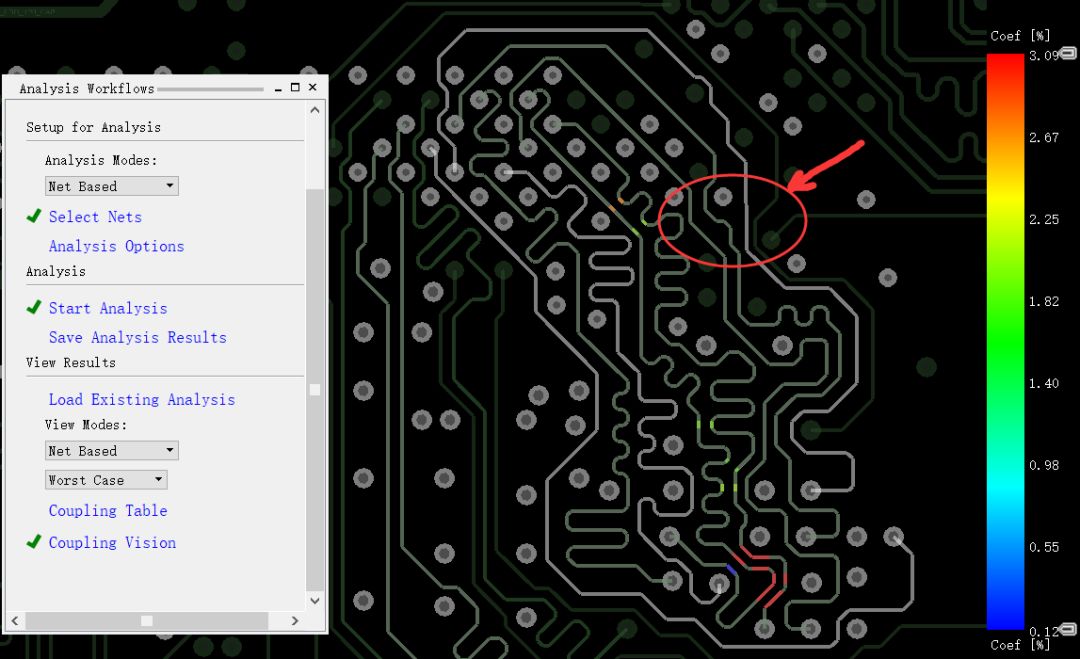

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

扫码关注

扫码关注