- 全部

- 默认排序

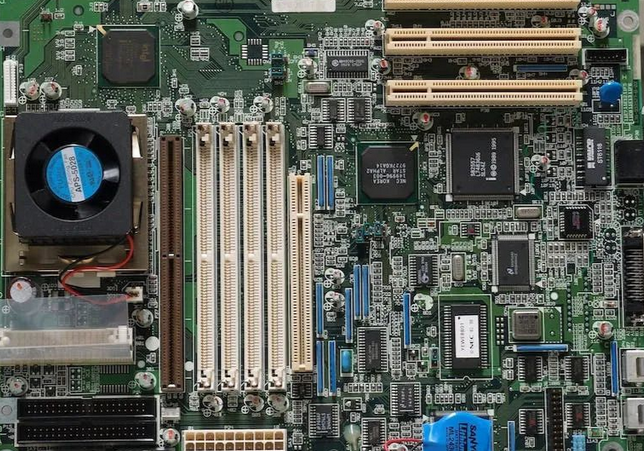

提起差分信号,很多电子工程师都不会陌生,得益于高速数字信号传输中的广泛应用,差分信号的走线在PCB设计中具有重要地位,为了确保差分信号的完整性,工程师需要遵循一些特定的规则,身为工程师的你知道有哪些规则吗?1、相对路径长度匹配差分信号对的两

1,strlen函数作用: 用于计算以空字符'\0'结尾的字符串的长度,即字符串中的字符个数,不包括空字符本身。返回值:strlen返回一个size_t类型的值,表示字符串中字符的数量。注意事项:strlen 需要在运行时遍历字符串,直到遇到空字符才停止计数。如果字符串没有以'\0' 结尾,strl

上次我们对不加端接电阻和加端接电阻之后的仿真结果做了分析之后我们得出在DDR采用菊花链拓扑结构的时候是需要加端接电阻的,这次我们看看DDR末端的端接电阻距离最后一片DDR远一点效果好一些还是近一点效果好一些。本次采用的案例依旧是我们上期的D

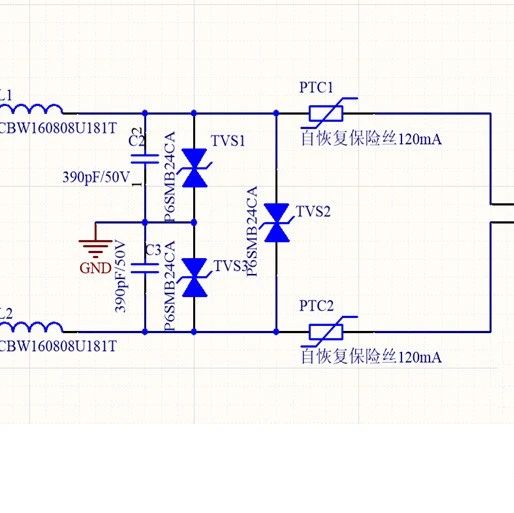

RS485电路原理图设计

RS485是差分信号,半双工、平衡传输线多点通信的标准,两个设备之间使用双绞屏蔽线缆连接,两个线缆分别传输A和B信号。RS485的传输速率与总线长度相关,最高可以达到10Mb/s,线缆越长,速率越慢;线缆越短,速率越快;RS485总线具有两种逻辑电平:高电平(1)和低电平(0)高电平(1):B线上的

PCB设计,细节要牢记,技巧规范,别忘记。元件选择,要慎重权衡,性能优化,细节考虑。电路布局,尺寸精确,差分信号,清晰准确。地平面铺,阻抗匹配,多层堆叠,功耗降低。信号路径,长度平等,串扰减小,信噪比增。参考设计,莫忽略,静电防护,接地要密

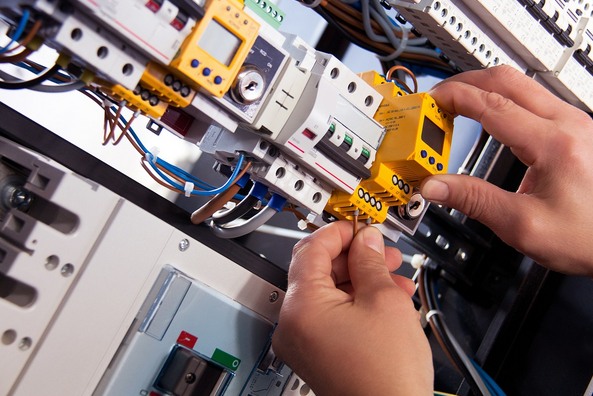

电子人都知道,电子产品的设计必须遵循抗静电放电(ESD)设计规则,以此让设备处在最佳运行状态,竞争力最大化。如果是电子机箱,该如何设计,才能达到抗ESD的目的?1、确保电子设备与下列各项之间的路径长度超过20 mm。包括接缝、通风口和安装孔

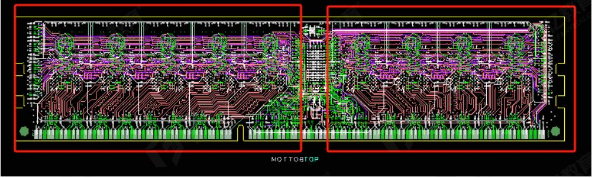

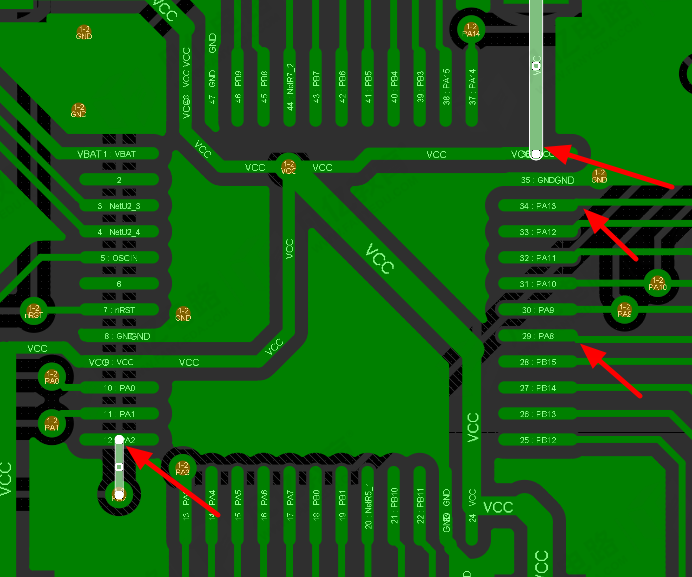

多个过孔没有网络过孔全都要打到电路的最后一个器件后方差分对尽量单对包地打孔处理电源不要包地,不要做多余处理差分对内长度误差5mil,设置对内等长规则以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接

单对差分对包地50-100mil打孔差分信号走线换层在旁边打回流地过孔同层连接多余打孔多处飞线未连接差分对内长度误差5mil,设置对内等长规则以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码

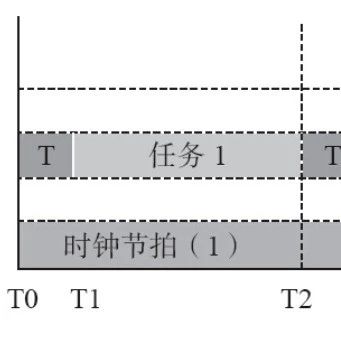

任务A和任务B按照等长时间轮流占用处理器,在单处理器上造成多个任务同时运行的假象。这里先聊一聊多任务系统架构的分割时间段。将处理器运行时间分成小的时间段指明了把处理器时间以多大的频率分割成固定长度的时间片段,也叫做多任务系统架构的时钟节拍。作为多任务系统运行的时间尺度,时钟节拍是通过特定的硬件定时器

焊盘从短方向出线,不要从长方向和四角出线,从焊盘中心出焊盘后拐弯主电源输出打孔要在模块最后一个电容后方,多打孔加大载流 SD走线保持3w间距整组打孔包地usb差分对经过电阻后而然是差分对,按照差分布线尽量耦合减短换层走线长度,换层打孔旁边打

扫码关注

扫码关注