- 全部

- 默认排序

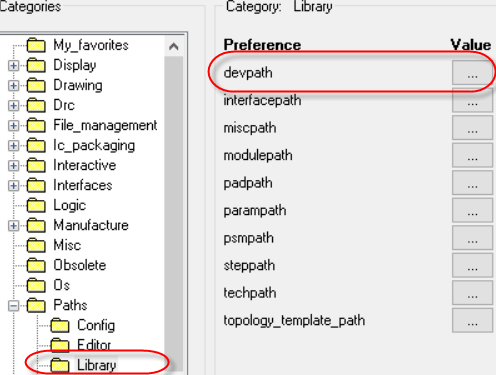

答:导网表时,常会用到第三方网表(用Other方式导出的网表)导入到PCB中,导入时常会发生找不到device的报错,具体报错内容可查看以下内容,如图4-97所示: 图4-97 错误提示示意图根据4-97所示,我们可以分析得出以下几个结论:Ø 导网表时,器件C1的封装报错。Ø 导网表时找不到封装名为SMD_0603的device文件。可以按照以下几个步骤来解决此问题:第一步,查看device路径是否设置正确。在命令Setup-UserPreference

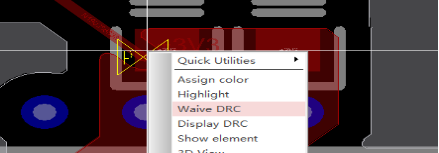

答:对于PCB上某些DRC,是可以忽略,可以通过Waive DRC将此DRC隐藏。第一步,在Find选项卡中勾选DRC errors;第二步,然后将光标移动到DRC附近,右击选择Waive DRC,如图5-202所示;

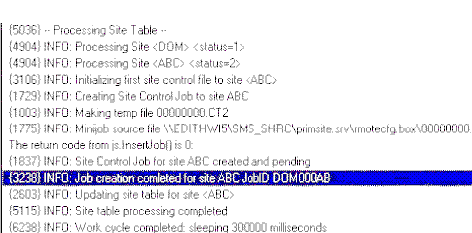

答:这里说的DB功能,指的就是DB Doctor功能。其作用就是对Allegro软件出现的一些无法解释的错误、bug、异常关闭软件导致的工作不正常等情况进行修复,使Allegro软件能够正常运行。其使用DB功能的操作步骤具体如下所示:

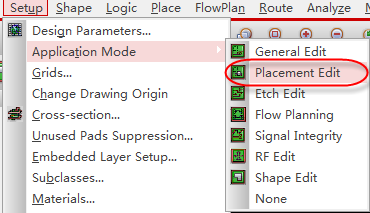

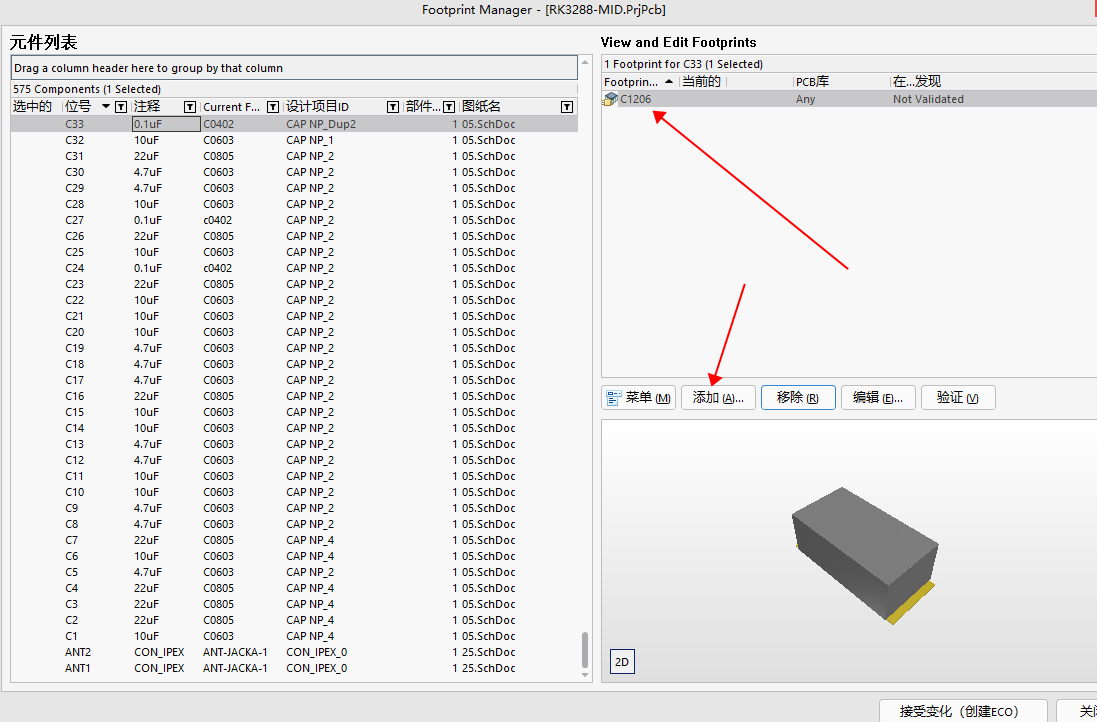

答:在前面的问题中,我们讲述了对同一种类型的元器件进行封装的更新,有时候会出现这样的情况,出现错误的操作,误删除的其中一个器件的丝印或者是什么的,能否只更新这一个器件呢,其它的不进行更新,当然是可以的,具体的操作步骤如下所示:

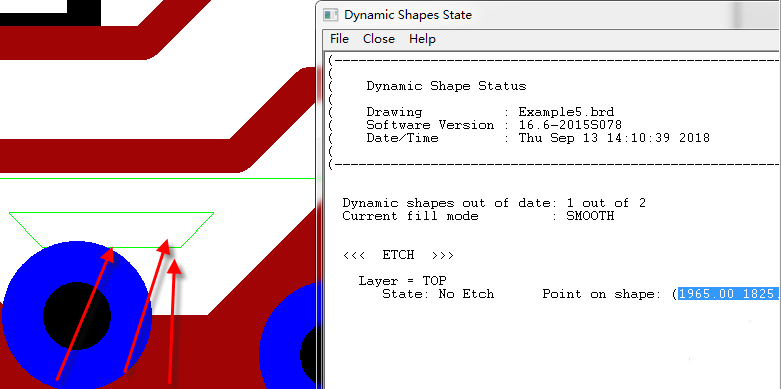

答:我们在设计完成之后,需要对所有的铜皮进行smooth处理,在进行smooth处理的时候,有时因为铺铜的错误操作,出现有一块或者几块铜皮不能更新,出现Out of data shape的问题,如图6-188所示,

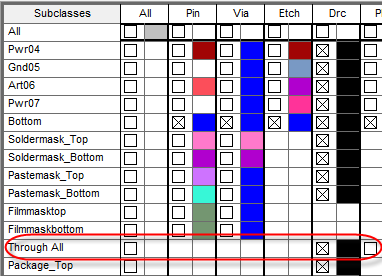

答:我们在PCB设计完成之后,都需要对整板铺地铜处理,然后在铺的地铜上面放置地过孔,但是有这样一个现象,相同的地过孔放重叠了,并不会产生DRC错误,我们应该如何设置,才可以让相同网络的重叠过孔产生DRC错误呢,这里讲解一下,具体操作如下所示:

答:原理图检查,检查是否有单端网络、连接错误、没有指定封装等设计问题→原理图输出网表以及网表检查→检查封装库,没有封装库的,匹配原理图

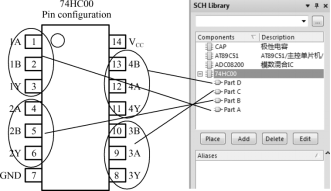

答:当一个元件封装包含多个相对独立的功能部分(部件)时,可以使用子件。原则上,任何一个元件都可以被任意地划分为多个part(子件),这在电气意义上没有错误,在原理图的设计上增强了可读性和绘制方便性。

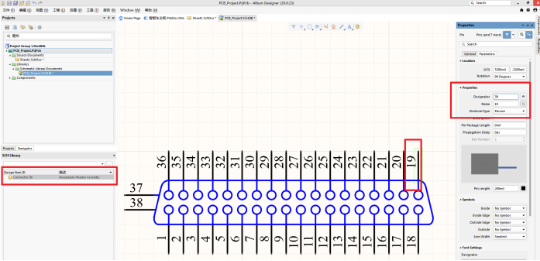

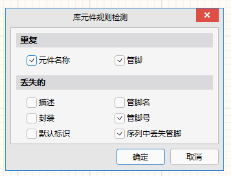

答:在绘制原理图的时候,有时出现绘制错误时。无需在原理图里面删除之后重新放置,可以在库中把修改好的器件直接更新进去既可,这样可以省去很多的设计时间,下面以一个例子进行说明:

扫码关注

扫码关注