- 全部

- 默认排序

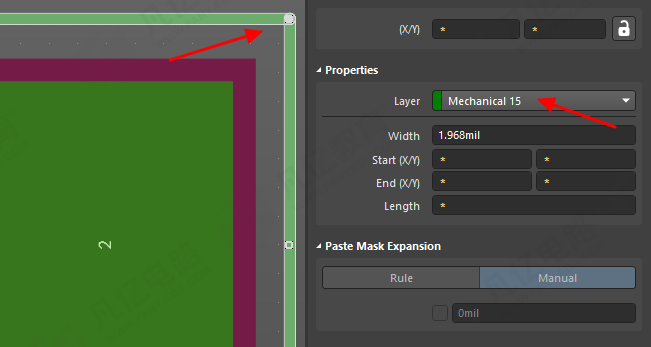

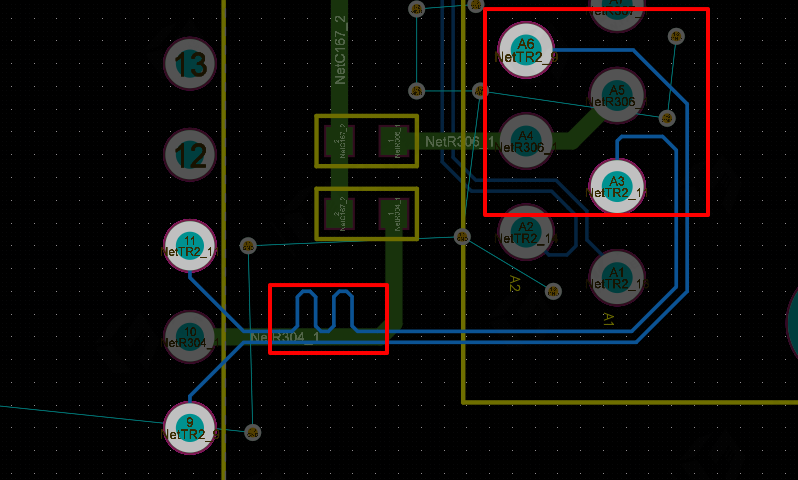

1.封装丝印层错误,Top Overlay是丝印层2.0805封装焊盘横向太宽补偿错误,焊盘间距太近3.sop8封装外侧没画一脚标识,器件焊接后将看不到一脚标识,丝印上焊盘4.sop8封装焊盘太短,焊盘补偿错误以上评审报告来源于凡亿教育90

在电子的设计制造中,PCB设计是至关重要的环节,尽管PCB设计的重要性得到了广泛认可,但依然有很多工程师在实践中犯下各种错误,本文凡小亿将盘点一些你没发现过的PCB设计错误,希望对小伙伴们有所帮助。1、散热走线未能正确连接到覆铜或平面;2、

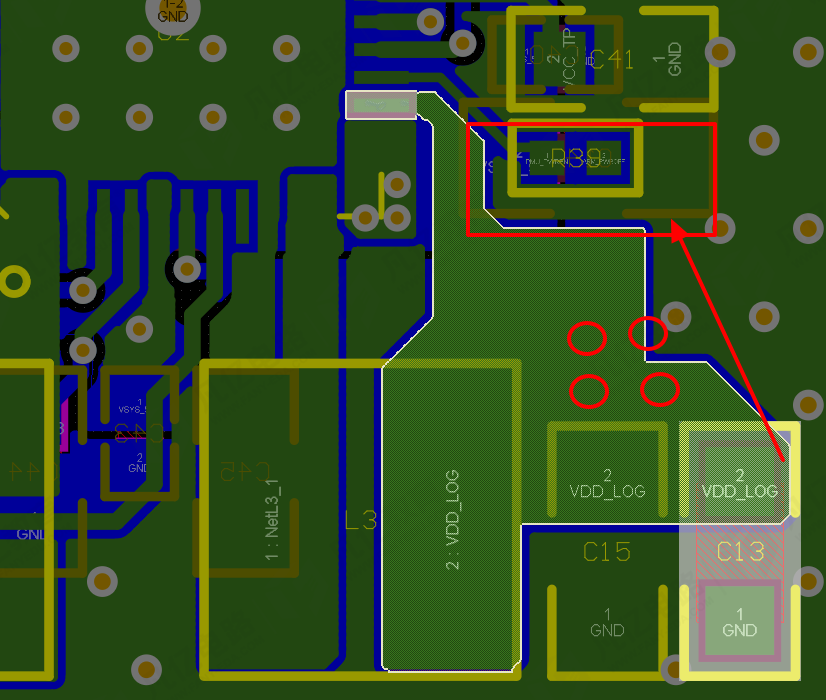

电容布局布线错误,此脚是反馈信号,电容应靠近管脚放置电源输出端打孔多处电源走线需要加粗走线不能从同层器件下穿过以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://ite

焊盘出线错误,应从焊盘短边出线平常铺铜和走线都要45度或90度,不要任意角度铺铜过孔不要碰到焊盘,过孔到焊盘保持一定间距铜皮尽量避开电感器件下方以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫

晶振布局布线错误,应包地打孔走类差分形式变压器出差分线外所有线加粗到20mil以上差分走线不耦合变压器下方所有层挖空铺铜器件布局太近丝印干涉走线不要锐角布线不能从同层器件下方穿过布线尽量短不要绕线布线保持3w间距要求以上评审报告来源于凡亿教

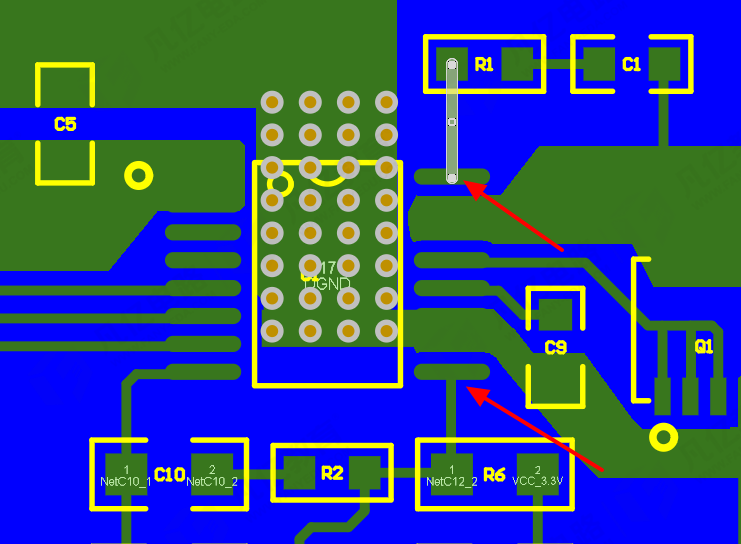

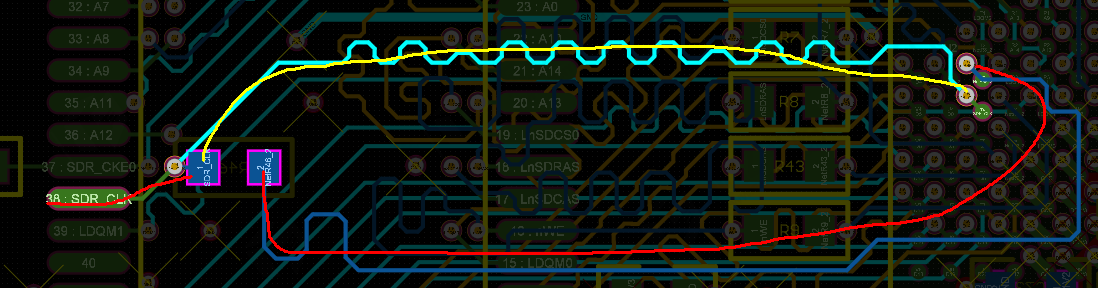

差分等长错误:1.尽量在引起不等长端绕线 2.差分对内等长绕线高度和间距不规范地址线要单根包地打孔处理tx、rx分别建立等长组等长,两组走线之间保持4w间距,有空间单组包地或两组包地以上评审报告

这对信号也是差分对,要差分布线器件尽量靠近管脚放置,要在电容旁边打孔器件中心对齐,相邻器件尽量朝一个方向放置差分对内等长错误差分尽量靠近引起不等长端进行绕线差分包地有空间尽量包完整走线尽量不要绕线,差分线两根尽量一样长不同网络走线用同一个过

1、什么是busoff?BUSOFF,从字面意思可以看出,表示总线的关闭,此时ECU从总线脱离,既不能接收总线的报文,也不能向总线发送报文。 2、BUSOFF是如何产生的?CAN总线上存在多种错误状态,包括:位错误(Bit Check Error)、位填充错误(Bit Stuff Error)、C

时钟信号等长错误地址线等长组有几个信号等长不到目标长度,电阻到芯片段加入一起等长应避免走线造成信号回路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.ta

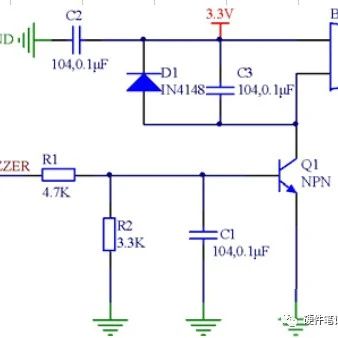

蜂鸣器驱动电路设计

下面就 3.3V NPN 三极管驱动有源蜂鸣器设计,从实际产品中分析电路设计存在的问题,提出电路的改进方案,使读者能从小小的蜂鸣器电路中学会分析和改进电路的方法,从而设计出更优秀的产品,达到抛砖引玉的效果。常见错误接法上图为典型的错误接法,当 BUZZER 端输入高电平时蜂鸣器不响或响声太小。当 I

扫码关注

扫码关注