- 全部

- 默认排序

数字电路中的逻辑电路

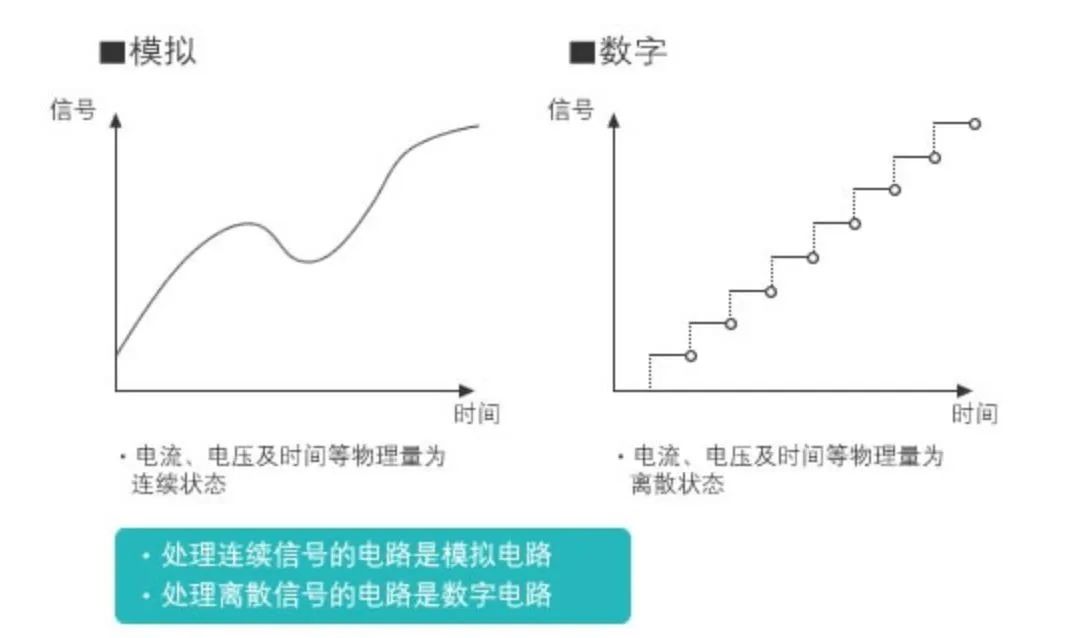

为了将自然界的模拟信息输入到象计算机那样的数字电路,需要将信息数字化(模拟信号→数字信号)。进行"模拟信号→数字信号"转换的是A/D转换器,A/D转换器按时间有规律地读取(采样)输入信号,并将其转换成用"0"和"1"表现的数值(2进制)。而整数只能表示直线上的特定点,就象是数字。于是,我们把处理连续信息的 —— 模拟信号的电路称作"模拟电路",把处理离散信息 —— 数字信号的电路称作"数字电路"。

二、模拟电路与数字电路之间的区别模拟电路是处理模拟信号的电路;数字电路是处理数字信号的电路。模拟信号是关于时间的函数,是一个连续变化的量,数字信号则是离散的量。因为所有的电子系统都是要以具体的电子器件,电子线路为载体的,在一个信号处理中,信号的采集,信号的恢复都是模拟信号,只有中间部分信号的处理是数字处理。具体的说模拟电路主要处理模拟信号,不随时间变化,时间域和值域上均连续的信号,如语音信号。而数字信号则相反,是变化的,数字信号的处理包括信号的采样,信号的量化,信号的编码。

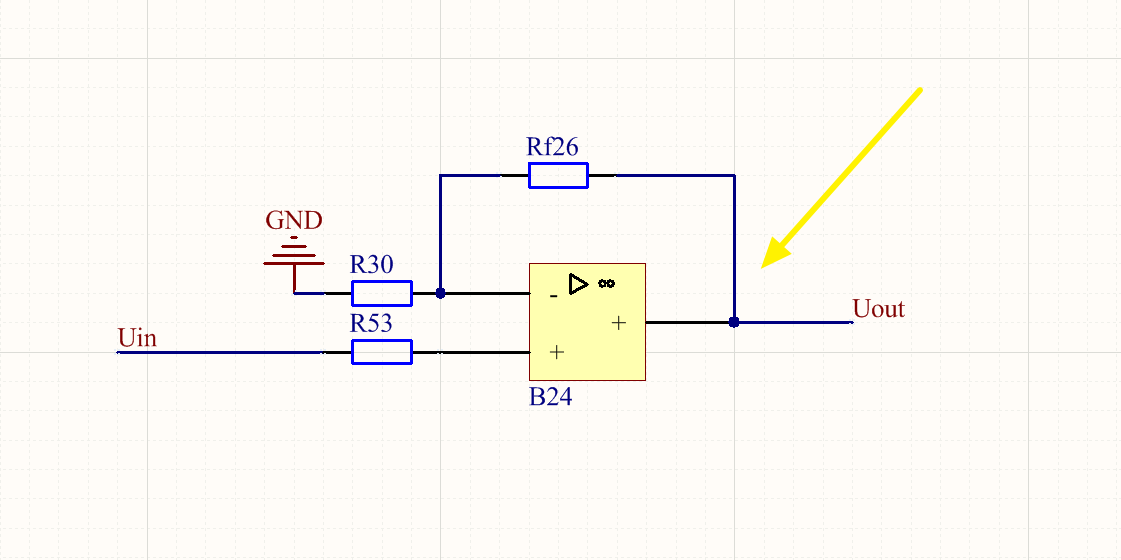

电流电压反馈如何判断

电压反馈从放大器输出端取出输出信号的电压,目的稳定输出信号的电压 电压反馈判定:输出信号撤销,反馈没有信号,采样点和输出端是否是在一个点,如果是一个点,属于电压反馈,并联电路输出端。

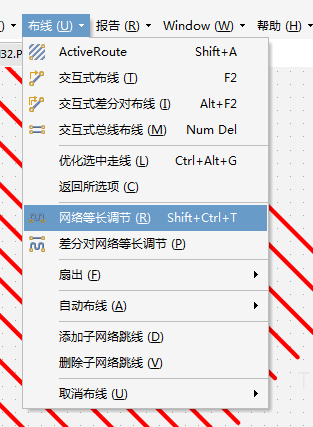

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

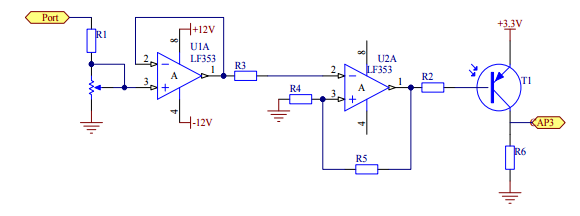

1.开关电源概述 开关电源的基本构成如下图所示,其中DC-DC变换器用于进行功率转换,他是开关电源的核心部分,此外还有启动、过流和过压保护、噪声滤波等电路。输出采样电路(R1、R2)检测输出电压的变化,并与基准电压Ur比较,误差电压经过放大及脉宽调制电路(PWM),在经过驱动电路控制功率器件的占空比,从而达到调整输出电压大小的目的。 2.开关电源设计要点 1) 第一时间下载主芯片的datasheet,按照推荐的布局布线来进行操作(以TPS55540为例)

利用CS5463芯片可调整温度漂移误差个提高测量精度-CS5463的内部结构框图如图1所示,它由2个可编程增益放大器、2个△-∑调制器、配套的高速滤波器、功率计算引擎、偏置和增益校正、功率监测、串行接口及相应功能寄存器等组成。2个可编程放大器采集电压和电流数据,△-∑调制器对模拟量采样处理,高速数字低通或可选的高通滤波器滤取可用电压电流数字信号,功率计算引擎计算各类型的功率,电压、电流,并将计算的功率值通过串行接口对外输出,既可以接EEPROM,也可以接微控制器。该电路还有能量脉冲信号输出模块,

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

扫码关注

扫码关注