- 全部

- 默认排序

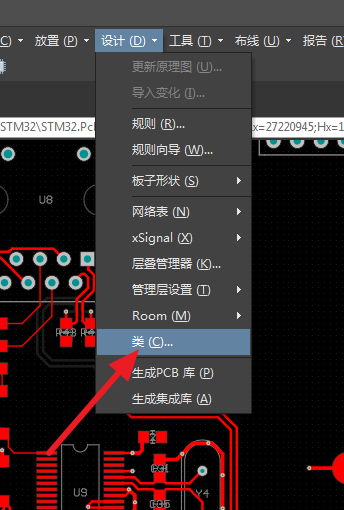

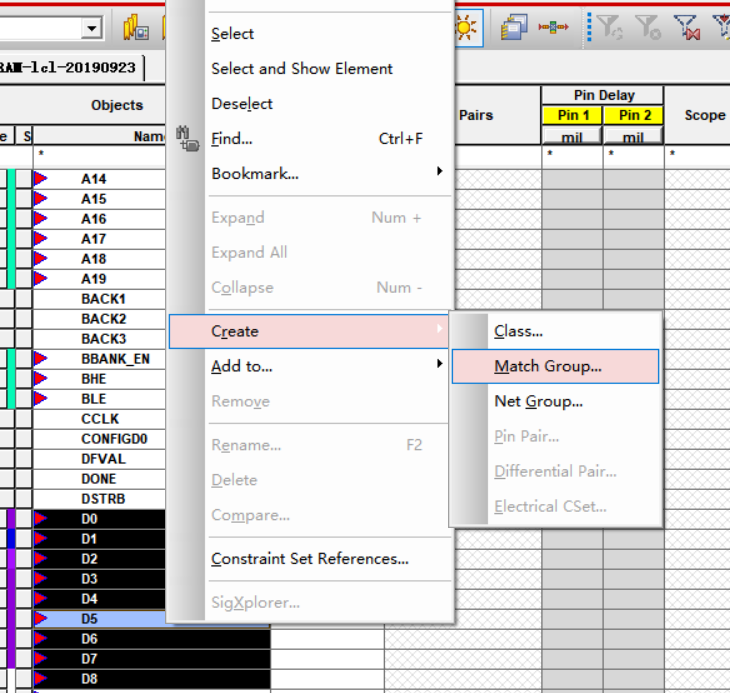

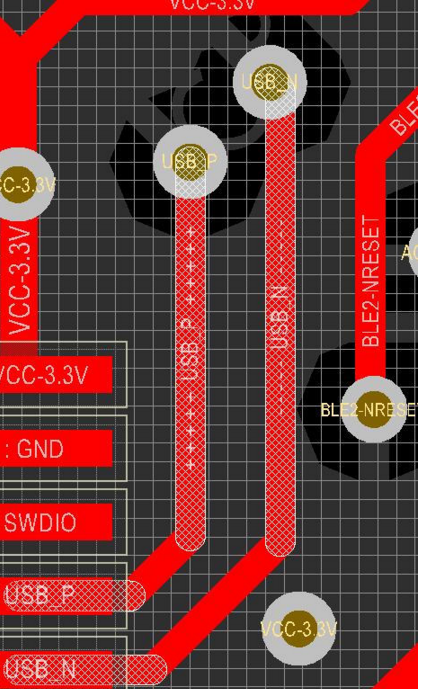

我们在进行PCB设计的时候,一个PCB板上的信号线,电源线,地线等等太多了。那我们给它分成一类一类的,就是我们常说的在Class中创建的类了。

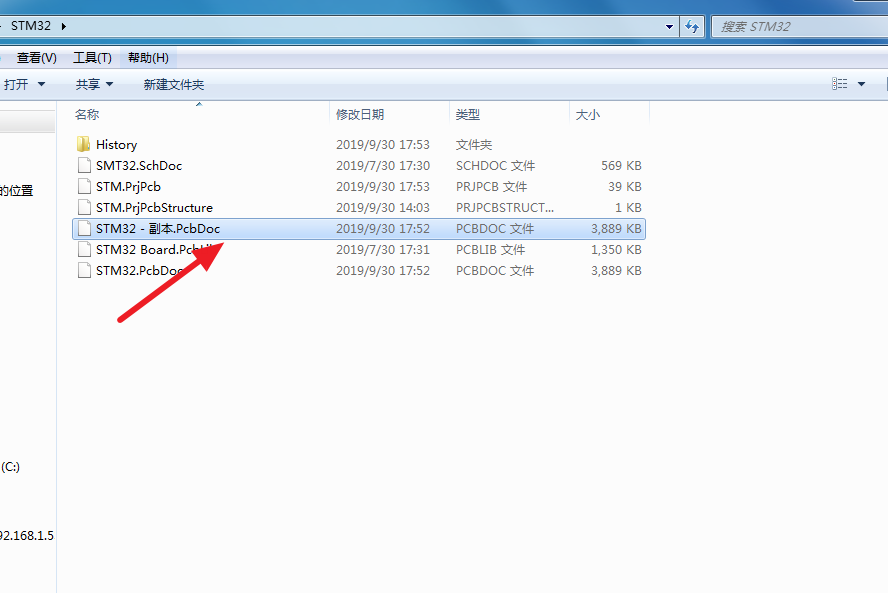

我们在进行PCB设计时,在连线走线的时候,会经常出现这么两种情况:1.走线连接到焊盘上时,我们以为自己已经连接到了焊盘中心点上,早已连接上了,其实没有。那么,这个对于我们后期会造成虚焊,而且这一项有时DRC也检查不出来。所有为了减少我们不必要的损失,就来讲一下这项常用的方法。2.走线跟走线连接的时候,以为是连接上了,其实也是没有连接上来,会有开路的现象。

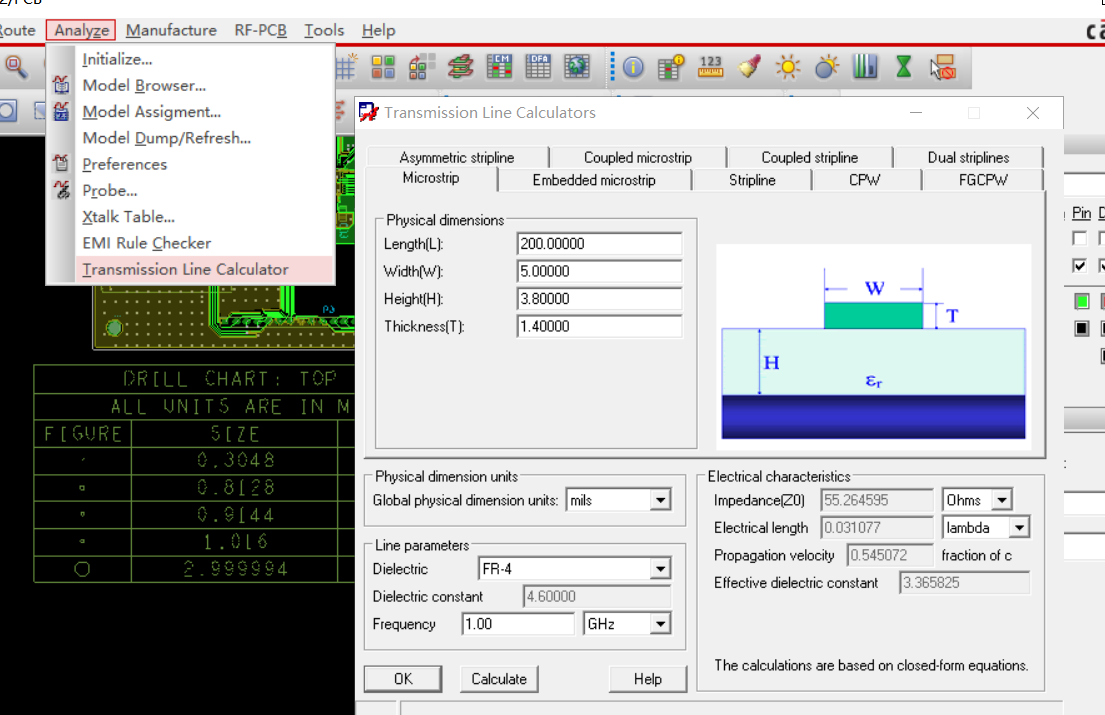

随着信号速率越来越高,PCB设计时,越来越多的数字电路 需要对走线阻抗控制、延迟等传输参数进行计算。Allegro16.6版本提供了一个内置的传输线参数计算工具,能对微带线、嵌入式微带线、带状线、差分线等多种传输数据结构进行传输参数计算。

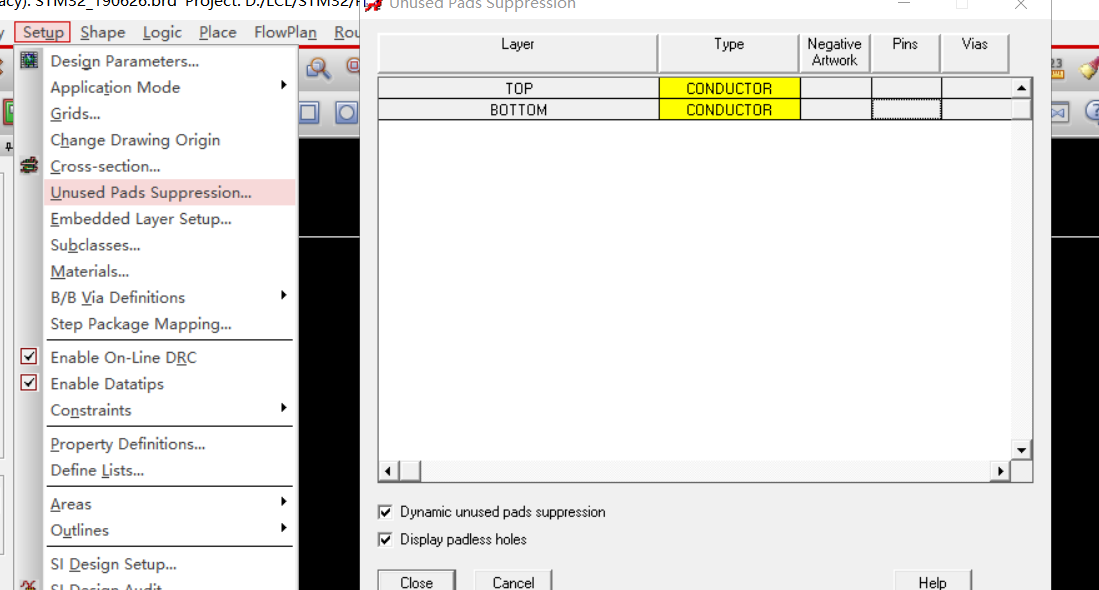

走线过孔与元器件通孔在内层的焊盘具有寄生电容的效应,易造成阻抗不连续,导致信号反射,从而影响信号完整性,allegro提供简单快捷的误判设计功能,可在设计端就将无走线连接层的焊盘去除,最大限度地保证过孔或通孔处与走线阻抗一致。

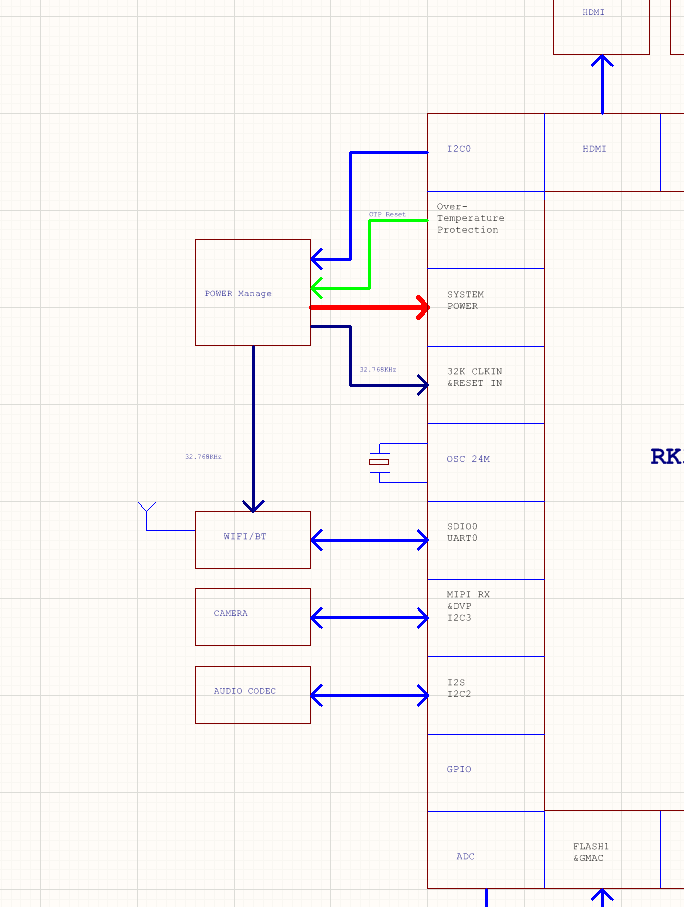

SDRAM信号线等长处理

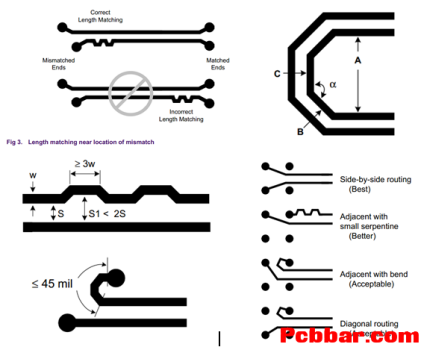

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

扫码关注

扫码关注