- 全部

- 默认排序

随着时代发展,Mentor Pads很快成为国内半导体公司的常用EDA软件之一,也就是说起码有数万个电子工程师在使用Pads设计PCB,当然也有很多工程师在使用Pads时遇到了很多问题,下面来看看有哪些技术问题仍然还在继续犯?1、走线细或设

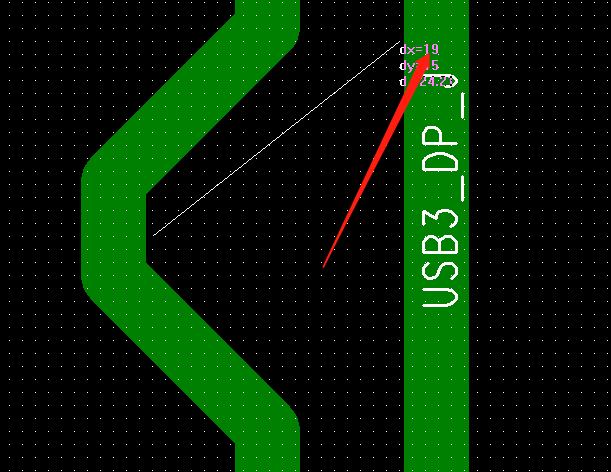

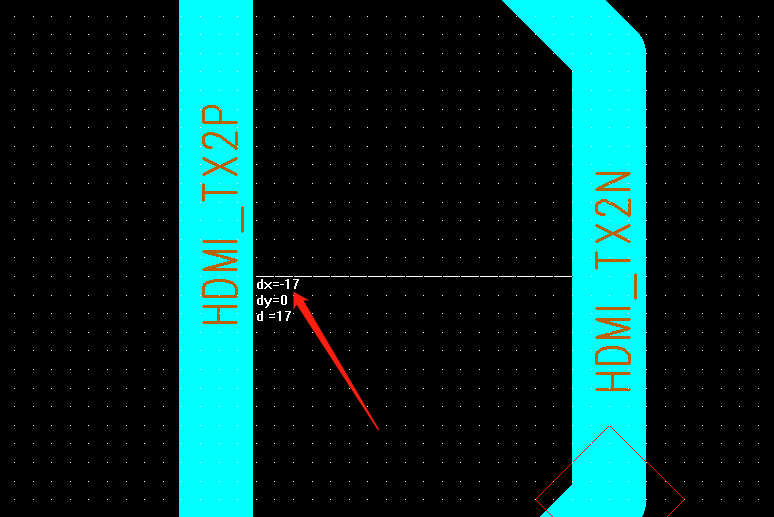

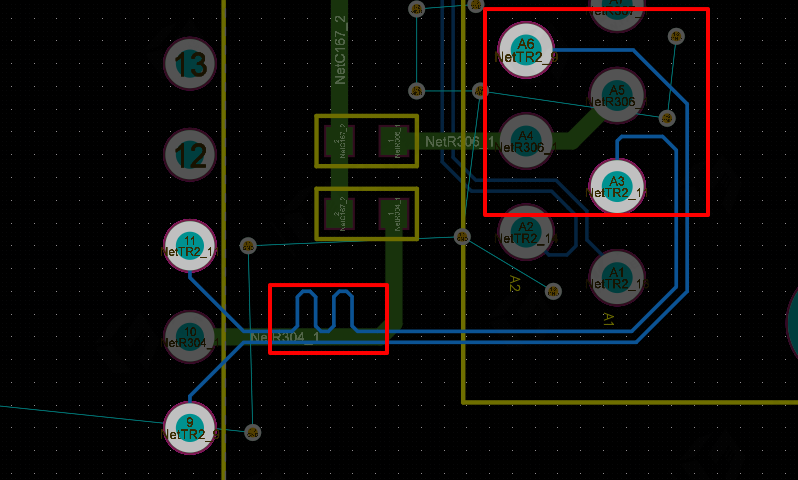

1注意差分对内等长凸起高度不能超过线距的两倍2.差分出线要尽量耦合,后期自己调整一下3.此处线宽不满足载流,后期自己加粗一下线宽或者铺铜处理4.CC1和CC2属于重要信号,走线需要加粗处理5.ESD器件要靠近关键摆放,先经ESD器件在到座子

在很多厂商的PCB Layout指导手册里,总是会注明:高速信号的走线拐角角度最好不要直角90°,尽量45°走线,甚至有的厂商还会说走圆弧比45度拐角更好,事实上是不是这样?PCB走线角度该如何设置?1、90°走线角度很多电子工程师经常在P

跨接器件旁边要尽量多打地过孔,间距要保证2mm,有器件的地方可以不满足2.此处差分出线需要再优化一下,尽量从差分4个角出线3.此处需要确认一下是否满足载流,后期自己加粗一下线宽4.晶振下面尽量不要走线和放置器件,包地处理5.电源走线需要加粗

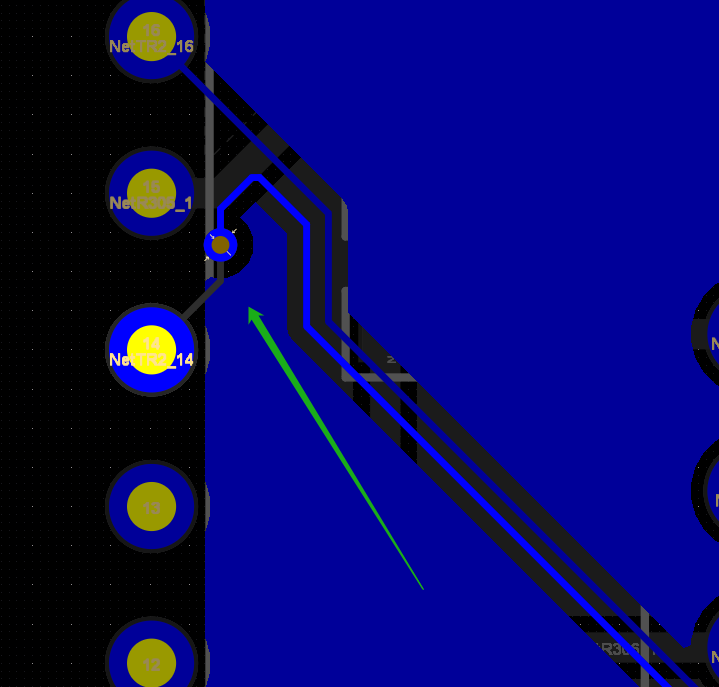

差分线对内等长凸起高度不能超过线距的两倍2.差分对内绕等长绕一边即可3.走线需要优化一下,尽量不要走任意角度4.差分出线需要优化一下5.存在开路6.地网络尽量就近打孔连接到地平面走线尽量不要超过器件外框丝印,走线离焊盘太近,后期容易短路差分

差分等长错误:1.尽量在引起不等长端绕线 2.差分对内等长绕线高度和间距不规范地址线要单根包地打孔处理tx、rx分别建立等长组等长,两组走线之间保持4w间距,有空间单组包地或两组包地以上评审报告

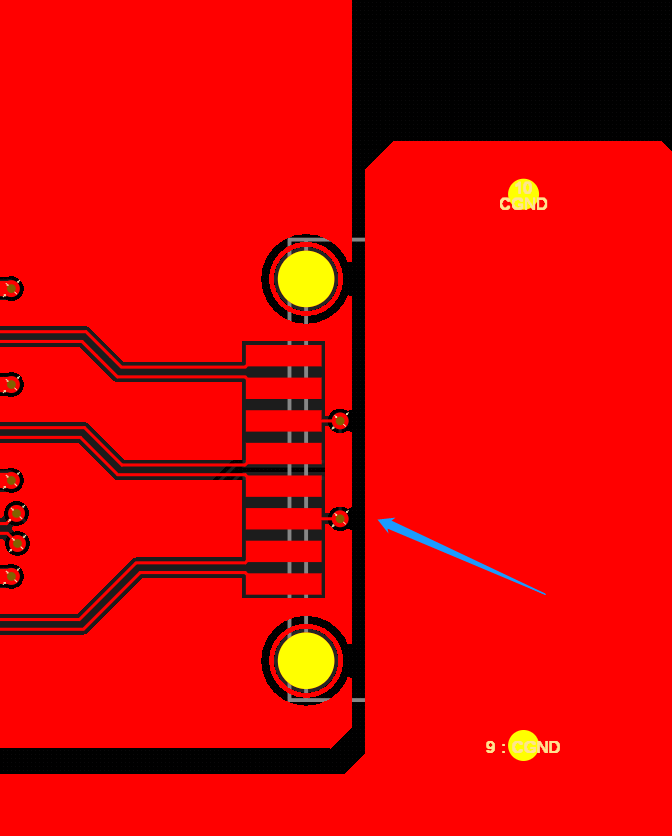

此处差分连接的变压器焊盘是通孔焊盘,不用扇孔可以直接连接:变压器上除了差分其他的信号加粗20MIL:差分打孔换层的两侧需要就近放置地过孔:差分需要耦合走线,删除重新走下:差分信号对内等长5MIL:注意等长,gap可以大一点 不用那么高:以上

机壳地与电路地之间至少满足2MM间距:GND铜皮跟GND焊盘并未连接:需要设置铜皮属性之后再去重新灌铜:跨接器件两边的地可以多放置地过孔:晶振底部不要走线:TX RX直接用GND走线隔开:信号线不要从电阻电容内部走线,更改下路径:以上评审报

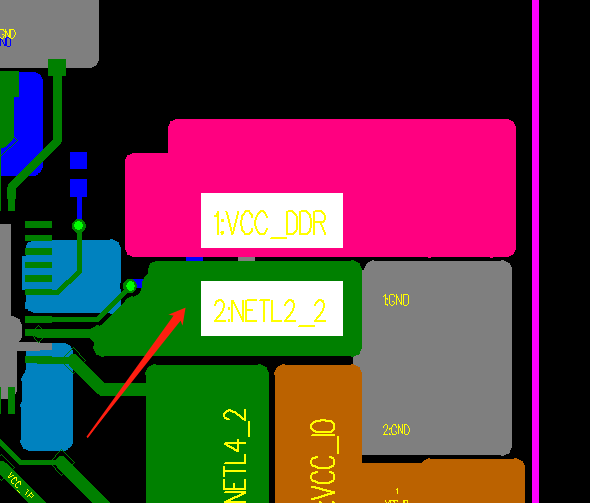

电感底部不要放置器件:可以吧电阻电容放置到中间IC的底部。电感内部也需要挖空处理:DCDC电源主干道建议铺铜处理满足其载流大小:LDO 电路部门扇孔注意过孔对齐:走线不要直角:LDO电源信号尽量拉出焊盘就加粗,不要拉出很多之后再去加粗:以

地信号跨接处多打过孔电源走线注意加宽走线 tx、rx两组线分开布线,不要混合布线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/it

扫码关注

扫码关注