- 全部

- 默认排序

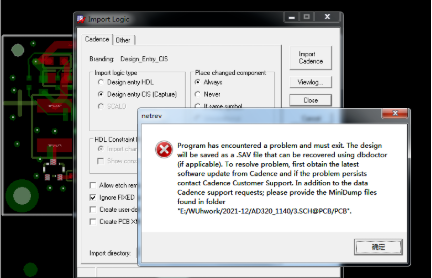

Allegro在导入网表文件时或者运行软件的时候出现如下截图报错,很多网友找不到解决方法,其实是可以根据下面俩种方法去解决这个问题的。第一种解决办法:1、当在设计过程中出现这个问题或者是在刚打开这个某一些文件出现这个问题的时候,可以点击菜单

Pads Router组件的操作界面主要由标题栏、菜单栏、快捷工具区域、主要设计工作区域输出窗口这几部分组成。如下图6-1示:图6-1 PADS Router组件操作界面6.1.1 标题栏标题栏主要记录了文件的保存路径、文件的名称。如图6-

和Pads Layout组件类似,PADS Router组件使用前,可执行菜单“工具-选项”,进行默认选项参数设置,常用设计选项包括全局、颜色、显示、布局、正在填充、文本和线、布线、测试点、制造、设计验证等。如图6-6所示。部分设置选项是与

PADS布线与修线操作

布线前须将规则设置好,一般在Layout内添加规则及层叠,注意将布线层选。在Router组件执行菜单命令“工具-选项”,在“选项”对话框“布线”标签页进行参数设置。注意选择好“布线角度”、“交互式布线”等参数,层对设置顶底层,一般不建议打开

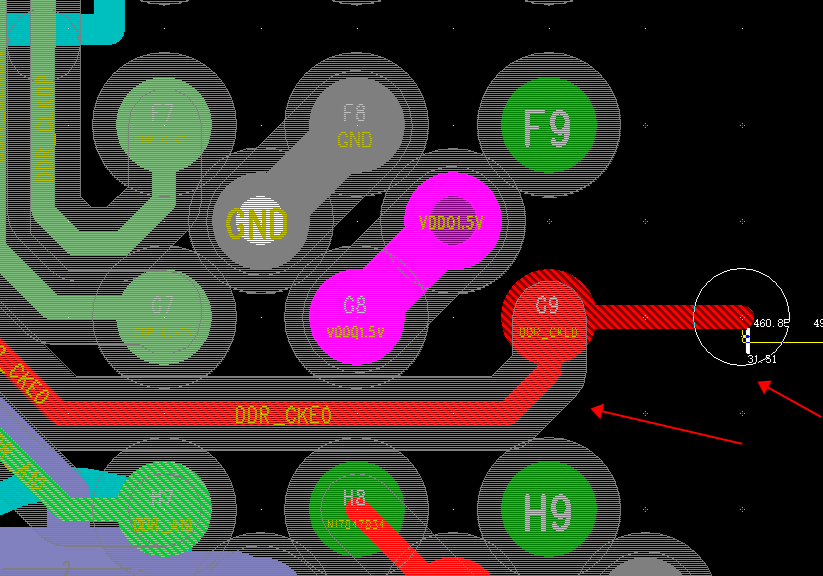

在PCB设计的时候,常常为了设计方便,会对某些特殊的网络或者某一网络类进行颜色的分配,具体步骤如下:1)给某一单独的网络进行颜色的分配执行菜单命令Display-Assign Color,在Find面板上勾选网络,在Options面板中选择

在DDR的设计中,需要对数据线及地址线进行分组及等长来满足时序匹配,通常DDR的数据线之间的长度误差需要保证在50mil以内,地址线的长度误差需要保证在100mil以内。执行菜单命令【设计】-【规则】或者使用快捷键DR打开规则约束器,在“H

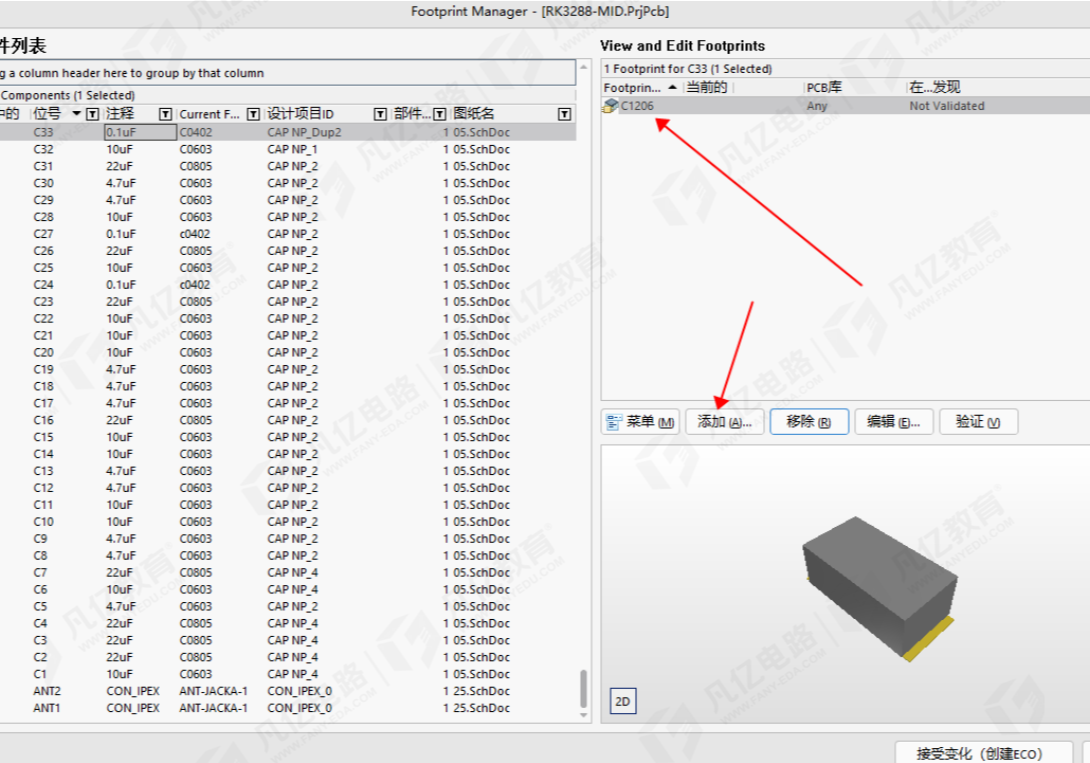

Altium Designer原理图中器件与PCB板图中的器件是怎么关联的?答:原理图绘制完成以后,需要将原理图的元器件与PCB版图中的器件关联起来,这样就需要指定对其指定PCB封装。在原理图界面执行菜单命令【工具】-【封装管理器】,通过“

1、系统默认的快捷键Altium Designer自带很多组合快捷键,可以多次执行字母按键组合成需要的操作,很是方便。那么组合快捷键如何得来呢?其实,系统的组合快捷键都是依据菜单中命令的下画线字母组合起来的。如图1所示,对于“放置(P)-线

第一步,在Logic界面中,执行菜单命令“工具-选项”,如图1所示。第二步,弹出的“选项”对话框中,点击“设计”分栏,如图2所示。对应设计分栏的对话框中找到“图页”设置界面,在其“图页边界线”选项旁点击“选择”选项,如图3所示。图1“选项”

第一步,执行菜单命令“工具-选项”,如图1所示。第二步,弹出的“选项”对话框中,点击左分栏中“常规”选项,如图2所示。在展开的常规界面中,找到“光标”设置,点击样式中的下滑栏存在以下选项,如图4所示,按照自己的设计进行勾选。如果设计存在需要

扫码关注

扫码关注