- 全部

- 默认排序

利用CS5463芯片可调整温度漂移误差个提高测量精度-CS5463的内部结构框图如图1所示,它由2个可编程增益放大器、2个△-∑调制器、配套的高速滤波器、功率计算引擎、偏置和增益校正、功率监测、串行接口及相应功能寄存器等组成。2个可编程放大器采集电压和电流数据,△-∑调制器对模拟量采样处理,高速数字低通或可选的高通滤波器滤取可用电压电流数字信号,功率计算引擎计算各类型的功率,电压、电流,并将计算的功率值通过串行接口对外输出,既可以接EEPROM,也可以接微控制器。该电路还有能量脉冲信号输出模块,

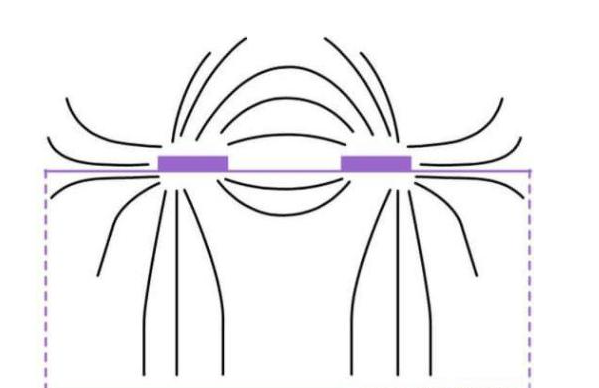

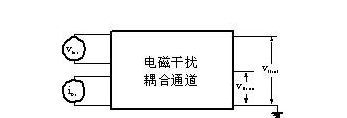

答:串扰,就是指一条线上的能量耦合到其他传输线,它是由不同结构引起的电磁场在同一区域里的相互作用而产生的。串扰在数字电路中非常普遍地存在着,如芯片内部、PCB板、接插件、芯片封装,以及通信电缆等等。 串扰可能是数据进行高速传输中最重要的一个影响因素了。它是一个信号对另外一个信号耦合所产生的一种不受欢迎的能量值。根据麦克斯韦定律,只要有电流的存在,就会有磁场存在,磁场之间的干扰就是串扰的来源。这个感应信号可能会导致数据传输的丢失和传输错误。 所以串扰对

答:上拉、下拉电阻的作用有如下几种:提高电压准位:当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V), 这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值;OC门电路必须加上拉电阻,以提高输出的搞电平值;加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻;N/A pin防静电、防干扰:在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗, 提供泄荷通路。同时管脚悬空就比较容易接受外界的电磁干

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

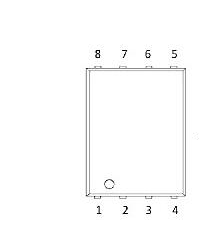

答:我们在创建多管脚的器件封装时,分Part的依据一般如下:查看改器件的Datasheet,根据芯片手册的分类来划分Part;把电源管脚与信号管脚分开;把功能一致的管脚分为一个Part;空管脚比较多的器件,把所有的空管脚分为一个Part。

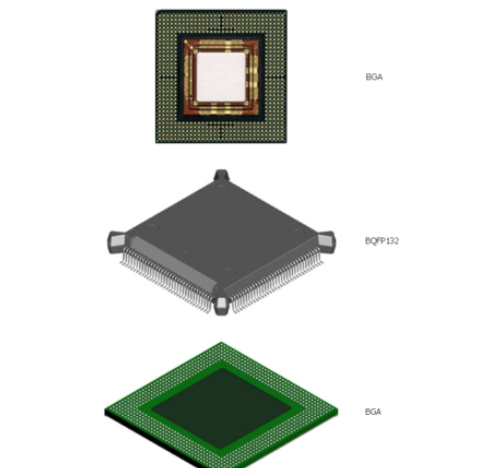

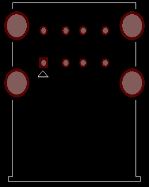

答:PCB封装就是把实际的电子元器件,芯片等的各种参数(比如元器件的大小,长宽,直插,贴片,焊盘的大小,管脚的长宽,管脚的间距等)用图形方式表现出来,以便可以在画pcb图时进行调用。1)PCB封装按照安装方式来区分的话,可以分为贴装器件、插装器件、混装器件(贴装和插装同时存在)、特殊器件。特殊器件一般指沉板器件。2)PCB封装按照功能以及器件外形来区分的话,可以分为以下种类:SMD: Surface Mount Devices/表面贴装元件。RA:

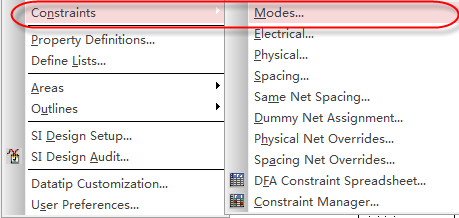

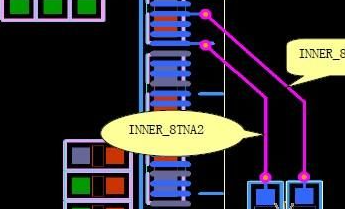

答:我们在时序等长时,除了考虑信号线的走线的长度以外,在高速设计领域里还需要考虑封装本身的引脚长度。所谓封装引脚长度,指的就是元器件封装内部的引脚长度,这个长度一般芯片的厂家会提供这数据,我们要做的就是将数据导入到规则管理器中,与等长一起处理,具体的操作步骤如下:

答:PCB符号,也叫PCB封装,就是把实际的电子元器件,芯片等的各种参数,比如元器件的大小、长宽、直插、贴片以及焊盘的大小,管脚的长宽、管脚的间距等用图形方式表现出来。

答:串扰,就是指一条线上的能量耦合到其他传输线,它是由不同结构引起的电磁场在同一区域里的相互作用而产生的。串扰在数字电路中非常普遍地存在着,如芯片内部、PCB板、接插件、芯片封装,以及通信电缆等等。

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

扫码关注

扫码关注