- 全部

- 默认排序

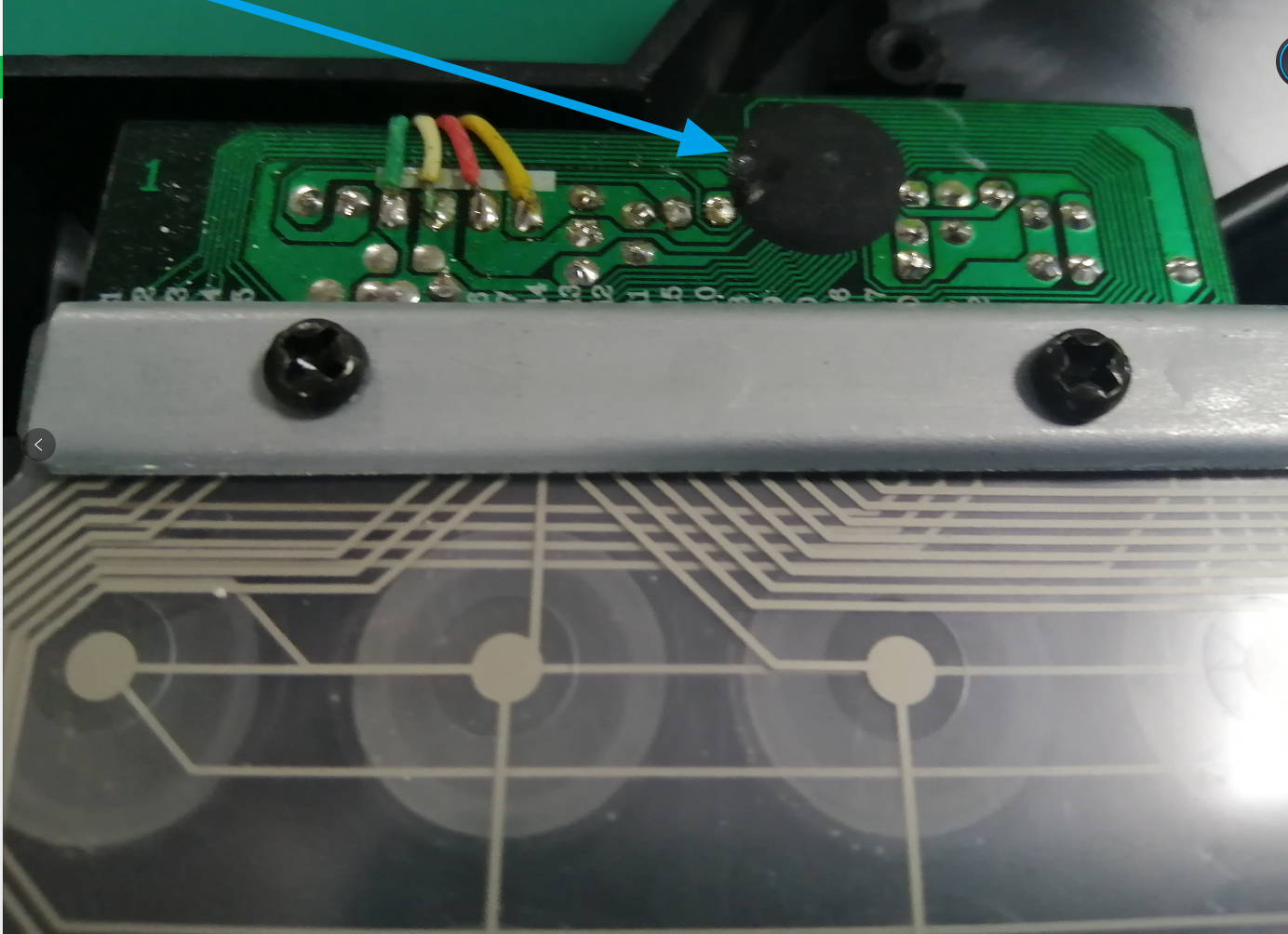

COB封装绑定IC

COB封装即chip On board,就是将裸芯片用导电或非导电胶粘附在互连基板上,然后进行引线键合实现其电气连接。如果裸芯片直接暴露在空气中,易受污染或人为损坏,影响或破坏芯片功能,于是就用胶把芯片和键合引线包封起来。人们也称这种封装形式为软包封。

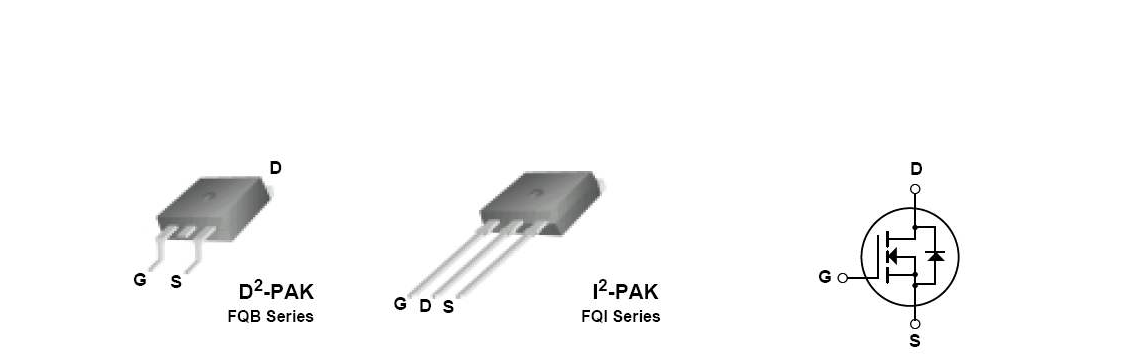

MOS管寄生电容

寄生电容是指电感,电阻,芯片引脚等在高频情况下表现出来的电容特性。实际上,一个电阻等效于一个电容,一个电感,一个电阻的串联,低频情况下表现不明显,而高频情况下,等效值会增大。在计算中我们要考虑进去。ESL就是等效电感,ESR就是等效电阻。不管是电阻,电容,电感,还是二极管,三极管,MOS管,还有IC,在高频情况下要考虑到等效电容值,电感值

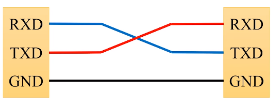

电脑串口与单片机可以直接相连吗?电脑的串行口RS232信号电平是(-10 ,+10v),单片机所用到的TTL信号电平是(0 ,+5v),很显然他们之间的电平没有统一标准,不能直连。

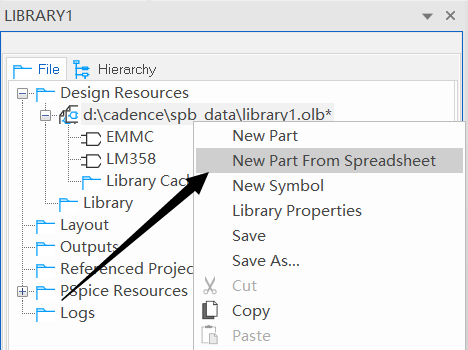

在我们遇到引脚数量特别多的芯片时,此前用的创建元件的方法会显得特别的麻烦,且费时费力,也会容易出现错误,这时我们可以通过Capture导入Excel表格的方式来方创建元件

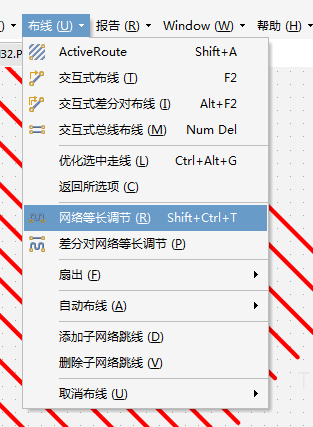

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

开关电源esd测试教程

1. 开关电源的几种保护OCP, OLP, OVP, OTP, ESD,UVLO分别是什么意逐周期电流限制保护(OCP),限制最大输出电流;过载保护(OLP),限制最大输出功率;VDD过压保护(OVP),限制最高输入电压;温度保护(OTP),限制工作时的最高温升;ESD静电保护,即静电释放,避免由于静电引起芯片或者电子元件损坏;以及低压关闭(UVLO),欠压锁定,限制最低入输入电压。过压保护开关和过载保护开关有什么区别?1、负载如果是阻性负载,当电源有故障,负载上的电压有可能大幅上升,而电流的上

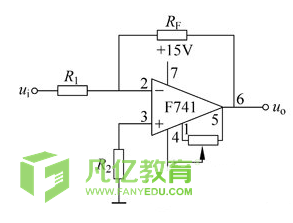

反向比例运算电路的认识

在反相比例运算电路中,电路输入信号ui总是经过一个电阻R1接到反相输入端,输出信号uo经过一个电阻RF反馈到反相输入端,如图1(a)所示。由图可见,图中电路是一个用国产芯片F741接成的反相比例运算电路,图中同时给出了电源连接及调零电路,并在同相输入端对地串了一个电阻R2=R1//RF,目的是使两个输入端对地的等效电阻相同。 (a)用F741接成的反相比例运算电路 (b)反相比例运算电路的简化图对于图1(b),由于理想运放的经输入电流为零,所以ip=in=0,由于运放的同相和

SDRAM芯片引脚介绍

以 Micron公司容量为512Mb(512兆位),规格为8M×16×4的某款 SDRAM为例,介绍 SDRAM的引脚定义。(1) CLK:时钟信号,为输入信号。 SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。(2) (2)CKE:时钟使能信号,为输入信号,高电平有效。CKE信号的用途有两个,其是关闭时钟以进入省电模式,其二是进入自刷新( SELF REFRESH)状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。在电路设计中需注意,应为C

LDO应用要点

(1) VRF滤波由LDO的工作原理可知,Vref(基准电压)的稳定性与LDO输出电源的纹波及噪声密切相关。为了减小器件面积,某些LDO在片内不提供对VREF引脚的滤波。在这种情下,设计者需在VREF引脚附近添加10uF电容,以保证VREF的低噪声和低纹波(2) SENSE(感应)引脚的处理SENSE引脚是LDO、DCDC电源芯片上常见的引脚在PCB上,当电源输出端与负载端相距较远时,输出电源Vout需通过较长距离的PCB导线(或PCB铜皮)才能加载到负载上,由于负载电流流经

扫码关注

扫码关注