- 全部

- 默认排序

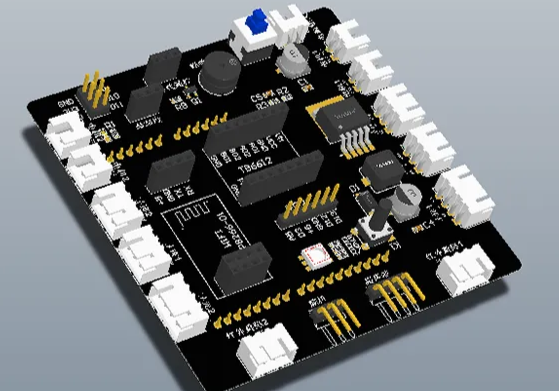

一个学习信号完整性的layout工程师今天整理下PCB封装的3D 模型添加,此步骤并不是所有的公司使用,因为我们平常给器件添加一个实际的高度,就已经OK了。只不过我们在看整版的3D模型是,每个器件都是方方正正的,不太美观。所以有的人要求完成

PADS对齐器件

为了布局美观性,设计时会根据情况对器件进行对齐处理,设计师可以利用格点,然后抓取器件中心,将器件放置到格点上,完成器件对齐,也可以使用对齐工具,将器件快速对齐。在PCB中选中需要对齐的元器件(2个器件以上),鼠标右击,在弹出快捷菜单中选择“

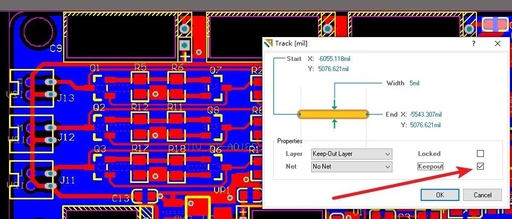

在做PCB设计的时候,很多的小伙伴经常会遇到这样或那样的一些问题,所以华秋电路收集整理了一些比较常见又容易规避的问题和解决方案,同大家分享一下,希望能为大家设计出高效美观的PCB产品提供一些帮助!1.内槽/板框锁住无法导出生产怎么办? 内槽/板框锁住,生成Gerber制板文件时无法导,常见的处理步

虽然很多工程师对印制电路板(PCB)的设计和制造流程都很了解,但是仍然有很多工程师对PCB板的装配工艺不太清楚,所以今天我们来聊聊PCB板的装配工艺。1、元器件引线成型为使电子元件在印制电路板上排列整齐、美观,避免虚焊等故障,将元器件引线成

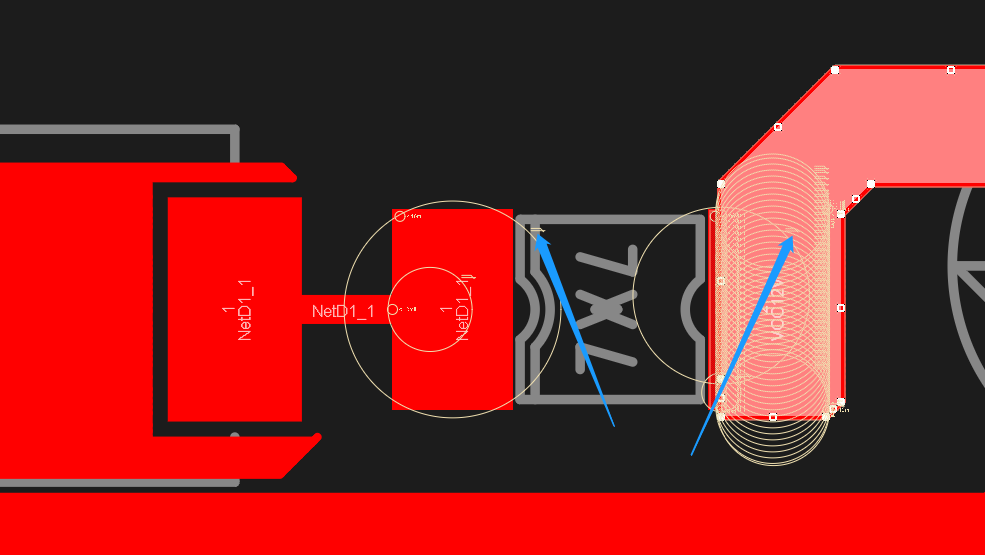

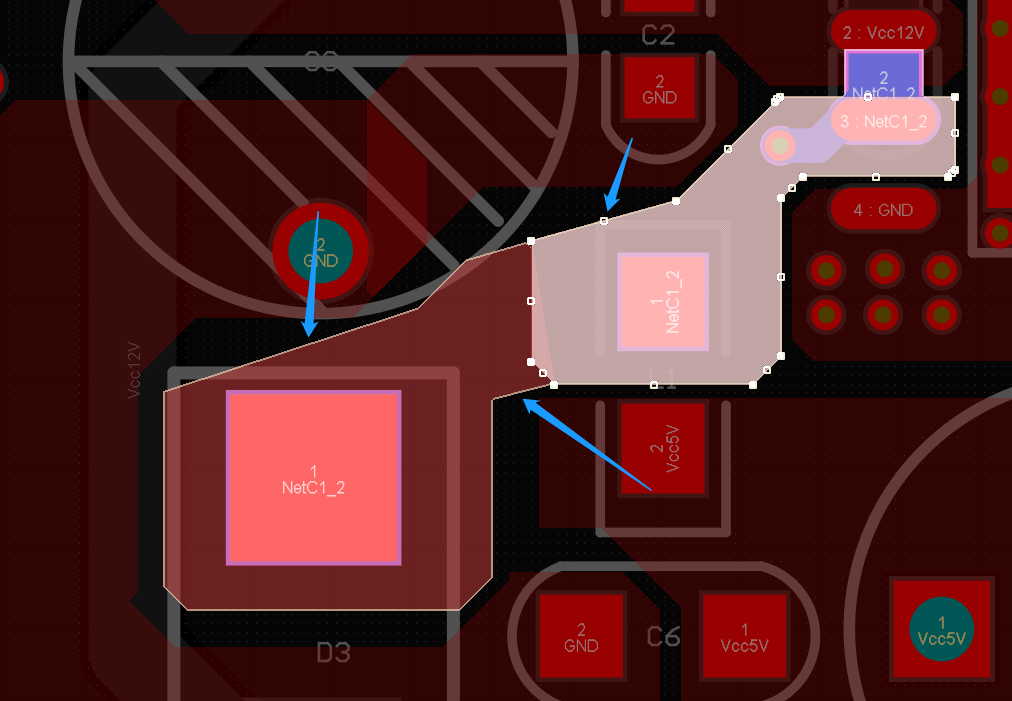

pcb上还存在短路2.滤波电容放置先打后小,电源输入过孔打在滤波电容前面3.电源输出主干道需要铺铜处理4.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.铜皮处理不当,不美观,需要优化一下,尽量钝角6.反馈从滤波电容后面

铜皮优化不当,不美观,尽量不要有任意角度2.反馈从滤波电容后面取样,走一根10mil的线即可3.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.注意器件摆放不要遮住一脚标识5.铺铜尽量把焊盘包裹起来,容易造成开路6.电源

在PCB的版图设计里,很多优秀的工程师在设计时都会默认对称型设计,这样做的好处不仅是可以减小EMC影响,也能使板子设计出来更加美观,因此如果小白正在学习版图设计,可以来看看这篇文。首先需要知道的是,该对称性设计经常在模拟电路中使用,对称性设

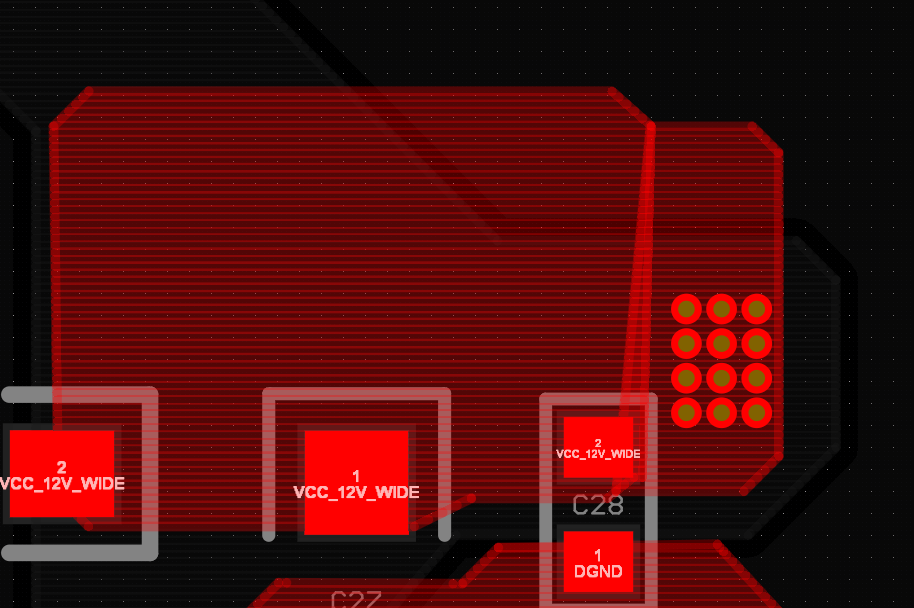

能铺完一整块铜皮的就一次铺完,优化下:过孔打在第一个电容输入前面:上述一致问题,能铺完的就整体铺完,不要太多这种碎铜:铺铜尽量美观,不要直角锐角,尽量全部钝角铺铜:不合格的铜皮都重新绘制铺配置电阻电容还有飞线,没有连接:注意焊盘出线注意规范

使用合适的格点大小能有效的提高我们设计的效率以及所设计文件的美观性。第一步:执行菜单命令工具-选项,如图1所示图1 设置选项示意图第二步:在弹出的选项窗口常规栏中可以找到栅格设置,如图2所示,在设计中通常设置设计栅格与显示栅格即可,推荐设置

注意数据跟地址,时钟,控制之间用GND走线隔开:建议等长线的GAP也尽量满足3W,避免自身的串扰:等长不是很美观,尽量采取咬合等长,既美观也节省空间,还可以调整下美观性:上述一致原因,注意等长线的gap:其他的等长没什么问题,只要是等长美观

扫码关注

扫码关注