- 全部

- 默认排序

在DDR的设计中,需要对数据线及地址线进行分组及等长来满足时序匹配,通常DDR的数据线之间的长度误差需要保证在50mil以内,地址线的长度误差需要保证在100mil以内。执行菜单命令【设计】-【规则】或者使用快捷键DR打开规则约束器,在“H

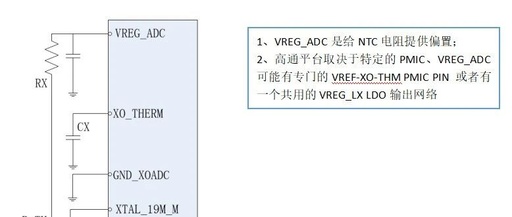

高通晶振设计指导

前言:1、随着目前PCB越来越小,越来越薄,导致更加严重的散热问题2、XTAL_IN/XTAL_OUT和GND_LINE可以作为热源的传热路径,导致GPS/GNSS受到影响。3、布局区域约束要求晶振布局必须靠近PMIC 一、布局要求1、晶振需要远离PMIC,需要保证XTAL_IN/OUT的距离在3~

出现以上飞线不从过孔出线的原因是其拓扑结构所导致,解决方式就是设置下拓扑结构。1、执行菜单栏命令“设计-规则”,或者快捷键DR,快速打开“PCB规则及约束编辑器”对话框,如图1所示。2、在对应的对话框中,选择“Routing-Routing

本文介绍了如何通过使用ZPLM优化操作数在评价函数编辑器(Merit Function Editor )中使用ZPL宏定义复杂的优化目标。本文介绍了如何使用ZPLM约束系统的质心,以确保其能正确地平衡。作者 Alessandra Croce

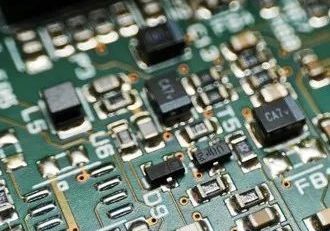

要想做好电路设计,第一步是要根据自身需求来挑选PCB材料,PCB材料并非全都选好材料,而是要切实符合产品需求,保证PCB上的电路和元件正常工作,而且材料的选择间接影响到PCB板的电磁兼容性能和约束工作。良好的PCB材料选择,可以做到提高PC

随着单片单片器件上集成的功能越来越多,高密度微孔已成为集成系统等硬件技术的应用,自由角度布线和自动布局布线等开始成为EDA工具的必备功能,然而很多小白不太清楚自动布线和自由角度布线是什么?有什么用?今天安排!1、设计约束条件由于要考虑电磁兼

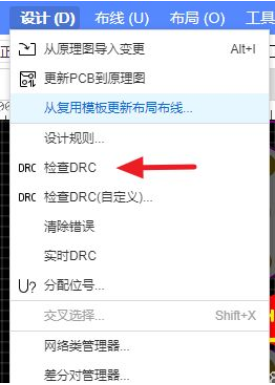

前期为了满足各项设计的要求,通常会设置很多约束规则,当一个PCB设计完成之后,通常要进行DRC。DRC就是检查设计是否满足所设置的规则。一个完整的PCB设计必须经过各项连接性规则检查,常见的检查包括开路及短路的检查,更加严格的还有差分对、阻

RF和微波无源元件承受许多设计约束和性能指标的负担。根据应用的功率要求,对材料和设计性能的要求可以显着提高。例如,在高功率电信和军用雷达/干扰应用中,需要高性能水平以及极高功率水平。许多材料和技术无法承受这些应用所需的功率水平,因此必须使用专门的组件,材料和技术来满足这些极端的应用要求。高水平的射频

射频电路板设计由于在理论上还有很多不确定性,因此常被形容为一种“黑色艺术”,但这个观点只有部分正确,RF电路板设计也有许多可以遵循的准则和不应该被忽视的法则。不过,在实际设计时,真正实用的技巧是当这些准则和法则因各种设计约束而无法准确地实施

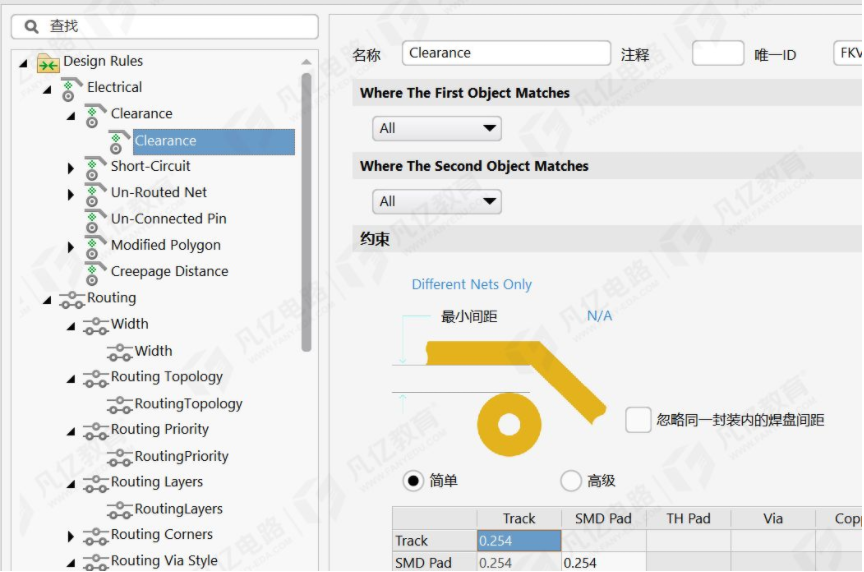

AD软件中怎么添加不同元素之间的间距规则呢答:AD软件提供了某一个元素针对其他元素之间的间距规则的设置。首先执行菜单命令【设计】-【规则】或者快捷键DR打开规则约束编辑器,然后在间距规则Clearance里面添加一个新的规则,如图1所示图1

扫码关注

扫码关注