- 全部

- 默认排序

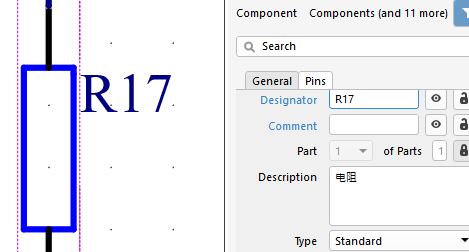

Altium Designer在原理图中默认给元器件添加的属性为Desugnator和Comment这两种属性,如果是绘制电阻电容这种类型器件时,可以在Comment栏填写Value值,但是有些设计者习惯在Value值栏填写,应该如何给元器件添加Value值属性呢

一、开关电源电磁干扰的产生机理开关电源产生的干扰,按噪声干扰源种类来分,可分为尖峰干扰和谐波干扰两种;若按耦合通路来分,可分为传导干扰和辐射干扰两种。现在按噪声干扰源来分别说明:1、二极管的反向恢复时间引起的干扰高频整流回路中的整流二极管正向导通时有较大的正向电流流过,在其受反偏电压而转向截止时,由于PN结中有较多的载流子积累,因而在载流子消失之前的一段时间里,电流会反向流动,致使载流子消失的反向恢复电流急剧减少而发生很大的电流变化(di/dt)。2、开关管工作时产生的谐波干扰功率开关管在导通时

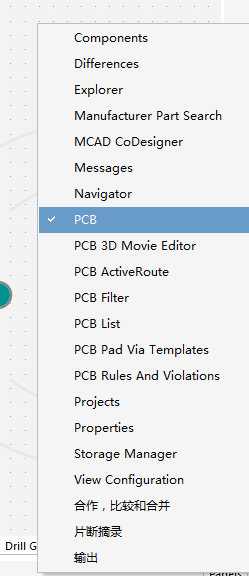

Class就是类,同一属性的网络或元件或层或差分放置在一起构成一个类别,即常说的类。把相同属性的网络放置在一起,就是网络类,如GND网络和电源网络放置在一起构成电源网络类。把属于90欧姆的差分放置在一起,构成90欧姆差分类

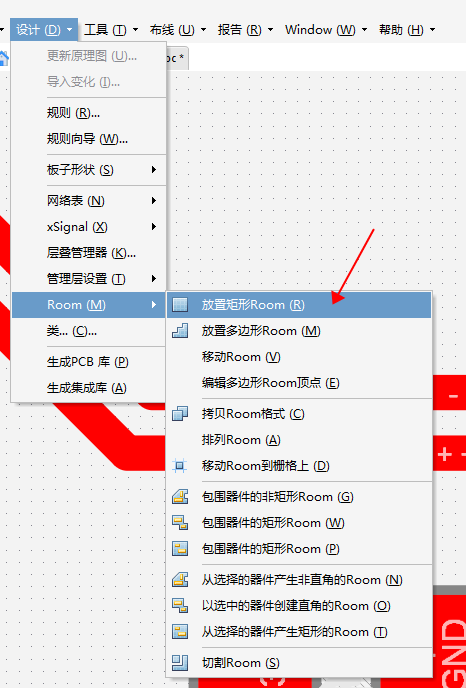

区域规则设置是针对某个区域来设置规则。为了满足设计阻抗和工艺能力的要求,需要对个别区域设置特殊的线宽走线或者间距或者过孔大小等,这时可以对这个区域进行特殊规则设置,常用于各类不同pitch间距的BGA。

我们在完成PCB的设计之后,通常需要生成用于生产的各类图纸,比如装配图纸、制造图纸、和相关的BOM等文件。这些文件虽然都可以通过PCB设计软件的相关菜单获得,但是寻找相应的菜单和逐一生成各类文件都要花费时间不说,文件生成之后还需要将其整理并存放到一起以备后续使用,这个过程相当繁琐。那么有没有方法,可以将这些图纸都生成在一个文件中,并且可以对不同的图纸进行标注,从而将设计人员从创建和整理生产文件的繁琐手续中解脱出来,使其有更多的时间专注于更有挑战性的PCB设计呢?

前文对差分类的添加进行了详细的讲述,不再进行赘述,这里对差分规则设置进行讲述。差分规则设置分为两种方法,一种为向导法,另一种为手工法。

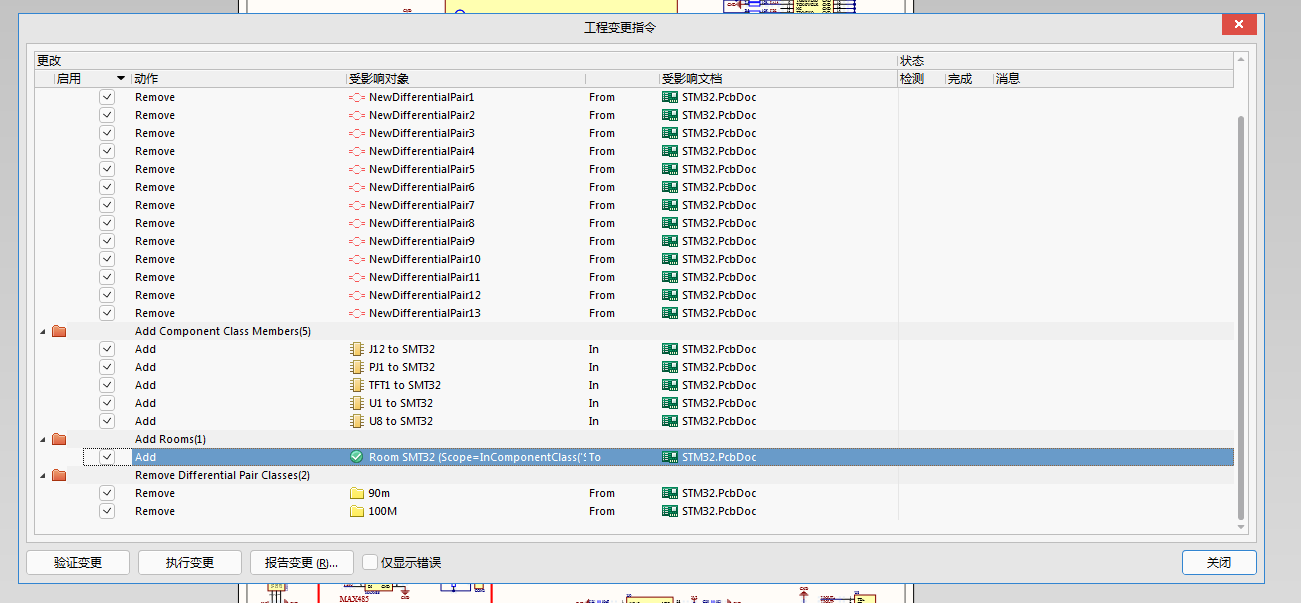

在PCB设计时,会根据PCB设计的一些情况,设置相对应的规则和区域,但是因为原理图这种没有设置,在原理图和PCB对比更新时不能把这些规则和区域去掉

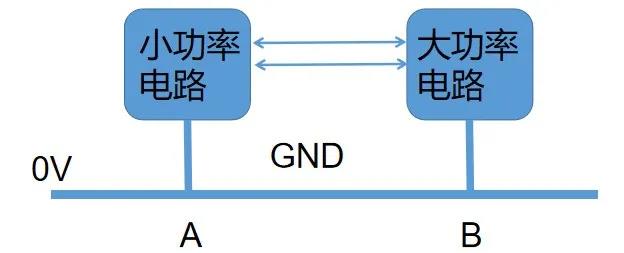

问一个简单而又很难回答的电路问题:电路中的地线GND,它的本质是什么? 在PCB Layout布线过程中,工程师都会面临不同的GND地线处理。 这是为什么呢? 在电路原理设计阶段,为了降低电路之间的互相干扰,工程师一般会引入不同的GND地线,作为不同功能电路的0V参考点,形成不同的电流回路。

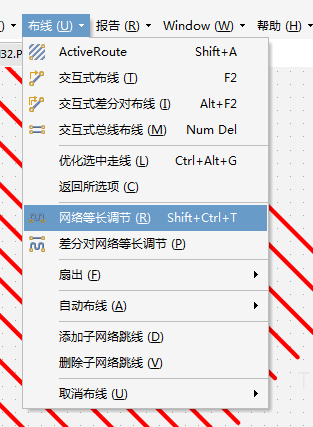

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

扫码关注

扫码关注