- 全部

- 默认排序

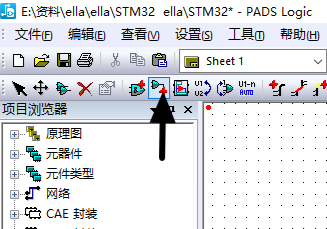

打开文件后,单击设计工具栏的连线命令,也可以使用快捷键F2,如图4-30所示。图4-30单击连线图标2)单击连线图标后,将光标移到元件的管脚位置,单击后连线以正交方式前进,单击鼠标左键进行暂停,双击鼠标左键可以停止走线,如图4-31所示。

总线的连接

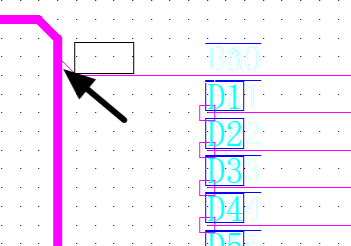

点击连线命令(快捷键F2),将管脚连接到总线上,如图4-56所示。图4-56 连线到总线(2)连线到总线时,系统会弹出“添加总线网络名”对话框,确定网络名后点击确定,单击鼠标左键放置网络名,如图4-57、4-58所示。图4-57 添加

如何测量电源纹波?

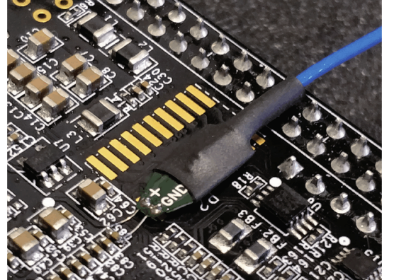

今天聊一聊如何测量电源的纹波。1 纹波的测量点要求纹波测量点要选择靠近负载的地方,例如CPU的供电管脚上的去耦电容上。PDN是一个网络,主板上一个电源平面的不同的地方纹波是不一样的,建议选择最远,负载最大,环境最恶劣的地方。如果一个电源网络

No ERC检查点即忽略ERC检查点,是指该点所附加的元件管脚在进行ERC时,如果出现错误或者警告,错误或者警告将被忽略过去,不影响网络报表的生成。忽略ERC检查点本身并不具有任何的电气特性,主要用于检查原理图。 图5-50 放置No E

PADS虚拟过孔

虚拟过孔一般在有拓扑结构的设计时被使用,比如T形拓扑,虚拟过孔可以当作一个虚拟的管脚,满足了拓扑结构设计时等长的需要。鼠标右键选择“选择网络”,鼠标左键选择需要添加虚拟过孔的对应的网络(可选择焊盘或者布线上),单击鼠标右键选择“添加虚拟过孔

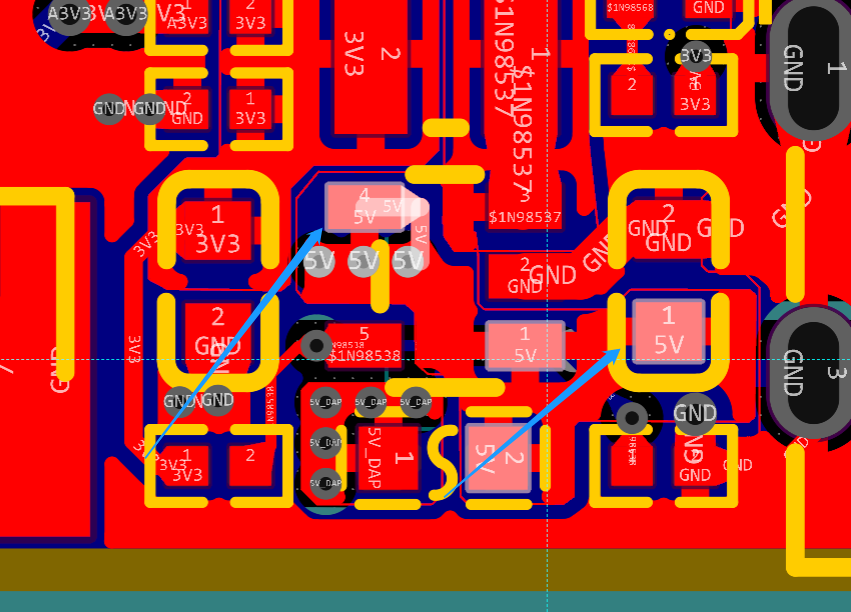

在进行PCB设计的过程中,某些焊盘已经铺上铜皮,并且在设计规则中已经设置其与铜皮的连接方式。但是存在其与后期生产工艺的问题导致需要针对此焊盘设置独立的铜皮连接方式,也就是如何设置单个焊盘跟铜皮的连接方式的问题。以下图这个2号管脚中的+5V网

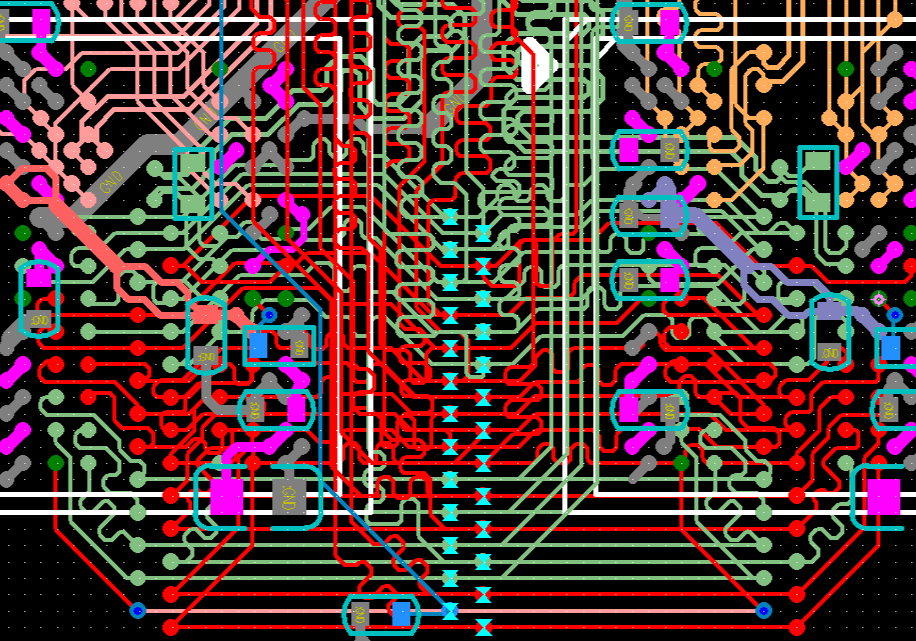

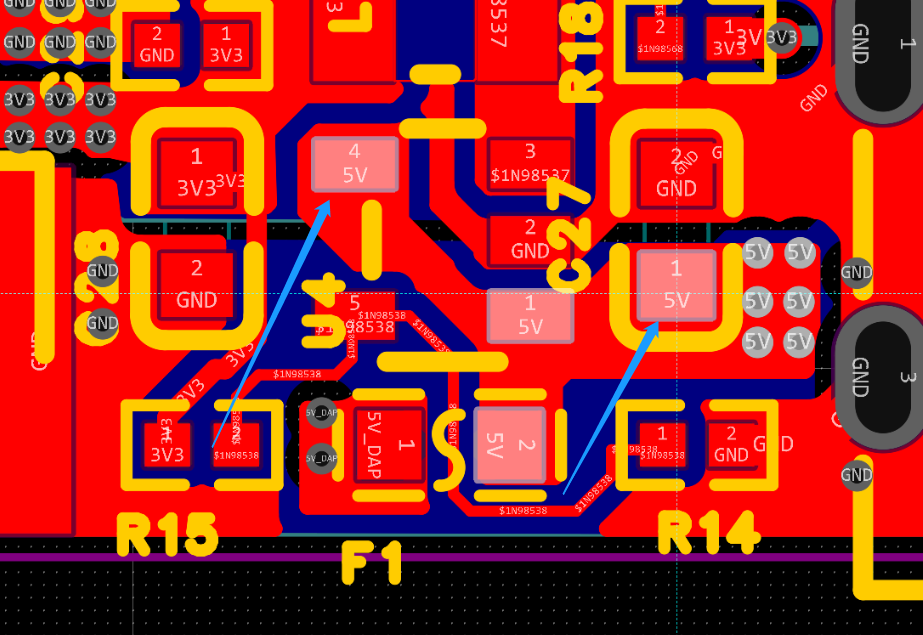

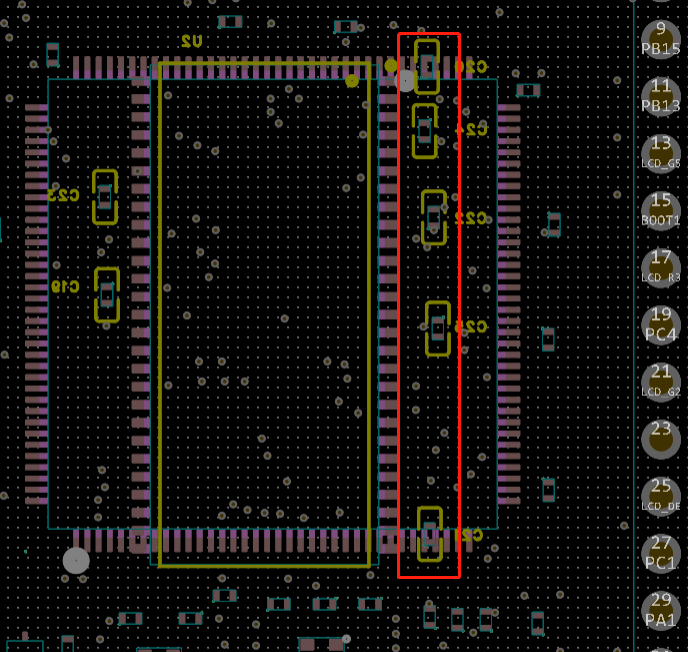

1.电源输入的滤波电容应该靠近输入管脚放置2.【问题分析】:注意等长线之间需要满足3W规则3.【问题分析】:USB需要进行等内等长处理,等长误差为5mil4.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-

电源输入的滤波电容应该靠近输入管脚(4脚)放置2.此处走线需要优化一下,尽量不要有直角,走线不要从器件中间穿3.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍4.器件摆放注意局部对齐处理5.logo图片最好不要放在焊盘上【问题改善建

器件摆放注意局部对齐处理2.注意器件干涉3.电源输出的滤波电容要靠近输出管脚放置4.电源输入输出换层打孔处理不当,输入应该打在滤波电容的前面,输出打在滤波电容的后面5..差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍6.确认一下此处

器件摆放注意局部对齐处理2.电源输入的滤波电容应该靠近输入管脚(4脚)放置3.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.确认一下此处是否满足载流【问题改善建议】:加粗线宽或者铺铜处理5.差分线处理不当,锯齿状等长,

扫码关注

扫码关注