- 全部

- 默认排序

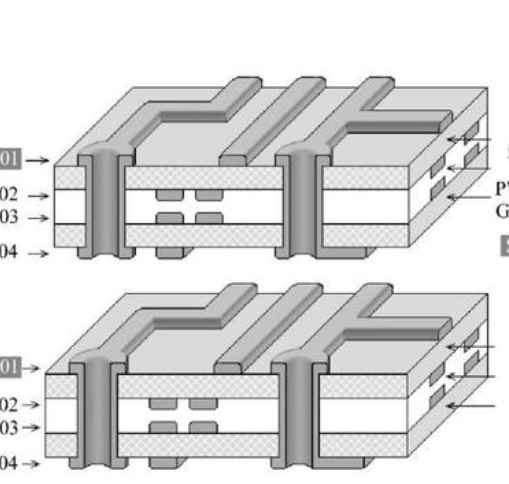

一、PADS8层DDR3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层PCB设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

1) 许多硬件工程师基本功不合格许多企业,在提到电源完整性的时候,许多工程师(甚至是工作了3-4年的)根本没有了解。他们的电容放置位置不取值不合适,电源分配网络设计不合理,最小回路等等基本没有概念,全靠经验和试凑。对于电源完整性概念背后的技术点懵懵懂懂,直接影响了他们的产品质量。基本功不合格的硬件工程师,怎么能突破基础岗位呢?

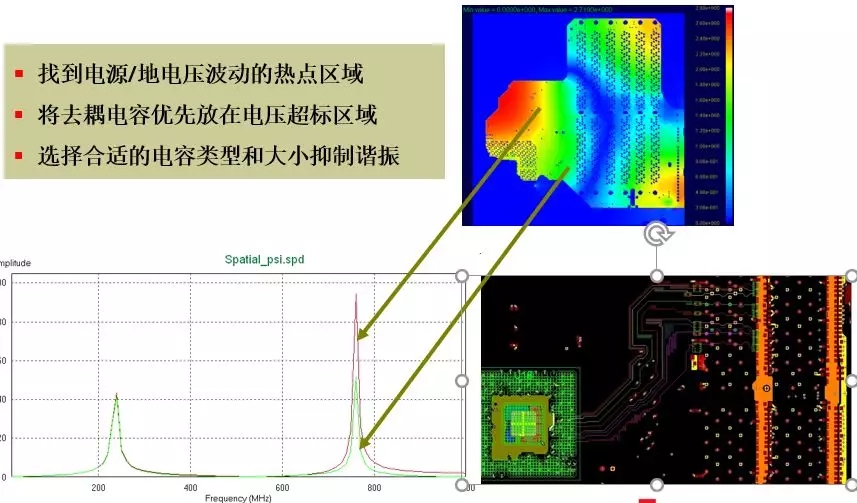

Sigrity PowerSI是IC封装和PCB设计快速准确的全波电磁场分析,作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。PowerSI可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压

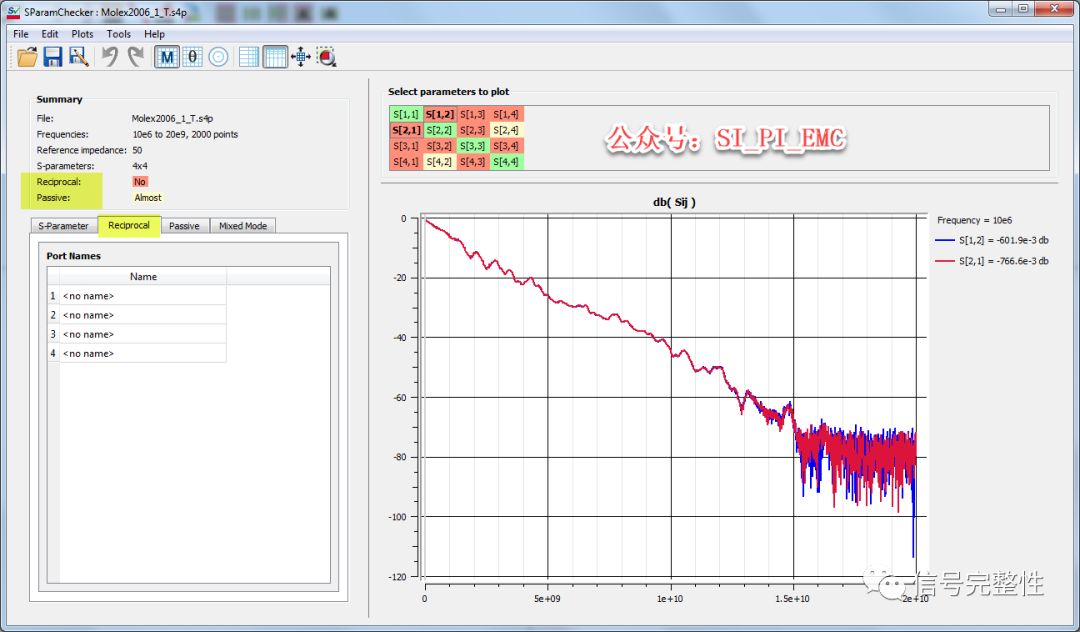

S参数被大量应用于高速电路和高频电路设计和仿真中。对于越来越高速的电子产品,以及不仅仅是信号完整性和电源完整性工程师需要了解S参数,对于电子工程师、测试工程师和EMC工程师等等都需要了解。

答:在进行阻抗、层叠设计的时候,主要的依据就是PCB板厚、层数、阻抗值要求、电流的大小、信号完整性、电源完整性等,一般参考的原则如下:l 叠层具有对称性;l 阻抗具有连续性;l 元器件面下面参考层尽量是完整的地或者电源(一般是第二层或者倒数第二层);l 电源平面与地平面紧耦合;l 信号层尽量靠近参考平面层;l 两个相邻的信号层之间尽量拉大间距。走线为正交;l 信号上下两个参考层为地和电源,尽量拉近信号层与地层的距离;l&nbs

答:在进行阻抗、层叠设计的时候,主要的依据就是PCB板厚、层数、阻抗值要求、电流的大小、信号完整性、电源完整性等,一般参考的原则如下:

主题;IC&SIP芯片封装设计与信号|电源完整性|电热仿真分析和建模1、IC&SIP产业封装设计验证工程师的前途集成电路IC&SIP设计处于集成电路产业的龙头地位,对产业整体的发展起着带动作用。未来几年内我国芯片生产有望每年以12%的速度递增,因此IC产业设计专业人才处于极度供不应求的状态。可以这样说,这正是我国很大程度上没有足够的IC产业设计人才的根源。

扫码关注

扫码关注