- 全部

- 默认排序

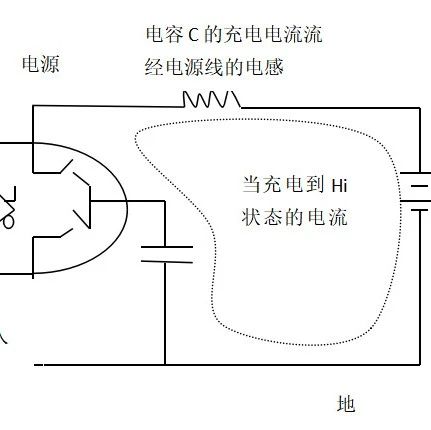

【摘要】 在某单板上,由于CPU芯片GMII接口的电源上只加了磁珠滤波,引起的故障:在网口通信时,当通信包的内容为低速码型(全0全1)时,没有丢包;当更改为伪随机包时(码型速率快),丢包严重。最终在磁珠后加电容,问题解决。原因分析: 从电源的输出到所供电的逻辑电路之间的引线可能包括值得重

过孔的寄生电感如何计算?

在高速数字电路设计中,过孔作为层间连接的关键元素,其寄生电感对电路性能有不可忽视的影响,而寄生电感的存在会削弱旁路电容的滤波效果,进而影响整个电源系统的稳定性,所以电子工程师必须计算过孔的寄生电感,将影响降到最低。1、过孔的寄生电感计算公式

磁芯的特性理解

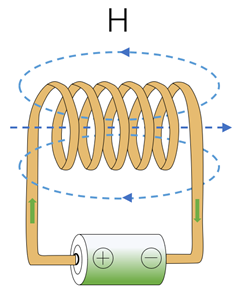

大家好,今天我们来简单聊一聊磁芯。之所以说磁芯,是因为磁芯对于电感来说,就相当于是电容的中间绝缘介质。磁芯决定了电感的很多特性。比如大家都知道,①电感线圈里面加个磁芯,电感值会增大很多,这是为什么呢?②还有电感有饱和电流,那电感为什么会饱和呢?③磁滞回线又是什么呢?④磁导率又是个啥? 物质的磁性首先

磁芯的气隙

最近又了解新东西了,那就是气隙,电感的气隙或者是变压器的气隙。总有人喊我大佬,我知道,他们只是不知道怎么称呼我而已。说出来我也不怕掉粉,在不久之前,我甚至都不知道气隙是什么。我原来以为,变压器磁芯中间那个缺口存在的原因,只是因为生产不方便,或是为了绕线方便。以前工作中用得最多的也就是电感了,电感选择

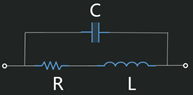

电感的阻抗-频率曲线

上一节我们说明白了电感的高频模型是怎么来的,现在就来说一说由高频模型提取出的阻抗频率曲线,这个曲线对于我们分析理解问题有很大帮助,下面就理论结合实践来详细讲解。 电感阻抗频率曲线电感的高频模型如图所示我们根据这个模型,可以得到阻抗公式,也可以得到谐振频率公式。也就能画出阻抗频率曲线了。横轴为频率,纵

在电路设计与制造中,我们会遇见五花八门的问题,其中之一是电路板制作好后,总是有呲呲的噪声,很多人认为这肯定是电感出错所致,这个说法是正确的吗?其实这个说法算是正确的,电感作为电路中的关键元件之一,其特性与状态基本上是此类噪声问题的主要源头,

电感有耐压值吗?

关于电感,我在很久之前梳理过了,不过最近又学了点新东西,那就是电感的耐压值参数。 我们确实很少会关注电感两端的耐压,它也不是关键参数,那么只会有一种原因,那就是我们的使用场景中,电感耐压总是满足要求的,所以就不用考虑了。 传统绕线电感和磁封胶结构电感的磁芯材料是铁氧体(绝缘体),漆包线耐压一般是1K

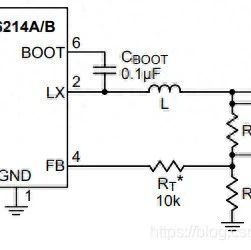

如下图为典型的DCDC电路:芯片是台湾省立琦科技的。上图为DCDC典型应用电路,CIN为输入滤波电容,CBOOT是上管驱动“自举”电容,L是储能电感,R1和R2是反馈电阻,CFF是前馈电容,COUT是输出滤波电容,RT是内部运放补偿器件。一、理论分析没有前馈电容如果没有前馈电容,内部补偿DC-DC转

在手工焊接时,总会遇到五花八门的问题,其中之一是要焊接有磁性的元件,如电感器、变压器等,这些磁性元件的吸引力不仅容易导致元件位置偏移,还可能吸附微小金属碎屑,影响焊接质量及电路性能,所以如何应对?1、预先固定元件在焊接前,使用镊子或专用夹具

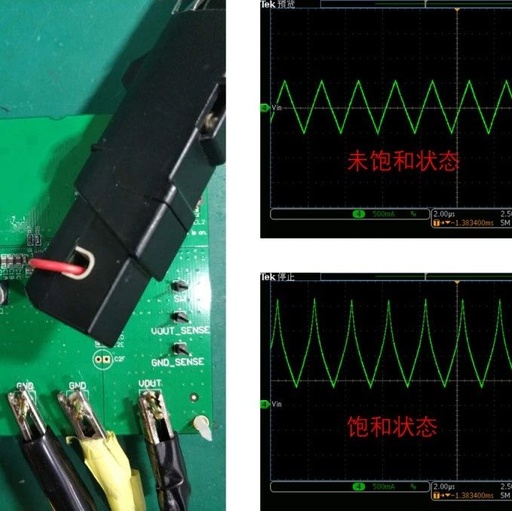

电感饱和的原因先直观的认识下什么是电感饱和,如图1:图1我们知道当图1线圈中通过电流时,线圈会产生磁场;磁芯在磁场的作用下会被磁化,其内部磁畴会慢慢旋转;当磁芯被完全磁化时,磁畴方向全部和磁场一致,即使再增加外磁场,磁芯也没有可以旋转的磁畴了,此时的电感就进入了饱和状态。从另一个角度来看,如图2所示

扫码关注

扫码关注