- 全部

- 默认排序

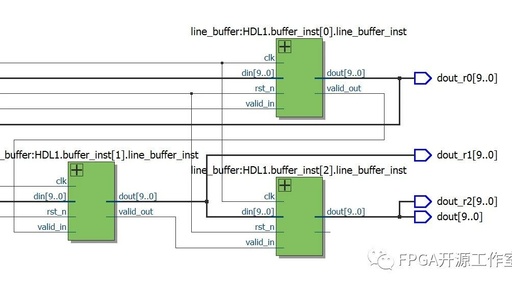

FPGA图像处理之行缓存(linebuffer)的设计二作者:OpenS_Lee01背景知识 在FPGA数字图像处理中,行缓存的使用非常频繁,例如我们需要图像矩阵操作的时候就需要进行缓存,例如图像的均值滤波,中值滤波,高斯滤波以及sobel边缘查找等都需要行缓存设计。这里的重要性就不在赘述。0

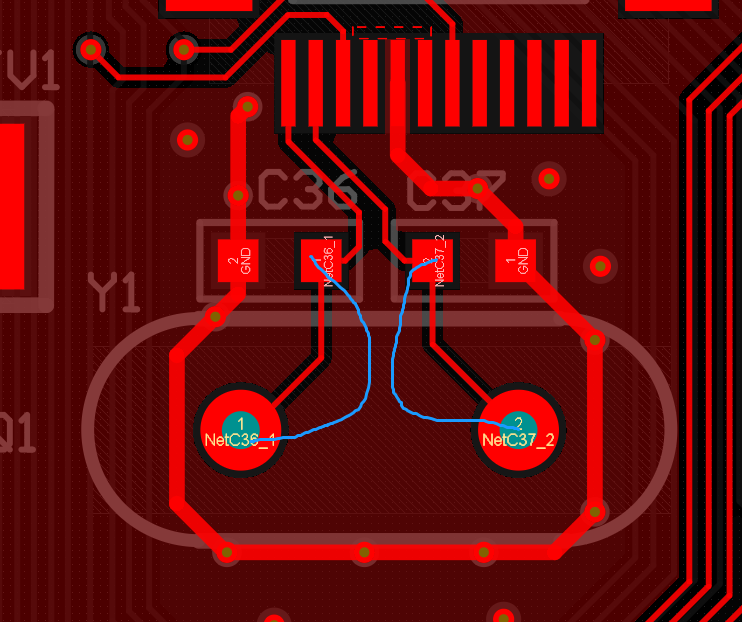

晶振走内差分需要再优化一下2.跨接器件旁边尽量多打地过孔,分割间距最少11.5mm,有器件的地方可以不满足3.网口差分信号需要进行对内等长,误差5mil4.变压器所有层需要挖空处理5.反馈信号要从最后一个输出滤波电容后面取样6.注意数据线之

电容器是电子电路中常见的passive元件,用于存储和释放电荷,及在电路中起到滤波、耦合、隔直流等作用,是很多电子工程师会应用的重要元件,电容器按期类型有不同的作用及个点,下面来看看吧。1、陶瓷电容器特点:陶瓷电容器是最常见的电容器之一,有

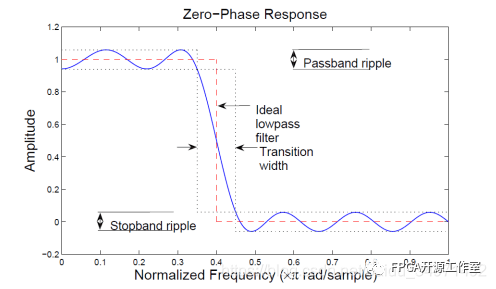

Matlab数字滤波器设计实践—FIR1低通滤波器设定在理想情况下,低通滤波器使信号中低于指定截止频率 ωc 的所有频率分量保持不变,并拒绝高于 ωc 的所有分量。由于实现理想低通滤波器所需的脉冲响应是无限长的,因此无法设计出理想的 FIR 低通滤波器。理想脉冲响应的有限长度

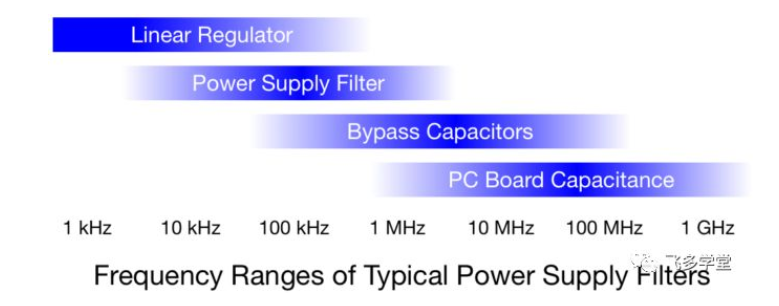

本文介源滤波器的作用、原理、要求和步骤,以及一些设计的技巧和注意事项。高频纹波会直接穿过线性稳压器。纹波来自开关电源、数字电路和无线电干扰。在频率高于 10 kHz 时,大多数线性稳压器开始失效。分布在芯片之间的小旁路电容在约1MHz时开始

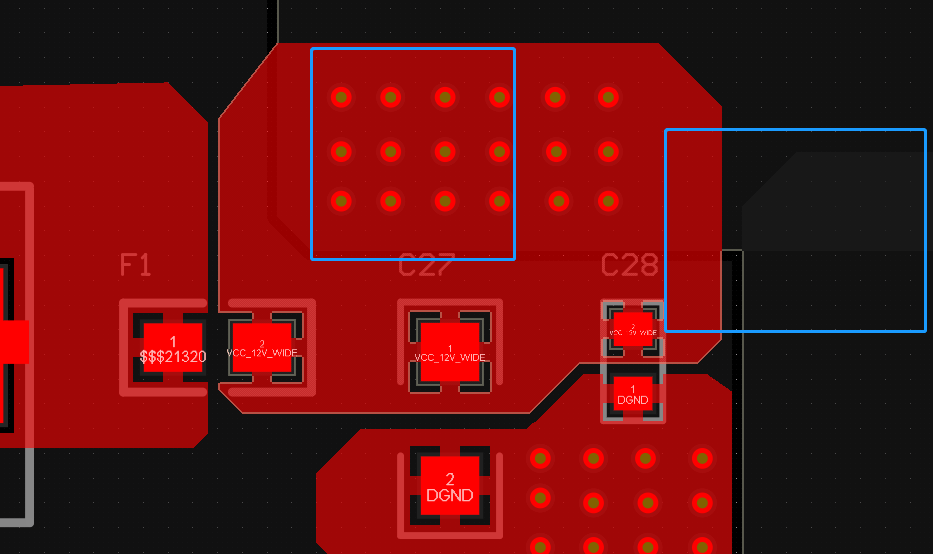

存在多处开路地网络后期自己在bottom层铺铜进行连接2.采用单点接地,此处可以不用打孔,只需要在芯片中心打孔进行回流即可3.输入打孔要打在滤波电容的前面4.输出打孔要打在滤波电容后面5.以上评审报告来源于凡亿教育90天高速PCB特训班作业

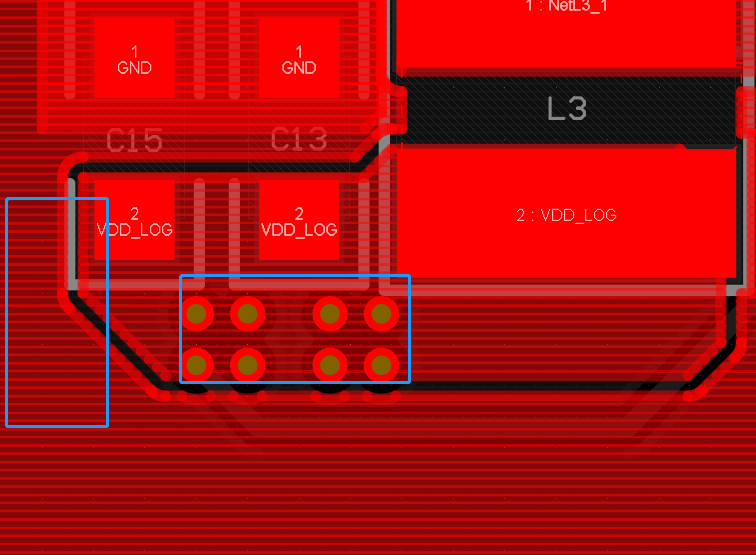

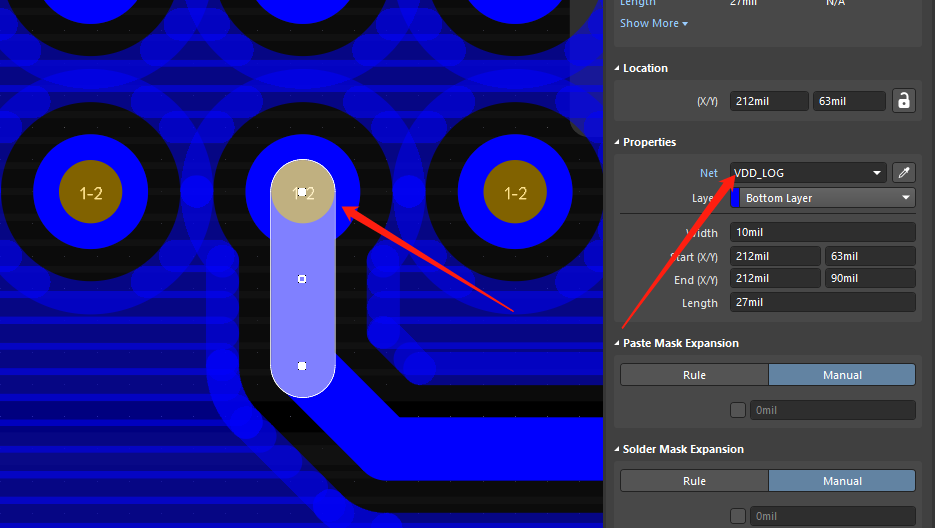

输出打孔要打在最后一个滤波电容后面2.器件布局尽量紧凑,对齐处理3.注意焊盘出现规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.注意铺铜不要有任意角度,尽量钝角处理后期自己优化一下铜皮5.电感所在层的内部需要挖空处理6.反馈线走1

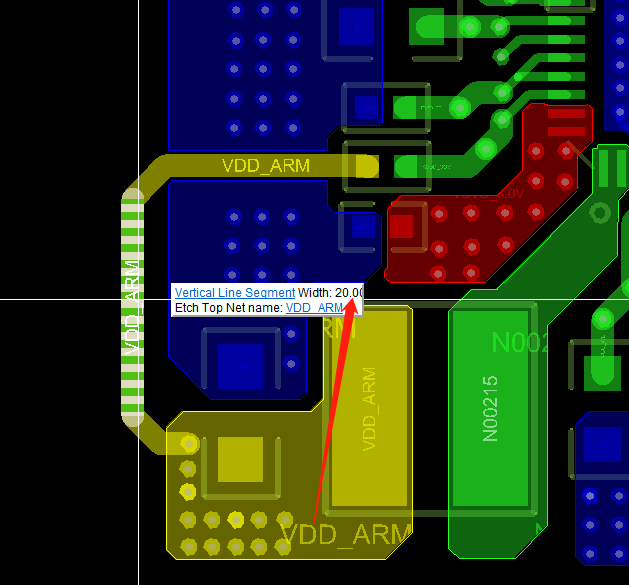

反馈线只用走10mil即可2.输出打孔要打在最后一个电容后面,反馈走线即可,不用铺铜输出打孔都需要再调整一下3.此处存在drc,短路了4.此处不满足载流,建议铺铜处理5.此处反馈器件要靠近管脚放置6.管脚滤波电容需要靠近管脚放置,保证一个管

输出打孔要打在滤波电容后面2.此处不满足载流,载流是一铜皮最窄出计算的,后期自己加宽一下铜皮3.铺铜是尽量把焊盘包裹起来,这样容易造成开路4.存在多处开路和drc报错5.电感下面不要走线和放置器件6.注意中间散热焊盘上的过孔需要开窗处理7.

存在无网络过孔,短路了2.输出过孔要打在最后一下滤波电容的后面3.过孔不要上焊盘4.电感下面尽量不要放置器件和走线5.存在多处开路和drc报错,后期自己处理一下6.注意走线需要连接到焊盘中心,此处需要优化一下7.相同网络的走线和铜皮未进行连

扫码关注

扫码关注