- 全部

- 默认排序

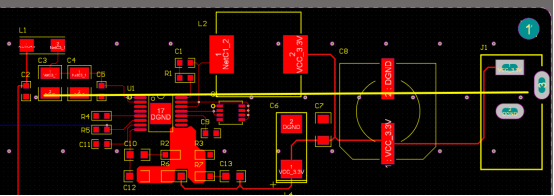

RJ45的座子要靠近板框放置2.注意差分走线要尽量耦合3.网口除差分信号外,其他的都需要加粗到20mil,器件靠近管脚放置4.晶振需要包地处理5.注意过孔不要上焊盘,地网络就近打孔,缩短回流路劲6.差分对内等长存在误差报错7.TX和RX要添

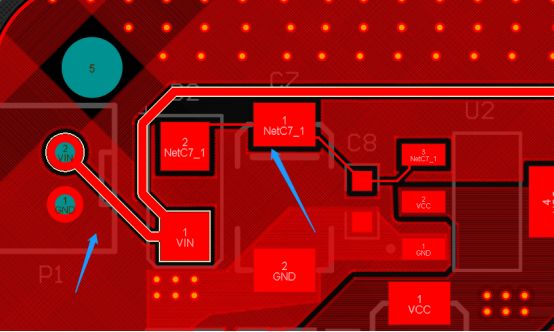

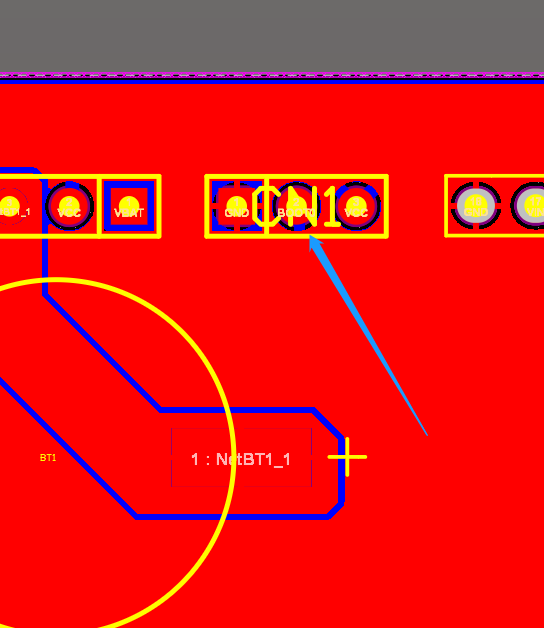

注意电源输入输出尽量铺铜处理,满足载流 输出过孔要打在滤波电容后面 注意器件摆放不要太靠近板框,建议最少2mm 注意焊盘要规范出线 晶振需要包地处理 电容靠近管脚放置,走线不要有直角 走线不要从焊盘中间穿,后期容易造成短路 此处电池走线不满

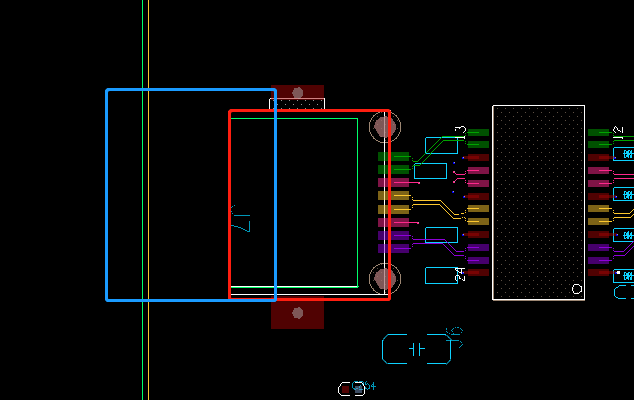

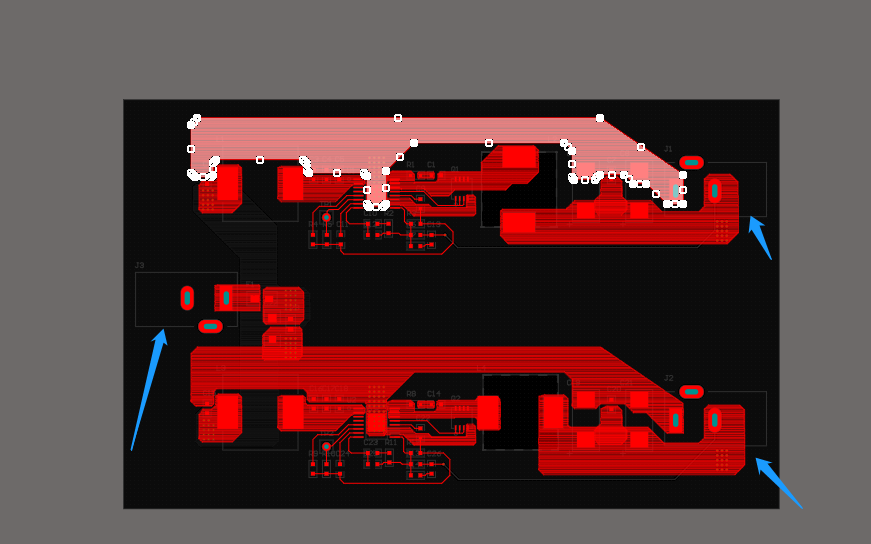

1.只有板框没有生成板子,应像下图一样生成黑色板子2.整板铺铜没有铺成功3.差分走线需要控制100欧姆阻抗,走5mil线框7mil间距,用布线-交互式差分对布线4.差分对布线按照信号信号流向顺序连接5.变压器的封装下方需要做铺铜挖空处理,变

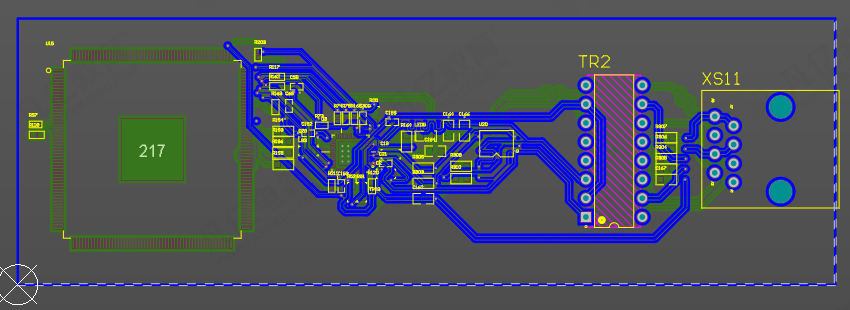

Cadence allegro学习笔记第一节 启动与板框的制作1、启动操作启动PCB Editor图标,弹出对话框后选择Allegro PCB Designer后择OK进入界面。 选择File文件菜单选择New新建弹出下面对话框。设置保存路径、输入文件名称、选择Board后选择OK

器件位号丝印后期设计完成需要调整,不要重叠:注意板上过孔是否盖油,不要开窗:注意看下工程里面原理图是空的:铺铜注意按照左边钝角绘制,不要直角:可以优化。类似的情况自己优化下。注意晶振底部不要走线:建议是PCB板框放在机械层:器件位号都放到器

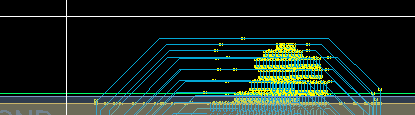

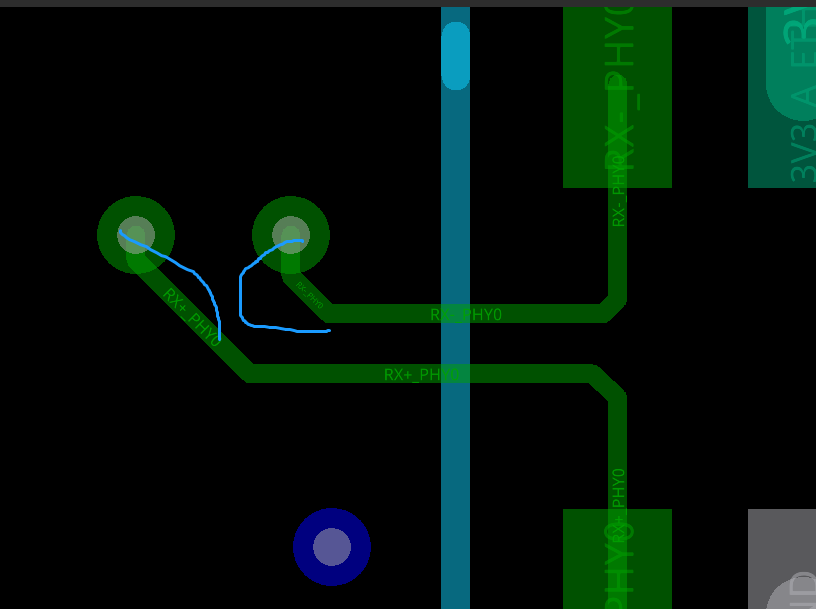

差分出线要尽量耦合2.差分对内等长误差5mil3.TX和RX需要创建等长组进行等长4.器件摆放进行电容靠近管脚5.走线需要优化一下,尽量不要有直角和尖角6.座子要超出板框进行摆放以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了

座子需要靠近板框放置2.不要随意改动原理图所需要用的封装3.此处走一根10mil的线即可,不用进行铺铜4.电感所在层的内部需要挖空5.输出电容按照先大后小顺序摆放,不要修改电容封装后期自己按照原理图自己调整封装6.器件摆放注意中心对齐处理,

要求一字型或L型布局,相邻器件中心对齐 输出座子要伸出板框一段 电源输入和输出主干道要铺铜处理,信号流向尽量顺畅 Dcdc模块要求单点接地,整条电路GND网络焊盘连接到芯片下方统一打孔接到底层 大电感下方所有层挖空铺铜处理 此处是反馈引脚,

Cadence allegro学习笔记第一节 启动与板框的制作1、启动操作启动PCB Editor图标,弹出对话框后选择Allegro PCB Designer后择OK进入界面。 选择File文件菜单选择New新建弹出下面对话框。设置

扫码关注

扫码关注