- 全部

- 默认排序

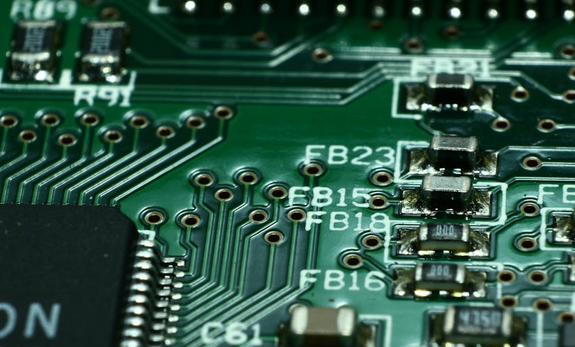

在PCB设计中,晶体振荡器(晶振)作为时钟信号的源头,其稳定性和准确性对系统整体性能至关重要,在双面板设计中,可能会遇见这个说法“晶振下方不得走线”,这个说法是否属实?为什么不能走线?1、晶振的工作原理及特性晶振通过石英晶体的压电效应,产生

晶体振荡器(晶振)是很重要的电子元件,在电子设备中起着提供稳定时钟信号的关键作用,但工程师可能会遇见晶振不起振现象,如何针对该问题查找原因解决问题?下面来探讨下!1、PCB板布线错误PCB板上的布线设计直接影响电路的性能。如果布线错误,如信

晶振(晶体振荡器)在电子系统中很重要,它为各种电路提供稳定的时钟信号,如果晶振不起振,可能导致整个系统无法正常工作,也不好排查问题,所以如何解决晶振不起振问题?1、电路检查首先,检查晶振电路的设计是否符合相应型号单片机的推荐电路,任何电路连

在电子工程领域,有源晶振(也叫做振荡器)是极其重要的元件,负责提供稳定的时钟信号,对确保电路的稳定运行和准确性至关重要,然而,由于有源晶振的引脚和封装设计各异,工程师在装配或维修时可能会遇见无法分辨方向的问题,那么如何解决?1、标记识别法观

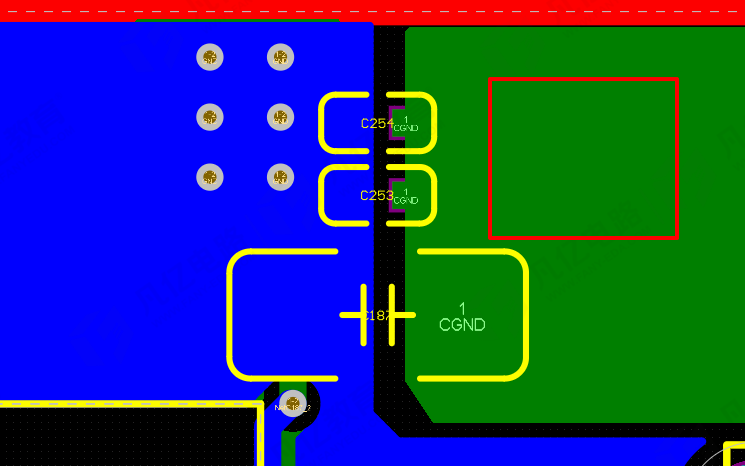

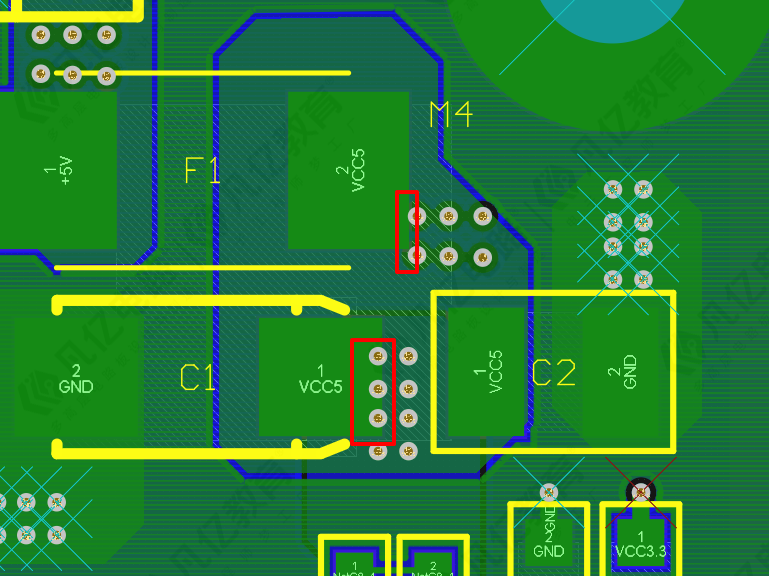

跨接处两边地多打过孔晶振包地约80mil距离打一个过孔过孔不要上焊盘,过孔间距太近电源走线出焊盘后尽快加粗,出焊盘后不要长距离不加粗走线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助

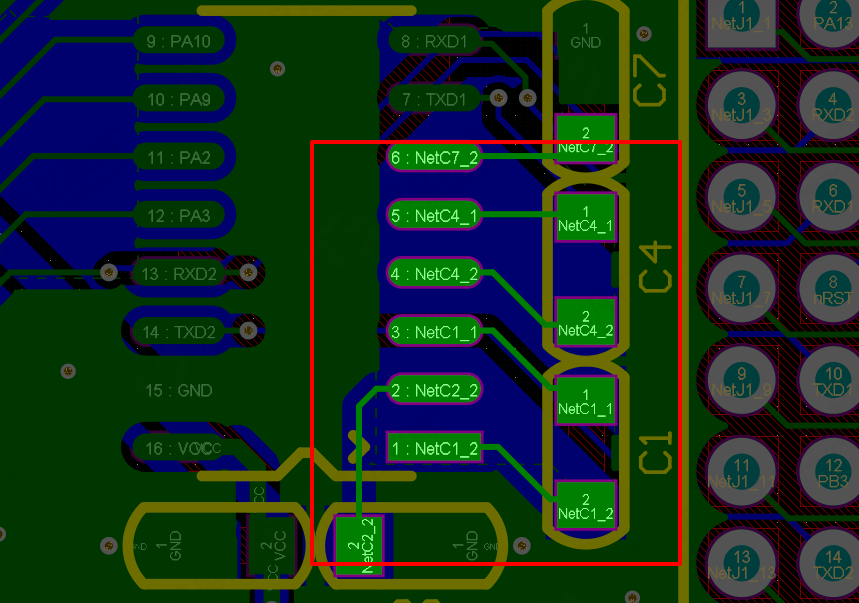

232模块c+-、v+-所接升压电容,走线需要加粗到10mil以上晶振包地打孔处理usb差分尽量走一层,换层长度不要太长器件布局太近相互干涉,大器件到小器件间应最少隔开1.5mm以上电源加宽载流,走线加宽或铺铜走线不完全连接,走线应连接到焊

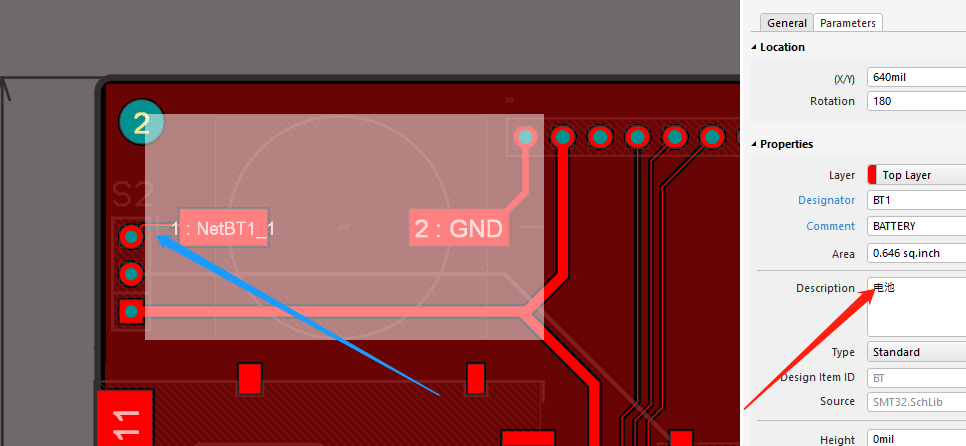

电池走线需要加粗满足载流2.注意晶振下面不要走其他信号线,并包地处理3.走线可以在优化一下走线没有连接到过孔中心,存在开路此处不满足载流,电源输入尽量铺铜处理,电容先大后小摆放注意电源输出要从滤波电容后面,后期自己调整一下布局,注意线宽是否

晶振决定数字电路的生与死

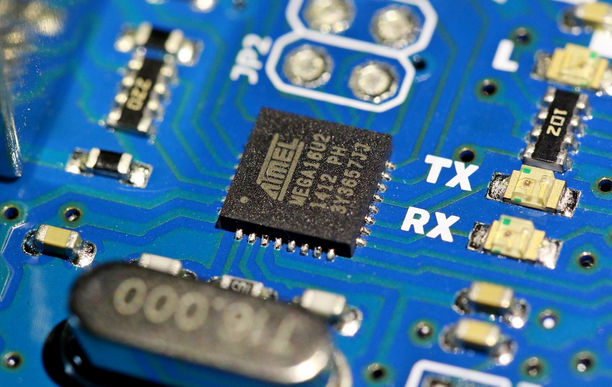

晶振,在板子上看上去一个不起眼的小器件,但是在数字电路里,就像是整个电路的心脏。数字电路的所有工作都离不开时钟,晶振的好坏,晶振电路设计的好坏,会影响到整个系统的稳定性。所以更多的了解晶振,选择好系统使用的晶振,对数字电路来说是决定成败的第一步。我们目前常说的晶振都是石英晶体振荡器或者石英晶体谐振器

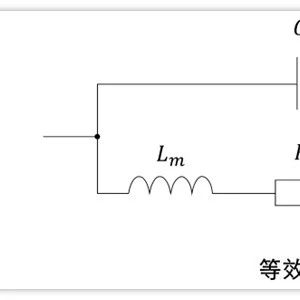

晶振的等效电路模型

上次说明了晶体谐振器的结构,这一节就来聊聊晶体的等效电路模型。晶振的等效模型从上一节内容知道,晶振工作时,内部是真的在“振动”的,是机械振动,振动的同时两端会输出对应频率的振动电压,这个电压非常的精确并且稳定,所以我们经常用作时钟信号。与此同时,我们发现晶振在谐振时跟下面的这个电路非常的相似

过孔不要上焊盘多处多余过孔只有一个层连接,造成天线报错焊盘不要从长边出线电源输出电路过孔打到最后一个电容后方多处电源走线没加粗,注意电源走线加粗晶振尽量缩短走线,打孔包地,走线尽量类似差分变压器除差分以外所有走线加粗到20mil以上变压器下

扫码关注

扫码关注