- 全部

- 默认排序

在PCB设计中,时钟信号是极为关键的敏感信号,若设置不当很容易干扰到系统稳定,电磁干扰更加严重。所以工程师必须慎重对待时钟信号,遵循其高频特性和对时序的严格要求,确保其布局布线顺利。1、减少过孔数量时钟线上应尽量减少过孔的使用,因为过孔会增

作为嵌入式系统的代表,51单片机应用广泛,其正常运作依赖稳定而精确的时钟信号,要想信号稳定,就离不开时钟振荡电路,它决定了单片机的执行速度及同步操作的时序。51单片机的时钟振荡电路可分为内部和外部时钟振荡方式,以此满足不同需求。1、内部振荡

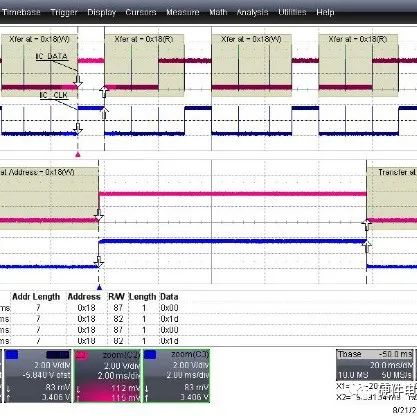

IIC接口—规范硬件信号测试1.测试指标说明 IIC总线根据时钟速率的不同分标准模式、快速模式和高速模式三种,测试中需根据实测的结果选择相应的测试指标作为判断的依据。测试内容主要包括以下两个方面: 信号完整性:SCL、SDA; 信号时序:tHD;STA、tSU;STO、tSU;D

DDR是当前最常用的存储器设计技术之一,其高速、低功耗的特性满足了众多消费者的需求。但随着传输速度的加快,DDR的设计验证难度呈指数上升。对仿真工程师来说,DDR的高速率很容易引起一系列信号完整性问题,引发包括时序冲突、协议背离、时钟抖动及

可编程逻辑器件是一种集成电路,可根据用户的需求和编程指令来执行特定的逻辑功能。这些器件在数字电子系统中扮演着重要的角色,能够实现逻辑门、组合逻辑电路以及时序逻辑电路等功能。基本结构方面,可编程逻辑器件通常由以下几个主要部分组成:输入/输出端

时钟发生器在计算机中起着非常重要的作用,主要包括以下几个方面:芯片同步:时钟发生器产生稳定的时钟信号,用于对计算机内部各个芯片的工作进行同步和时序控制,确保它们按照正确的顺序和速率进行操作。CPU同步:时钟信号被用来控制中央处理器(CPU)

在高速设计中,基于时序的考虑通常要对信号做线长匹配。对于Allegro PCB设计者来说,我们在等长的时候经常会提到X-NET,利用X-NET功能我们能够很快的计算多点拓扑结构等长长度,并且还能够计算数据组等长误差,很是方便,但是我发现在给很多学员教学的过程中,很多人不清楚这个功能的使用,那么我们这次抽时间弄成一个专题来详细的给大家讲解一下。

Altium Designer 22X-Signal功能在Altium软件等长中的使用讲师:郑振宇直播直播:2022年5月27日 周五晚8点直播简介:在高速设计中,基于时序的考虑通常要对信号做线长匹配。对于Altium PCB设计者来说,我

FPGA设计准则

直播时间:11月11日 晚8点直播结束后扫码添加助教领取直播福利直播介绍:近年来,随着国产全面化目标的推进,国产FPGA迎来了春天,Mill团队作为国内知名的FPGA研究团队,多次深度参与各大高校的FPGA课程改革和重大项目开发,本次直播,Mill团队将和大家一起聊聊FPGA设计准则及未来前景....直播大纲:(1)FPGA开发硬件思想(2)FPGA开发标准化设计流程(3)时序分析及时序分析准则直播福利:1、观看直播赠送【3套紫光CPLD板卡及配套指导手册】2、报名直播,可永久观看回放讲师介绍:缪老师(Mill),现为紫光同创FPGA原厂核心生态战略伙伴,拥有超过10年FPGA开发经验,在技术层面,曾重点参与和主导多个大型项目开发,熟悉各类高速协议应用开发:TCP/IP ,Serdes,光纤通信等。熟悉各类数字信号处理及定点技巧,独立完成纯逻辑LDPC编解码,DVB-T2等无线标准核心模块开发。凡亿教育课堂介绍:凡亿教育直播凡亿课堂是凡亿旗下开放式电子问答平台,包含免费小课、免费问答、社区、直播等版块,横跨知识分享和在线孝育两大领域。内容方面覆盖了嵌入式、单片机、电源设计、模拟技术、PCB、仿真、软件开发、Lab应用、IC设计等细分领域品类,汇聚了上百名网师,利用平台的在线教学课堂,为电子行业学生无界交流。

扫码关注

扫码关注