- 全部

- 默认排序

秒懂电感饱和

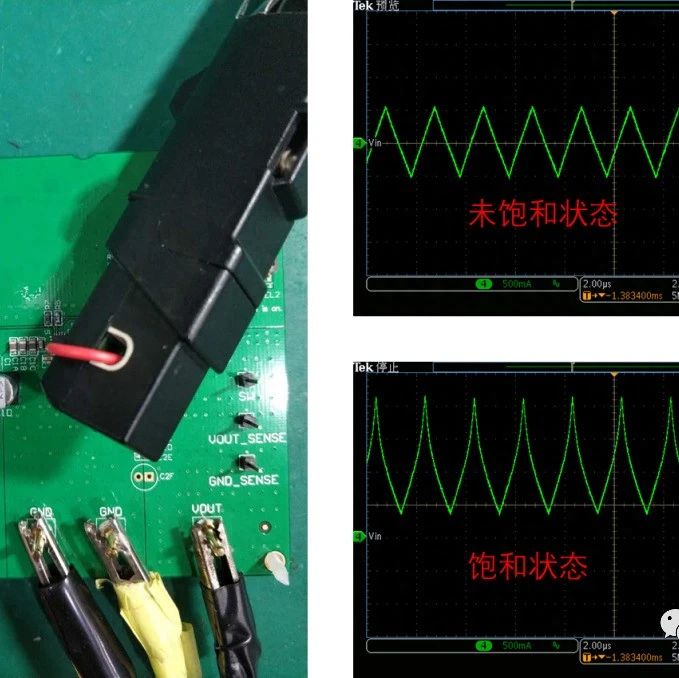

电感饱和的原因先直观的认识下什么是电感饱和,如图1:图1我们知道当图1线圈中通过电流时,线圈会产生磁场;磁芯在磁场的作用下会被磁化,其内部磁畴会慢慢旋转;当磁芯被完全磁化时,磁畴方向全部和磁场一致,即使再增加外磁场,磁芯也没有可以旋转的磁畴了,此时的电感就进入了饱和状态。从另一个角度来看,如图2所示

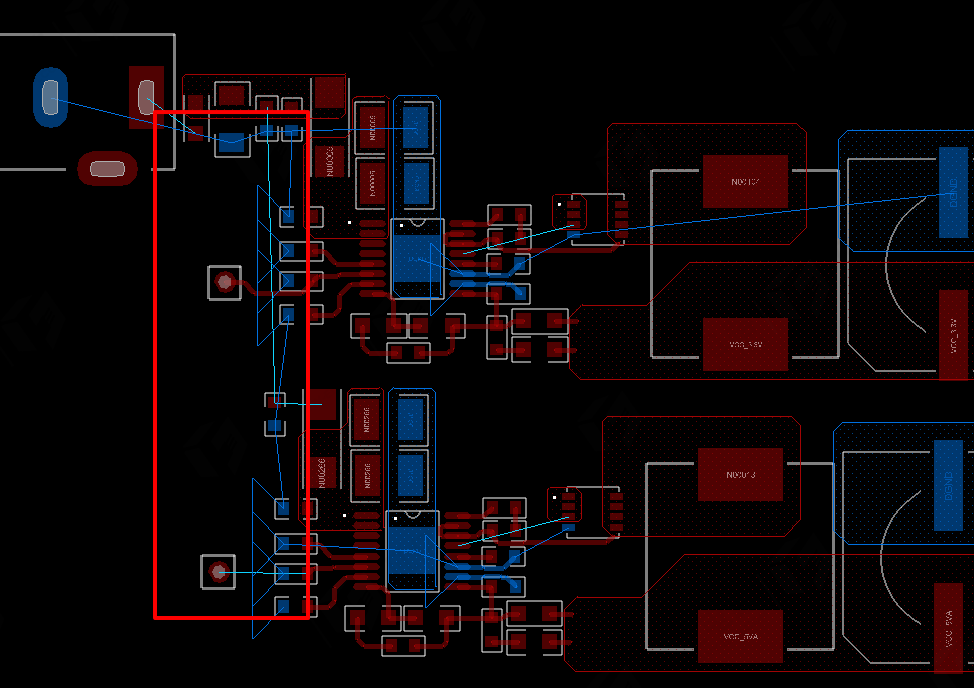

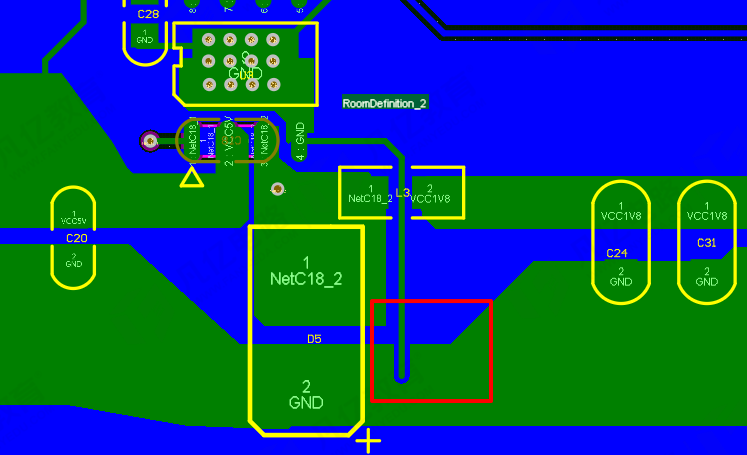

多处飞线没有连接铺铜尽量用动态铜皮电源输出路径铺铜加宽载流,按原理图顺序放置封装反馈路径应连接到电路最后端,走线即可主输出和反馈信号正确示范一路dcdc电路地信号连接通,在芯片下方打孔接地相邻电路电感应朝不同方向垂直放置问题很多,需要认真改

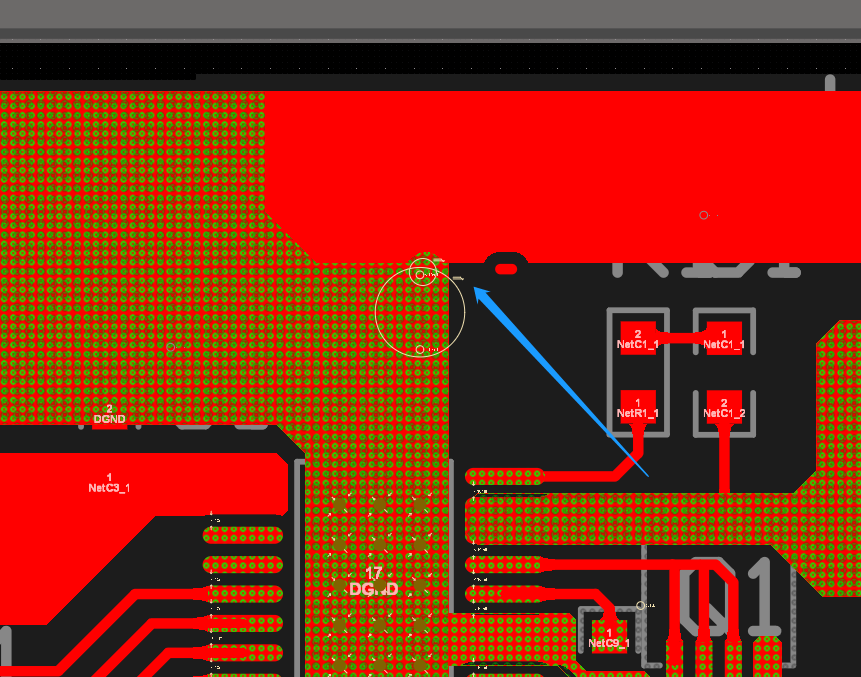

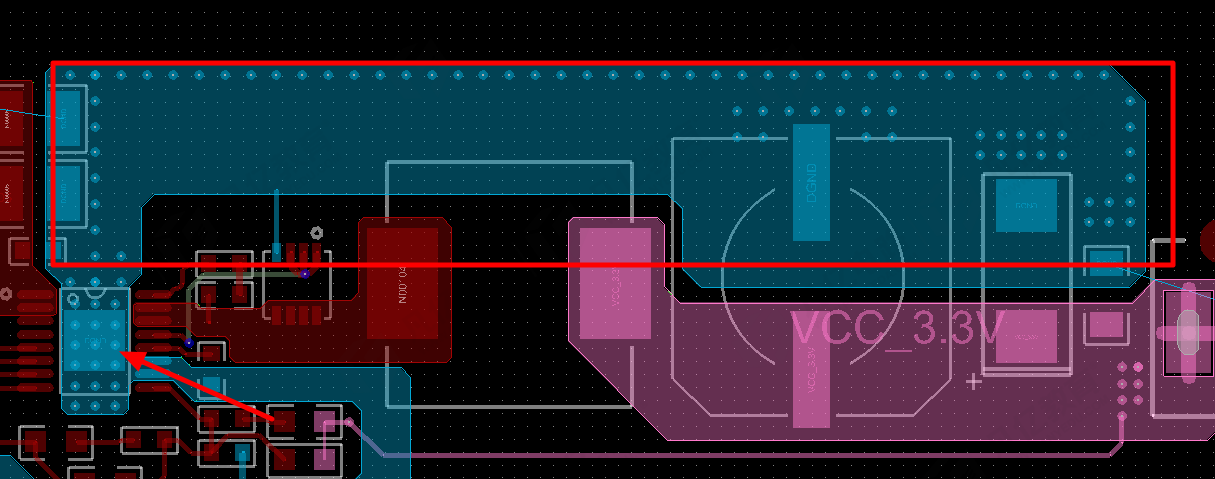

焊盘避免从长边、四角出线大电感下方同层铺铜挖空相邻电路大电感应朝不同方向垂直放置走线铺铜避免直角锐角以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.tao

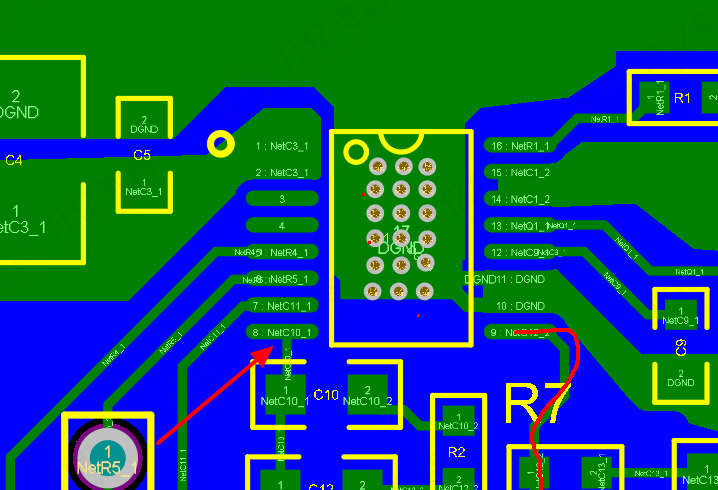

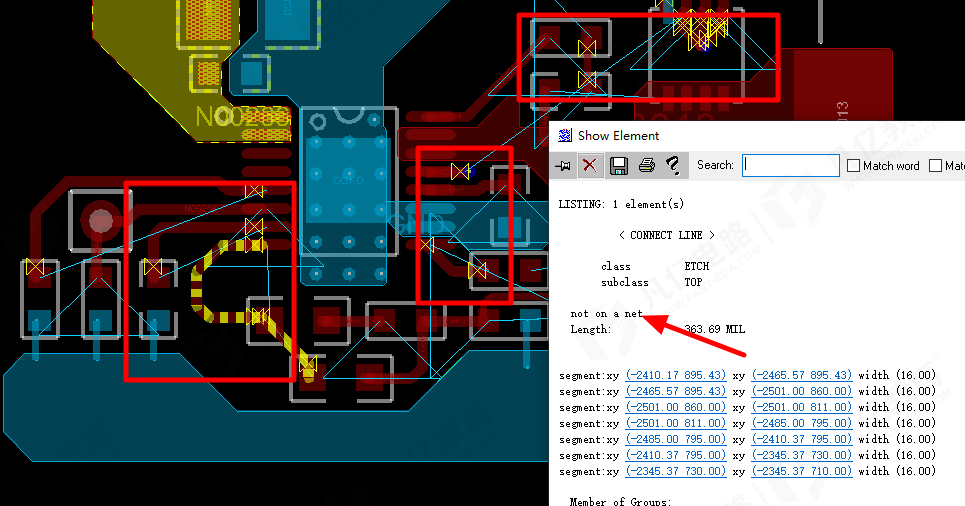

还存在开路报错,自己检查修改下:电感当前层的内部注意放置挖空区域:注意主干道器件需要整体中心对齐,都没 对齐:根据电流输出方向,电容按照先大后小的顺序布局,布局有问题:器件丝印位号没有放置整齐,要不在板外,要不就丝印重叠或者丝印覆盖焊盘了,

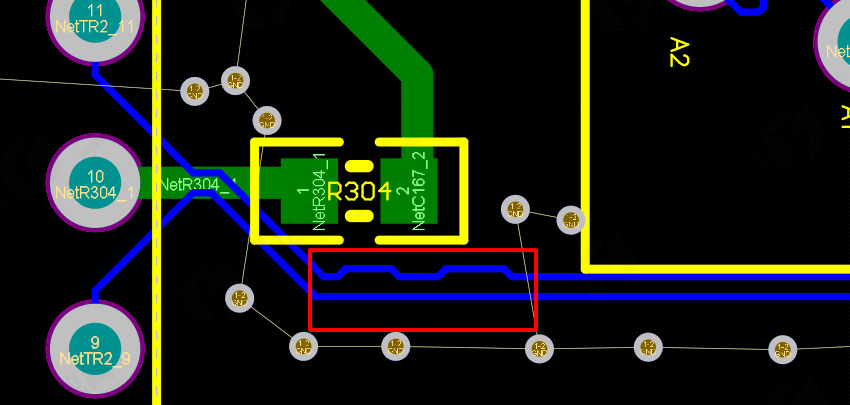

走线和铜皮没连接相邻器件尽量朝同方向,中心对齐放置一个电路GND网络连接到一起在芯片下打孔,单点接地走线在焊盘内不要拐弯,尽量不从四角出线走线不要从同层器件下方穿过按照先大后小原则放置,小电容放到电流后方走线铺铜尽量避免直角锐角以上评审报告

差分对内等长错误,按照等长绕线高度和长度不符合规范焊盘没有开窗相邻器件尽量朝相同方向整齐放置走线避免锐角对内等长误差不达要求,差分对内等长误差要求在5mil范围内以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课

多处走线没有网络造成报错多处网络未布线,反馈信号打孔链接到电路最后一个器件相邻电路大电感应朝不同方向垂直放置焊盘尽量避免从长边和四角出线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助

近年来,各大半导体厂商及跨国公司纷纷投注加码新兴技术,在此氛围下,芯片性能大幅提高,芯片迭代更新速度加快,那么哪些技术是未来芯片发展关键方向?也许苹果可以参考。据外媒报道,苹果近期正在积极与多家供应商探讨将玻璃基板技术应用在芯片开发的可行性

要求单点接地,一路dcdc电路GND焊盘都连接都芯片下方打孔大电感下方同层铺铜挖空处理同层连接多余打孔相邻电路大电感朝不同方向垂直放置多处GND网络飞线未处理,底层应大面积铺GND网络铜皮以上评审报告来源于凡亿教育90天高速PCB特训班作业

近年来,随着超大规模集成电路工艺的高速发展,芯片工作电压明显降低,功耗逐渐增高,传输信号的提升加强,促使了电路相关设计、布局布线、叠层密度等越来越大,PCB电路自然也呈现了高速、高频传输的特性,高速PCB设计已成为未来电路设计的主流方向。在

扫码关注

扫码关注