- 全部

- 默认排序

虽然说很多学员与爱好者应该都知道具体的PCB软件操作,也知道了一些基本的PCB设计规则与需要注意的事项。但是当他把整个工程或者输出文件保存了之后,在文件夹里面去进行打开,你问他这是什么文件?他看文件的后缀不一定能认识出来。所以,总的来说很多人对于AD常用文件的后缀名称它是比较陌生的了。

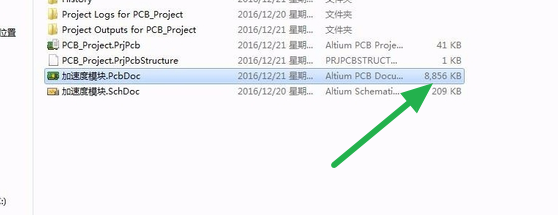

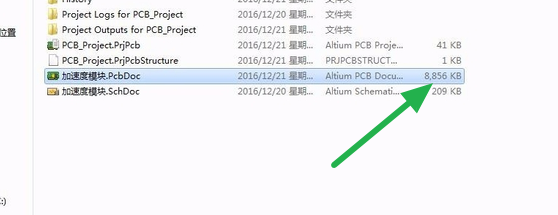

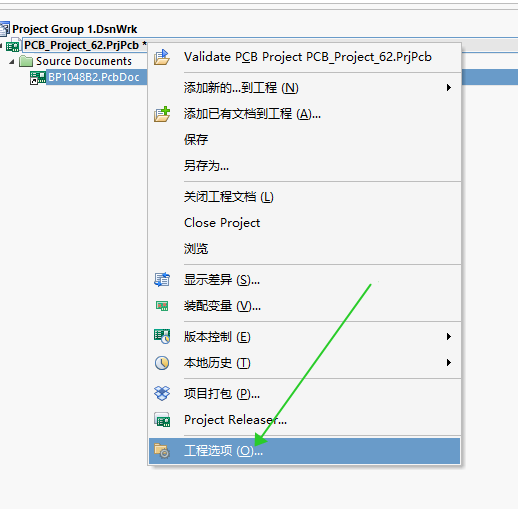

当我们设计完PCB时,去进行保存的时候,在文件夹里面看到此刻的PCB文件非常大,这是为什么呢?是不是里面还有文件什么的?其实出现这个现象最大的原因就是在PCB工程加入了中文字库。那么遇到这种情况我们如何去解决?

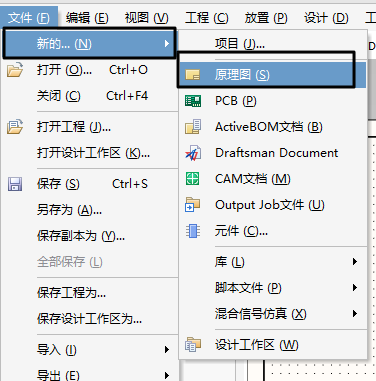

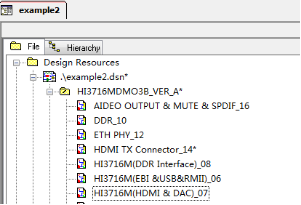

平坦式原理图是一种基础的电路图设计方法,它结构简单,所用的元器件能够在一张电路图上全部表示出来。功能模块是不能进行重复调用的,基本上每一页就是一个功能模块,不同页之间的网络用Offsheet连接,不同的页面都属于同一层次,相当于在一个电路图文件夹中,绘制平坦式原理图的方法和新建原理图方法一致

当我们设计完PCB时,然后再进行保存,在文件夹里面看到PCB文件非常大,这是为什么呢?是不是里面还有文件什么的?其实出现这个现象最大的原因就是在PCB工程加入了中文字库。那么我们的解决办法又是什么呢?

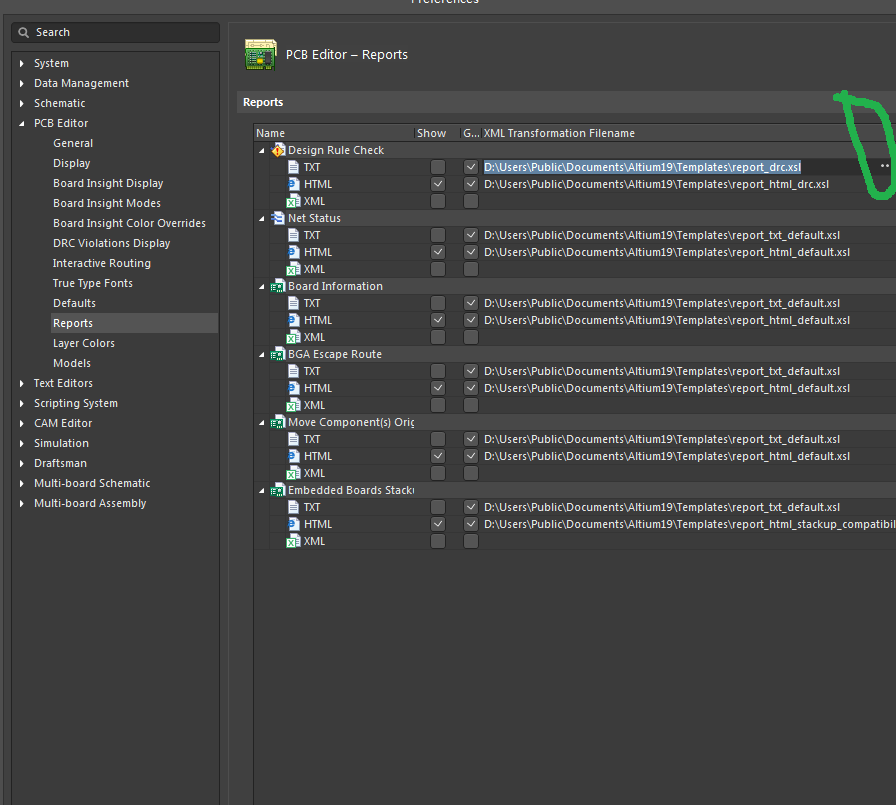

. report_drc.xsl文件的缺失;解决的方法为:复制一个report_drc.xsl文件,放置到对应的文件夹下就可以

答:使用Orcad软件进行输出Allegro第一方网表时,弹出如图3-72所示的界面,这个是表示原理图有错误,不满足Allegro软件的要求,不能输出网表, 图3-72 输出Allegro网表报错示意图在输出Allegro第一方网表弹出这个界面,我们需要找到如图3-72所示的netlist.log这个文件,原理图中存在的错误在这有详细的描述,这个文件一般存储于输出网表的那个文件夹下,用写字本文件打开此文件,如图3-73所示,将列表中所列的错误一一解决掉,即可输出网表文件了。

答:一种基础的电路图设计方法,结构简单,所用的元件能够在一张电路图上全部表示出来。功能模块是不能进行重复调用的,基本上每一页就是一个功能模块,不同页之间的网络连接用off-Page Connector,不同的页面都属于同一层次,相当于在 1 个电路图文件夹中,如图3-102所示: 图3-102 平坦式原理图示意平坦式原理图绘制在我们的日常处理中用的非常多,它的优点有如下几个:Ø 设计简单,操作容易,对结构的理解更容易;Ø 逻辑关系清楚,非常直观的表达电路

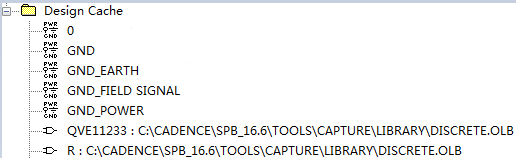

答:我们在使用Orcad软件进行原理图绘制的时候,会在整个工程文件的下方可以看到一个类似于文件夹的东西,下面是“Design Cache”,点开这个文件夹前面的+号,将文件夹进行展开,如图3-230所示,里面全部都是原理图封装库文件,而却是没有办法进行打开编辑的,具体这个Design Cache的功能是什么,我们这里呢给大家做一一的解释说明,具体如下, 图3-230 Design Cache展开示意图首先,这个Design Cache文件夹里面所包含的内容就是当

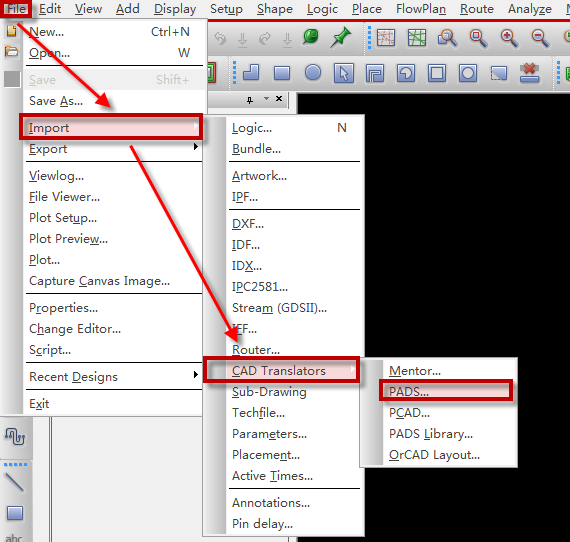

答:Pads封装导入到Allegro,一般先是通过Pads PCB转Allegro PCB,转换完成后,将封装导出,再逐个对PCB封装进行检查修改,修改为标准可用的封装。第一步,将Pads PCB导出ASC文件,打开PCB点击文件-导出选项,在弹出的对话框中设置好导出文件的文件夹和文件名,然后点击保存,如图4-78所示; 图4-78 导出asc文件示意图第二步,在弹出的对话框中勾选所有内容,格式中选择PADS Layout V2007选项,然后点击确定,就能生成ASC文件,

扫码关注

扫码关注