- 全部

- 默认排序

PADS Logic软件提供了元件库管理、原理图设计、原理图符号创建向导、元器件浏览和检索、物料清单输出、ECO同步和网表输出等功能,是一个界面友好、操作简单且功能齐全的原理图设计软件。

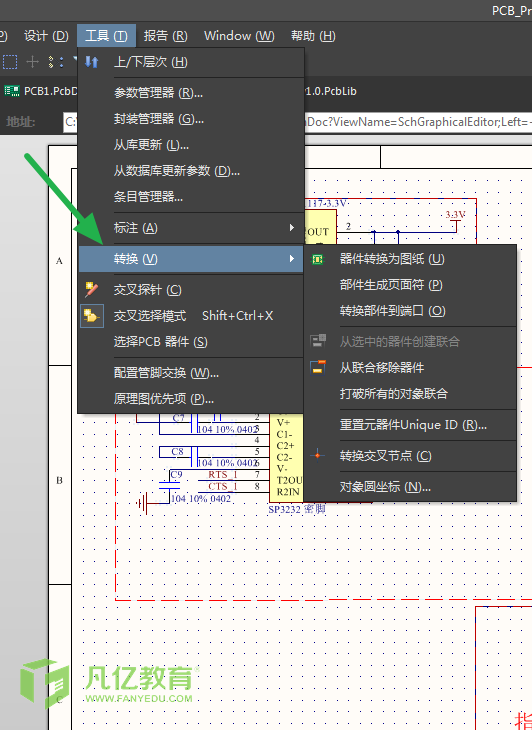

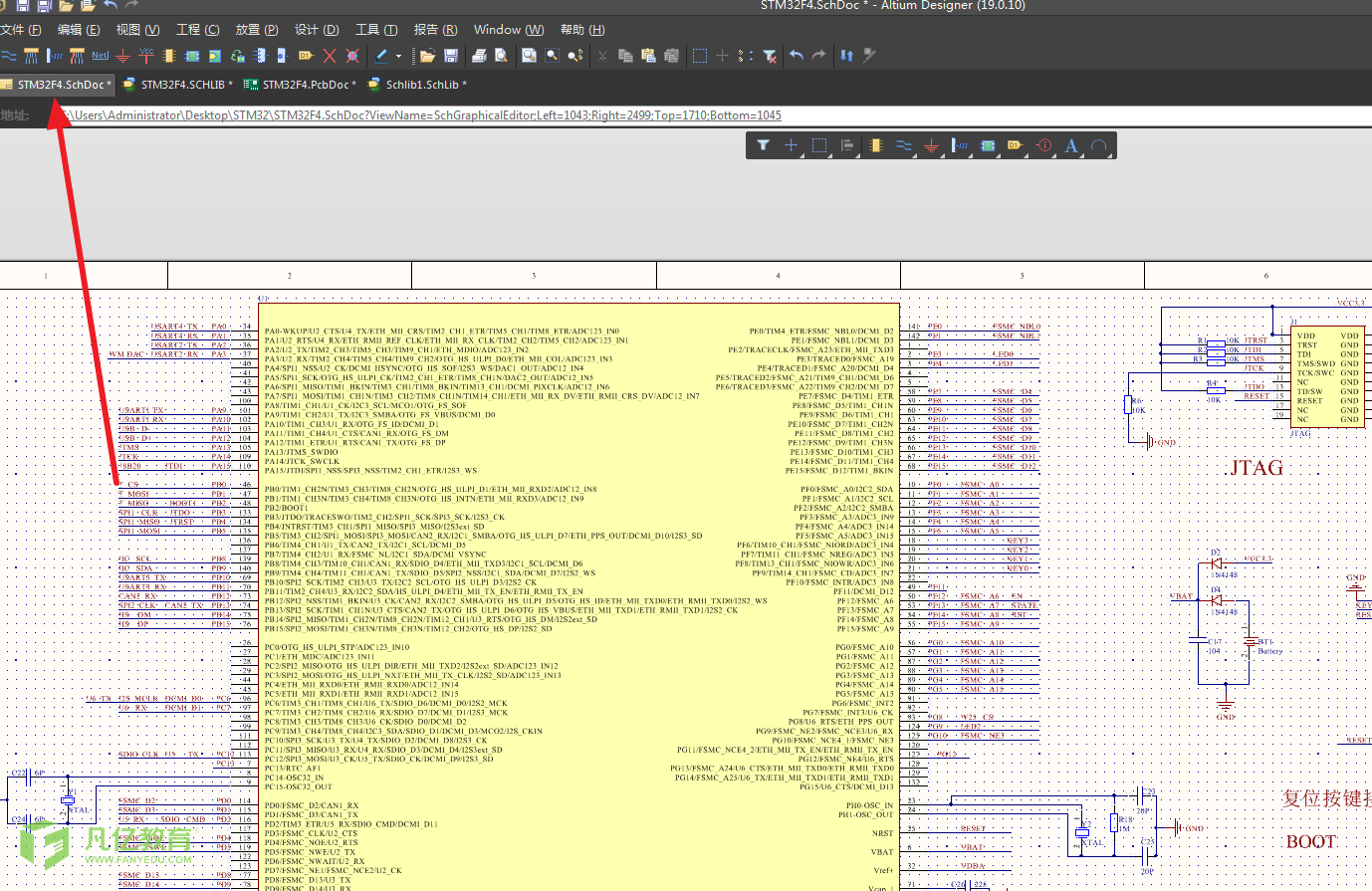

当我们在绘制原理图的时候,电路相同的模块可以进行复制粘贴,得到多个相同的原理图图纸,但是如果直接进行文件复制粘贴会出现ID相同的情况。这个unique ID在原理图和pcb中就是相当于这个元件的唯一身份许可证一样的,所以不可能两个元件之间相同。那么,在我们操作不当的时候造成ID相同怎么办呢?我们就需要对unique id进行复位。

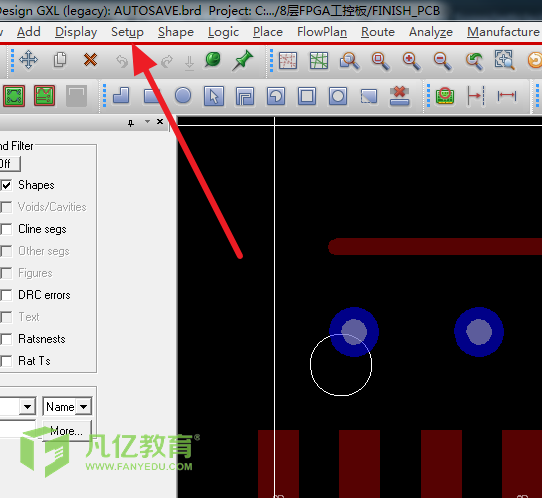

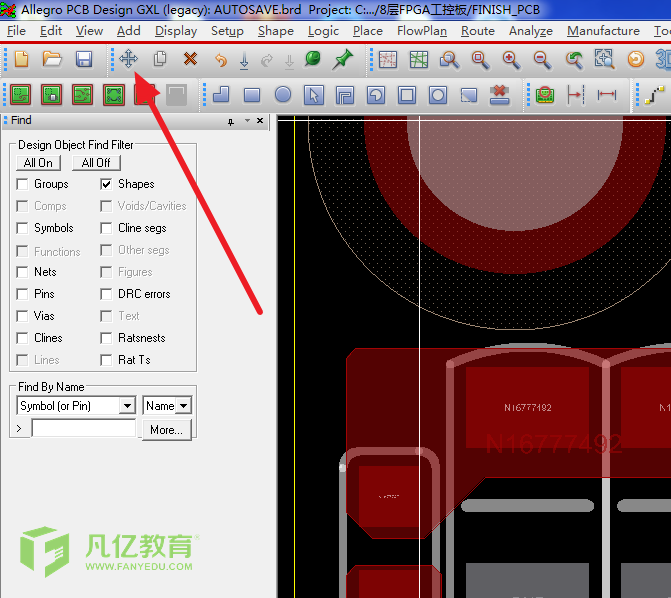

在进行pcb设计的时候,我们经常会进行切换走线的线宽这一项操作。而我们的Allegro 软件中是默认记忆走线线宽的。这个的意思就是我们在连接下一个网络的时候,走线会默认使用连接上一个网络的线宽。那么,这个时候我们就会遇到一个很头疼的问题,就

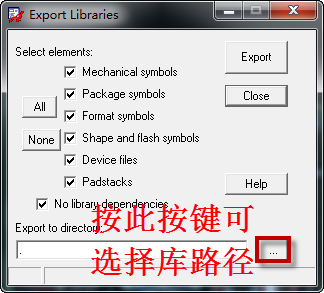

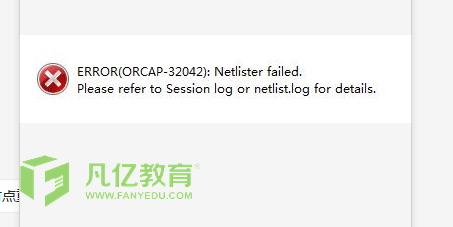

我们在进行原理图设计的时候,完成之后就需要去进行网表的导出,然后在pcb中去进行设计。有很多学员在原理图导出网表的这一操作中会出现各种各样的报错,那么今天我们就来看看最常见的一项导出网表的报错的解决办法,即”Netlister failed”的报错。

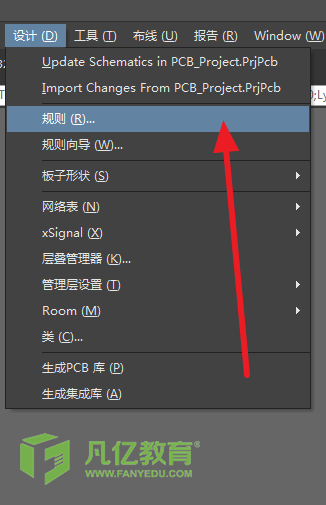

我们进行PCB设计的时候,总会遇到再进行了敷铜操作,我们如何去更改对应网络的焊盘与铜皮之间的连接方式?我们首先可以来分析一下焊盘的连接方式有几种,分别为哪几种?运用AD进行PCB设计的人都清楚,焊盘的连接方式为三种:一个是全连接,一个是十字连接也就是我们经常所说的花焊盘连接,还有一个就是不连接意思就是不进行设置。

在我们设计完原理图模板之后,对于其原理图模板也进行了保存。我们就需要对于其模板的调用了,我们应该怎么将这个模板应用到我们的原理图中来,这样的一个操作过程又是怎么样的?

扫码关注

扫码关注