- 全部

- 默认排序

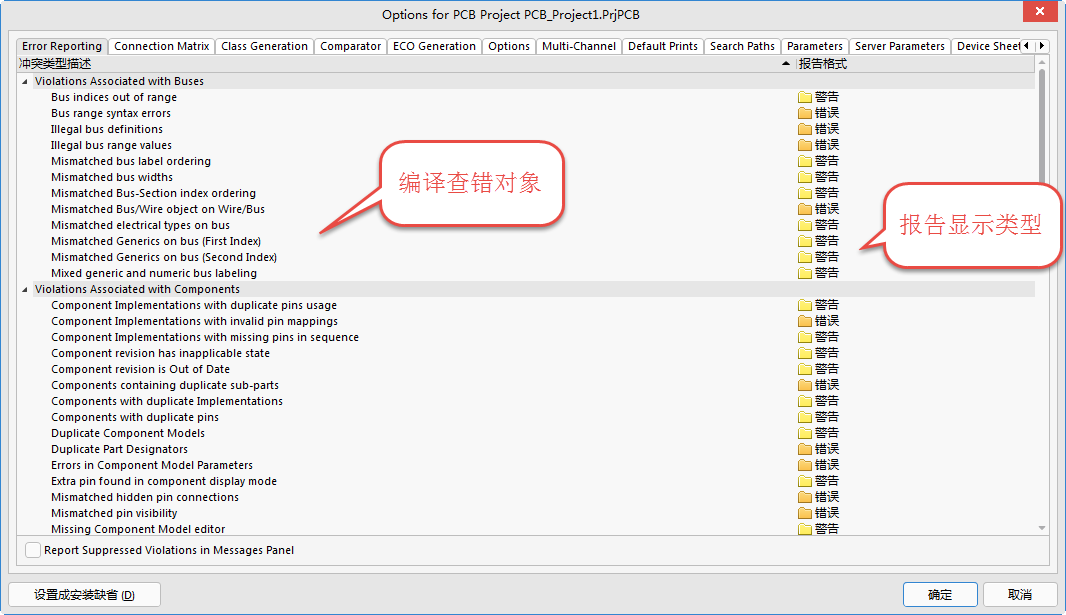

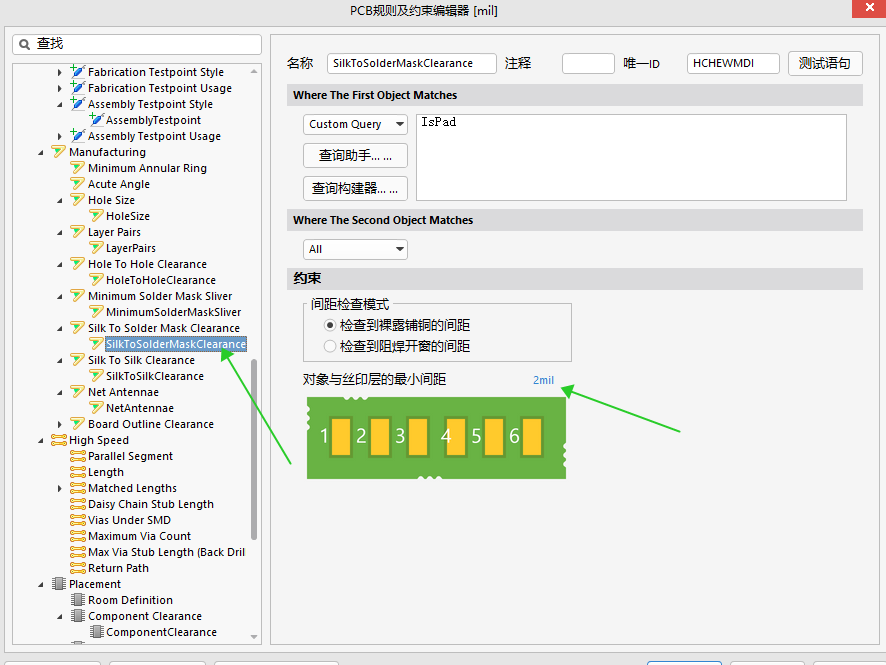

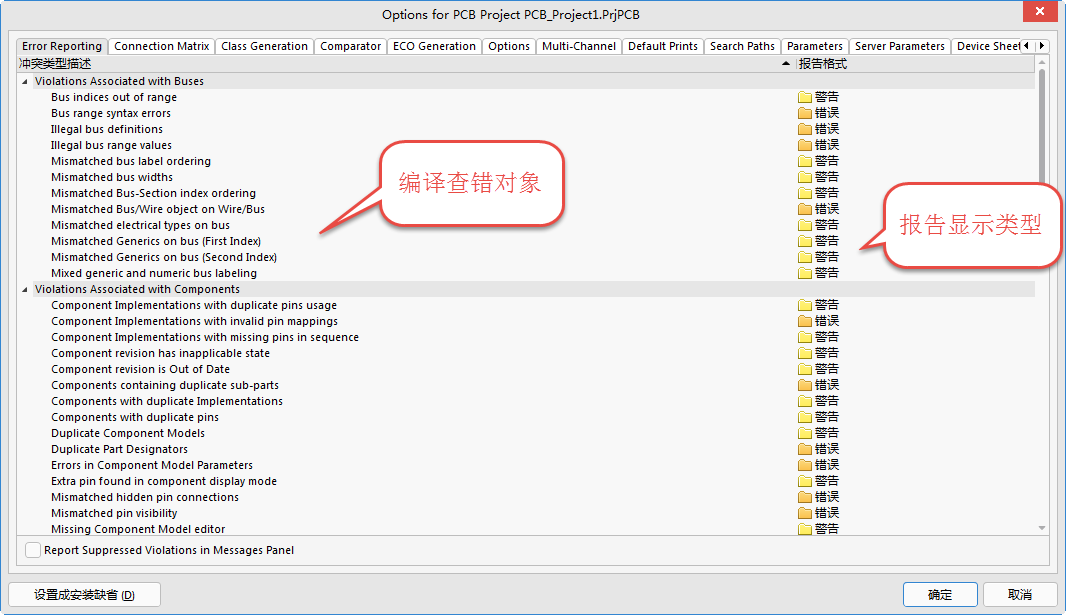

在设计完原理图之后、设计PCB之前,工程师可以利用软件自带的ERC功能对常规的一些电气性能进行检查,避免一些常规性错误和查漏补缺,以及为正确完整地导入PCB进行电路设计做准备。

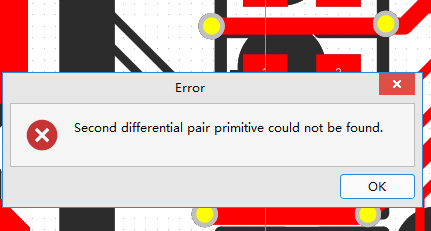

AD差分走线时出现Second differential pair primitive could not be found报错

在绘制层次原理图后进行编译时,有时会遇见弹出报错“XXX.Sch Compiler Sheet-Entry XX not matched to port”的情况,那么为什么会出现此报错,以及应该如何解决呢?

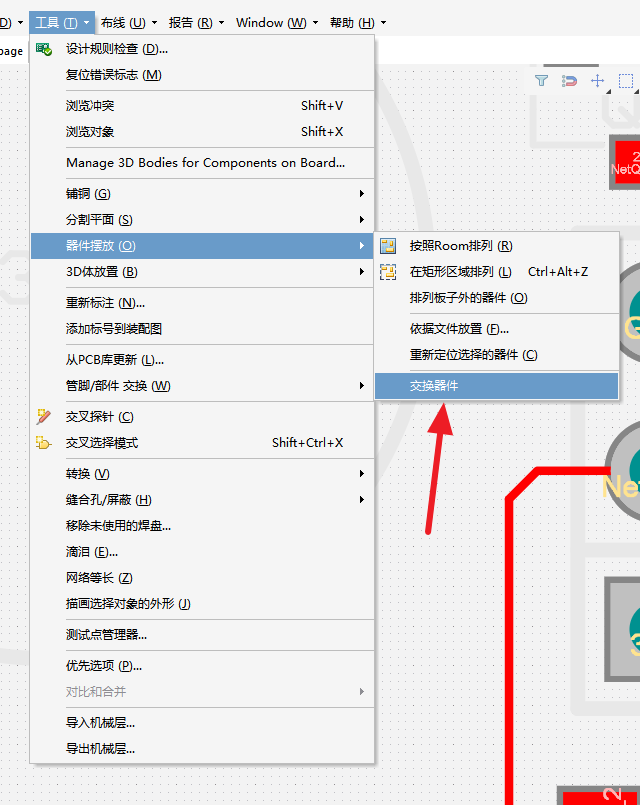

进行PCB设计的时候,每当有两个元件相隔很远,但是又想对于这两个器件进行位置的互换。这种情况多适于PCB设计完成之后,想要将两个元器件进行位置的交换,但是直接拖动进行位置互换的话又会引起非常多的报错,导致后期还要修改很久。

在设计完原理图之后、设计PCB之前,工程师可以利用软件自带的ERC功能对常规的一些电气性能进行检查,避免一些常规性错误和查漏补缺,以及为正确完整地导入PCB进行电路设计做准备。

扫码关注

扫码关注