- 全部

- 默认排序

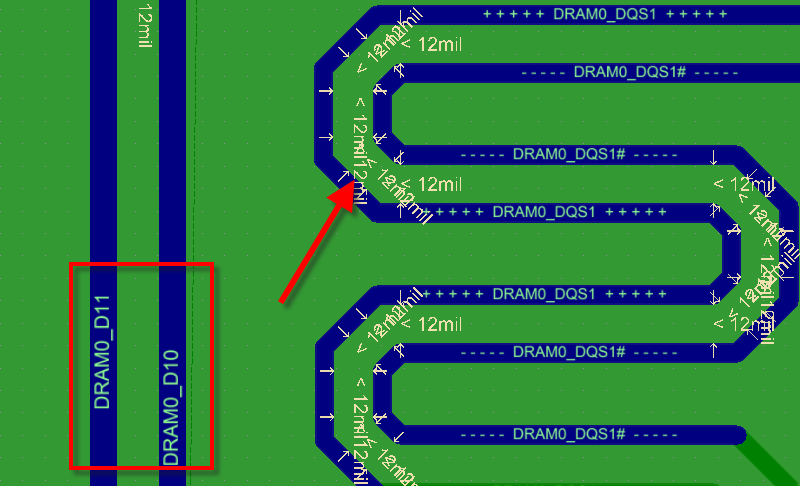

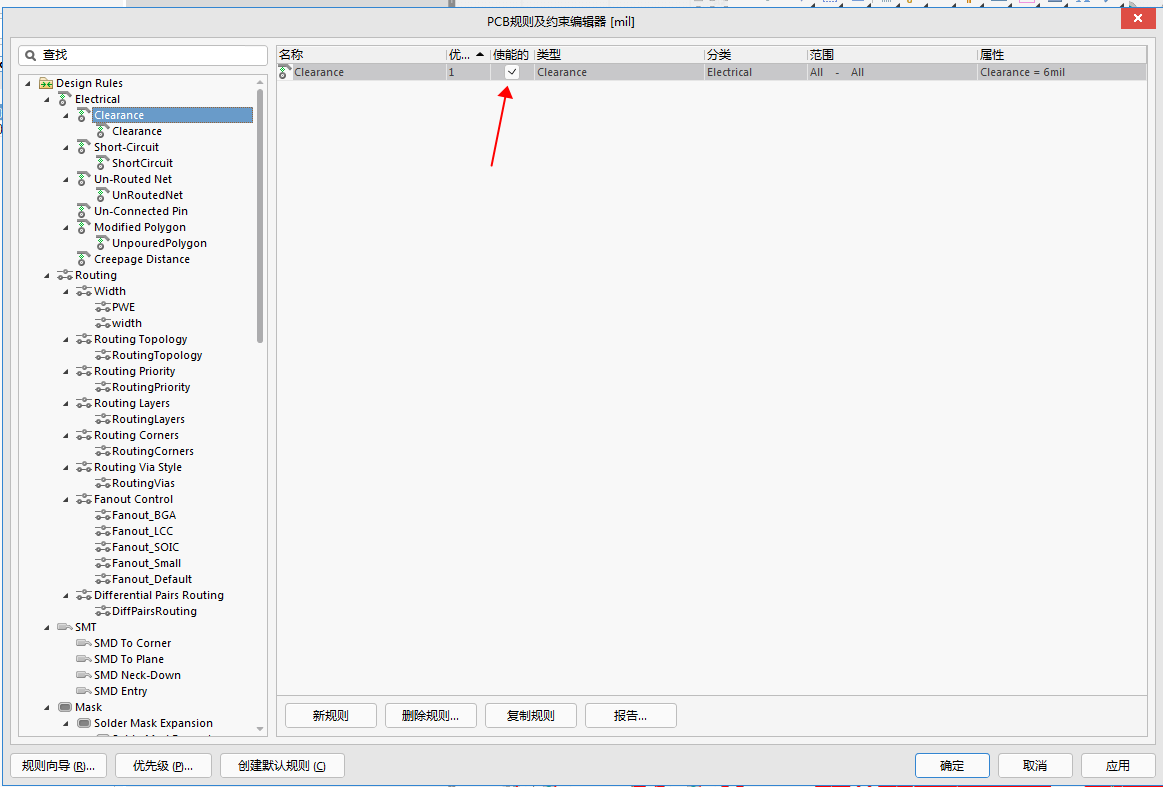

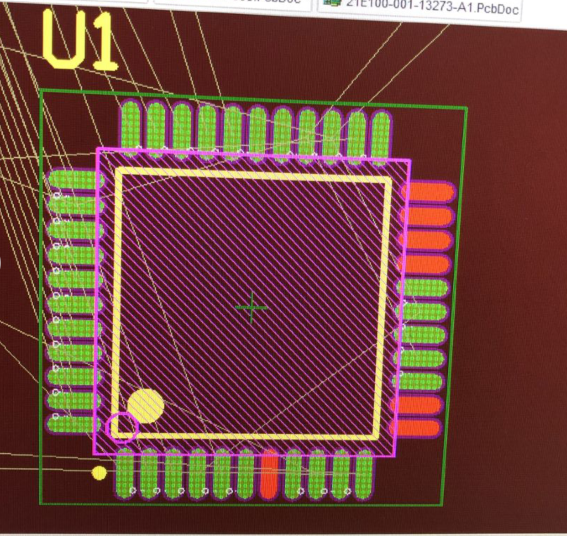

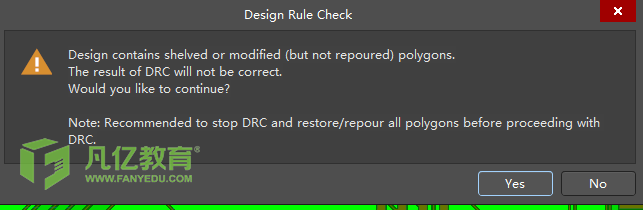

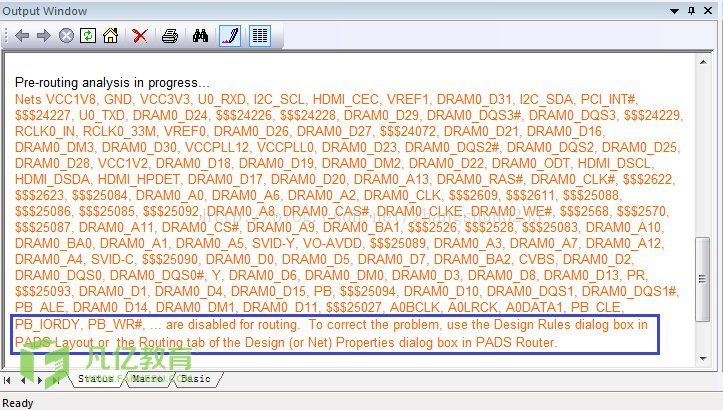

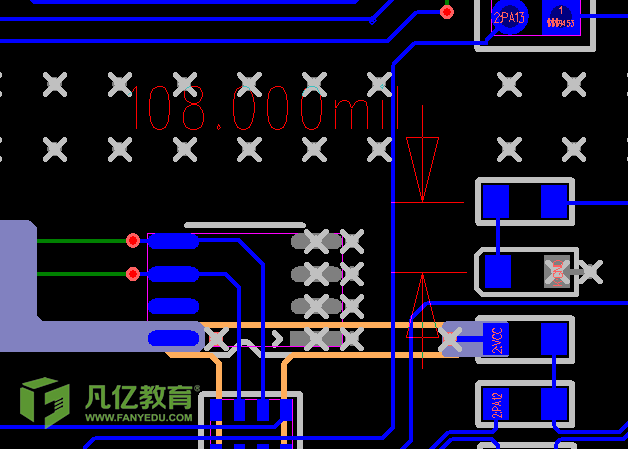

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

我们在根据PCB板的要求,在规则编辑器里面加入了很多对应的规则。比如:间距规则,线宽规则,短路等都是非常重要的电气规则规则,及其重要性是非常重要。

在layout中布局时,经常需要测量间距,有时候会发现测量的间距有误差并且我们在layout中出cam文件时,有时会弹出钻孔精度报错,其实都是因为我们的测量精度设置有误

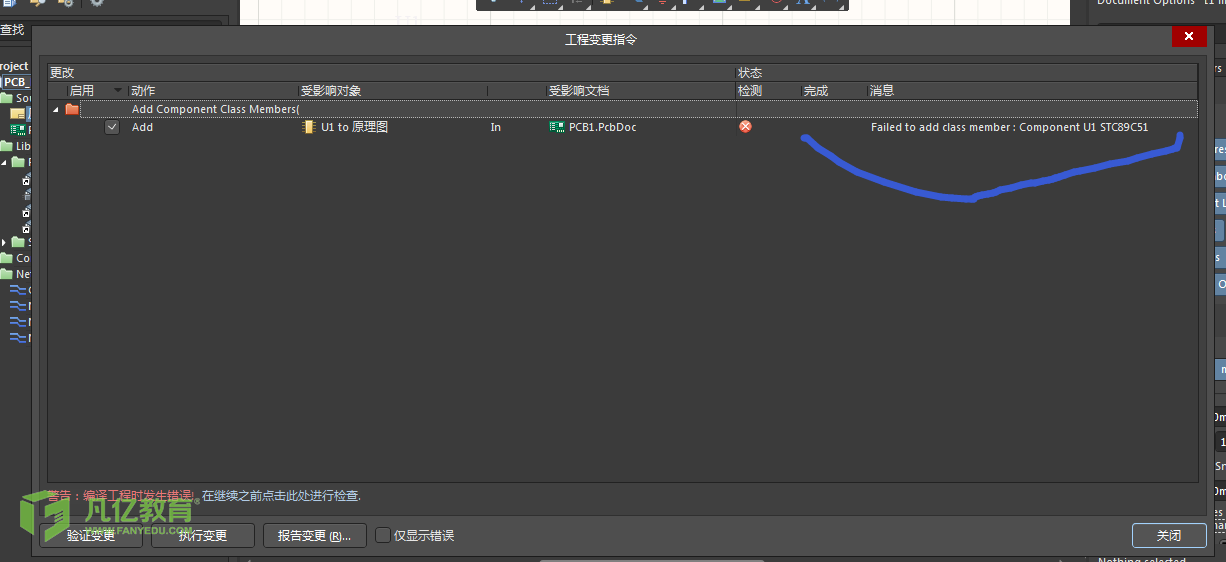

我们在进行到原理图导入到PCB中会出现各种各样的报错,之前的几种常见的报错我们也已经写过其对应的教程了,那么我们今天来看下出现“Failed to add class member”的这一项错误的解决办法。

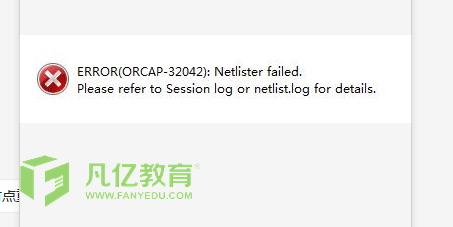

我们在进行原理图设计的时候,完成之后就需要去进行网表的导出,然后在pcb中去进行设计。有很多学员在原理图导出网表的这一操作中会出现各种各样的报错,那么今天我们就来看看最常见的一项导出网表的报错的解决办法,即”Netlister failed”的报错。

扫码关注

扫码关注