- 全部

- 默认排序

1、LMK04368MPAPTEP 是一款适用于航天应用、支持 JEDEC JESD204B/C 的高性能时钟调节器。PLL2 可以配置 14 个时钟输出以驱动 7 个 JESD204B/C 转换器或其他逻辑器件(使用器件和 SYSREF

本文要点将 PDN阻抗设计为目标值有助于确保设计的电源稳定性。PDN 目标阻抗在一定程度上会决定 PDN 上测得的任何电压波动。确定目标阻抗需要考虑 PDN 上允许的电压波动、输出信号上允许的抖动,或将两者都考虑在内。阻抗可能是用于普遍概括电子学所有领域信号行为的一项指标。在 PCB 设计中设计具体

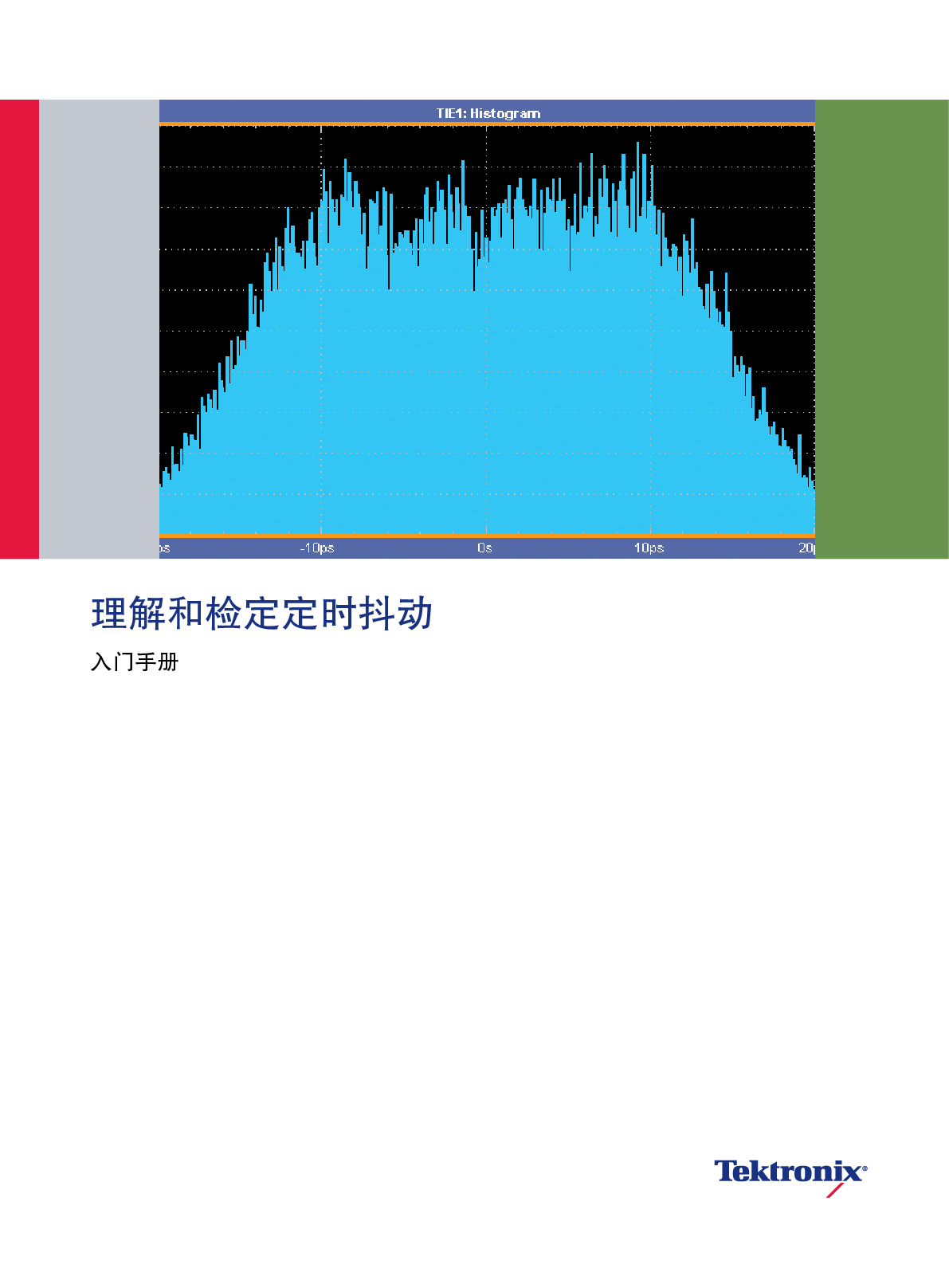

DDR是当前最常用的存储器设计技术之一,其高速、低功耗的特性满足了众多消费者的需求。但随着传输速度的加快,DDR的设计验证难度呈指数上升。对仿真工程师来说,DDR的高速率很容易引起一系列信号完整性问题,引发包括时序冲突、协议背离、时钟抖动及

扫码关注

扫码关注