- 全部

- 默认排序

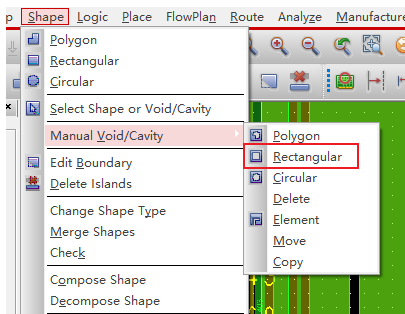

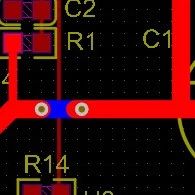

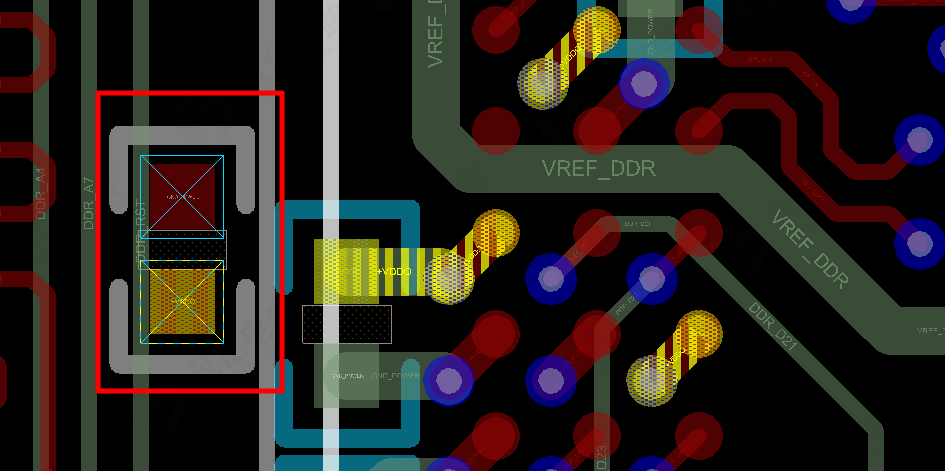

在PCB设计中,铜皮是电路板布局布线的重要载体,但有时候要根据项目需求对其进行切割或挖空,以此满足特定需求,那么如何操作?1、准备工作在进行切割/挖空操作前,先确保是否打开Allegro并加载器相关的PCB文件。2、Rectangular在

No.1:资料输入阶段在流程上接收到的资料是否齐全(包括:原理图、*.brd文件、料单、PCB设计说明以及PCB设计或更改要求、标准化要求说明、工艺设计说明等文件)。确认PCB模板是最新的。时钟器件布局是否合理。确认模板的定位器件位置无误。PCB设计说明以及PCB设计或更改要求、标准化是否明确。确认

有器件没有布局布线滤波电容放置不均匀,应尽量1-2个焊盘一个电容器件丝印干涉,丝印不要重叠保持一定间距以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.ta

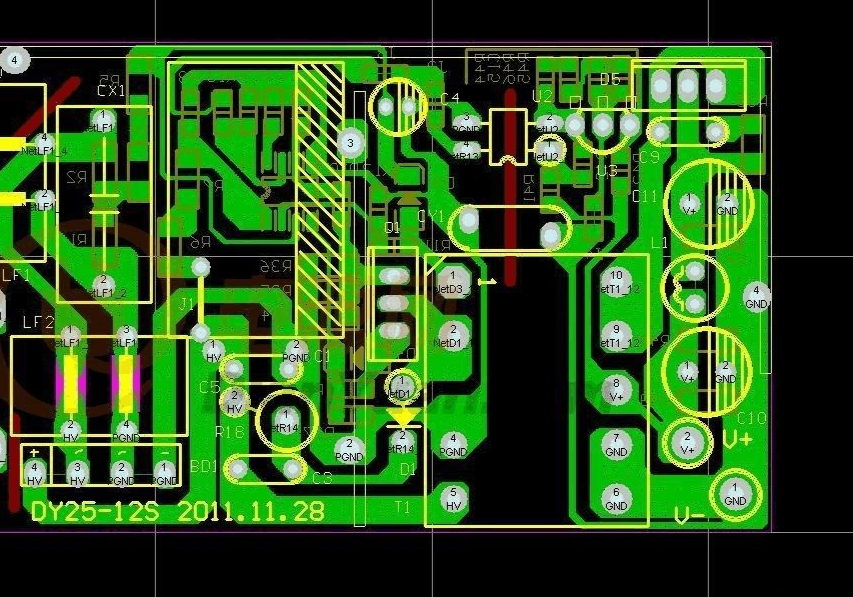

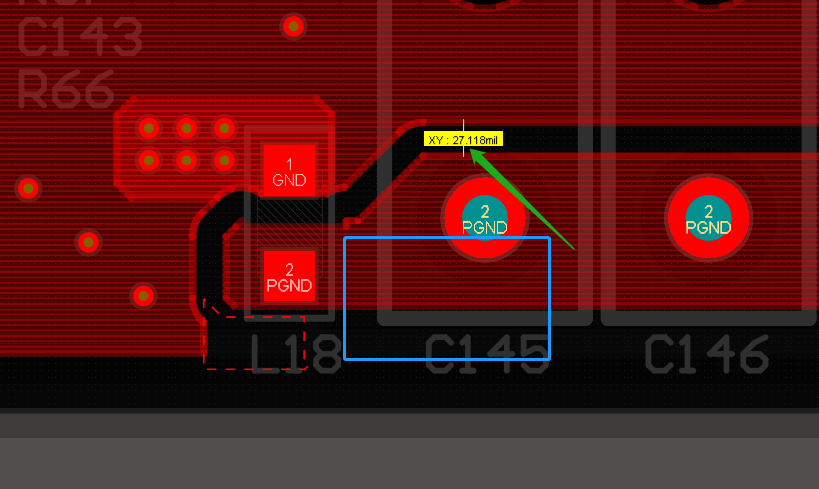

差分对内等长绕线不符合规范差分对布线线宽不一致,会导致阻抗不一致多个器件没有布局布线内层电源和地没有铜皮,导致电源和地都是开路变压器前后电源线宽不一致,变压器除差分外所有走线加粗到20mil时钟信号没有布线,应包地打孔连接rx,tx应建立等

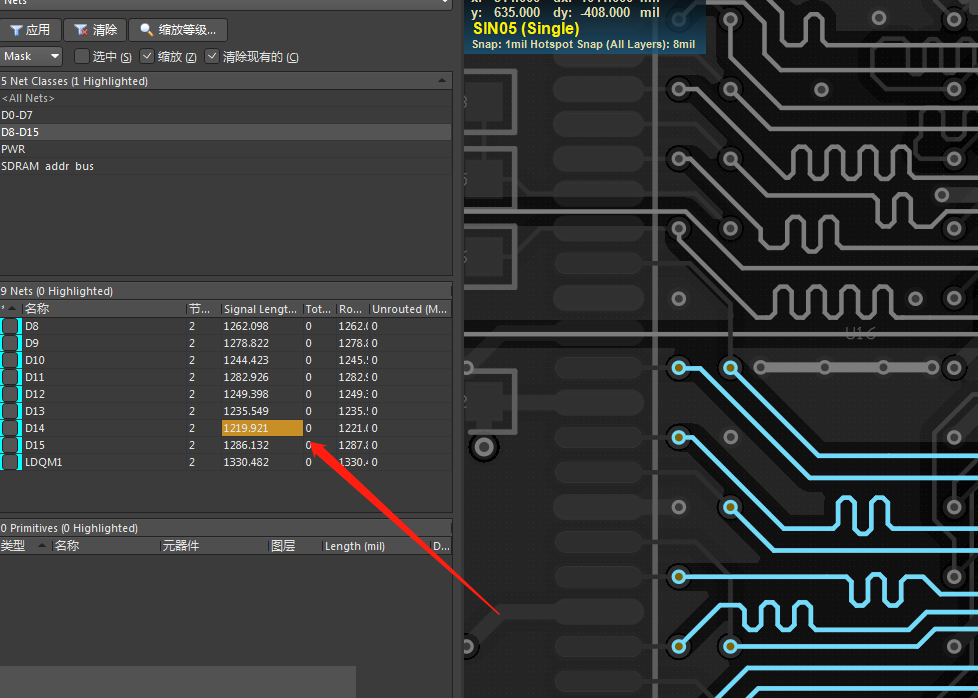

组内等长误差还存在报错:自己注意修改下等长,让组内误差没有报错。以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?s

4、结构体成员的布局很多编译器有“使结构体字,双字或四字对齐”的选项。但是,还是需要改善结构体成员的对齐,有些编译器可能分配给结构体成员空间的顺序与他们声明的不同。但是,有些编译器并不提供这些功能,或者效果不好。所以,要在付出最少代价的情况下实现最好的结构体和结构体成员对齐,建议采取下列方法:(1)

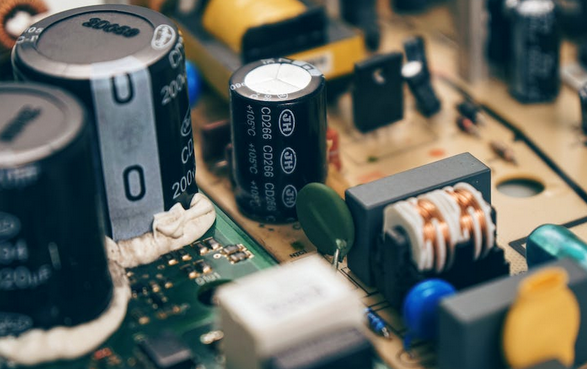

高功率电源的设计中,变压器起到了电能的传递与转换的重要作用。变压器下方的走线设计不仅涉及到电路的功率传输效率,还与电磁兼容性(EMC)、热管理以及电路的可靠性密切相关。1. 走线布局在进行变压器下方走线设计时,合理的走线布局是关键。应该避免

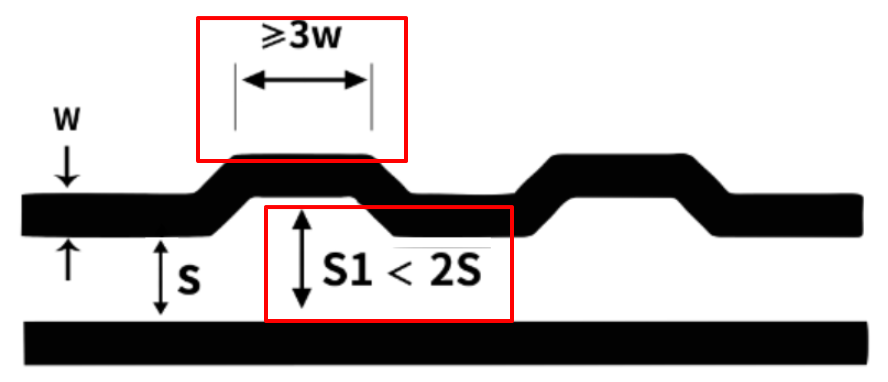

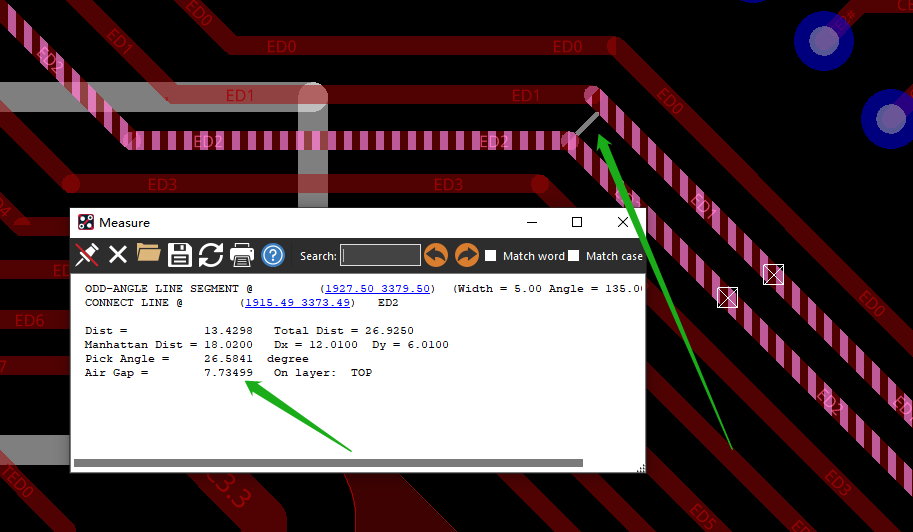

注意数据线之间等长需要满足3W间距,后期自己检查一下其他组是否满足2.注意模拟信号尽量一字型布局3.跨接间距最少要保证1.5mm,一般建议2mm,有器件的地方可以不满足4.电源输出打孔要打在最后一个电容后面5.反馈信号需要走10mil的线进

跨接器件旁边尽量多打地过孔,间距最少1.5mm,建议2mm,有器件的地方可以不满足2.网口差分需要进行对内等长,误差5mil3.模拟信号需要一字型布局,走线加粗4.注意过孔不要上焊盘5.反馈信号走线需要加粗到10mil6.注意确认一下此处是

在PCB Layout布局布线过程中,很多电子工程师都会面临不同的地线(GND)处理,这是因为降低电路之间的互相干扰,一般会引入不同的GND地线,作为不同功能电路的0V参考点,形成不同的电流回路,那么你知道有哪些地线吗?地线是电路中的一个参

扫码关注

扫码关注