- 全部

- 默认排序

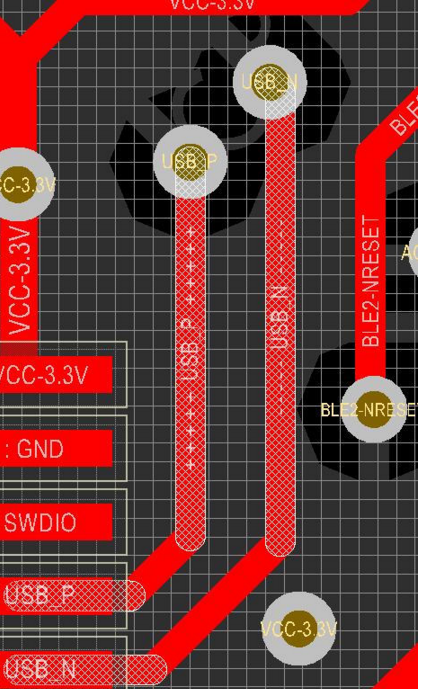

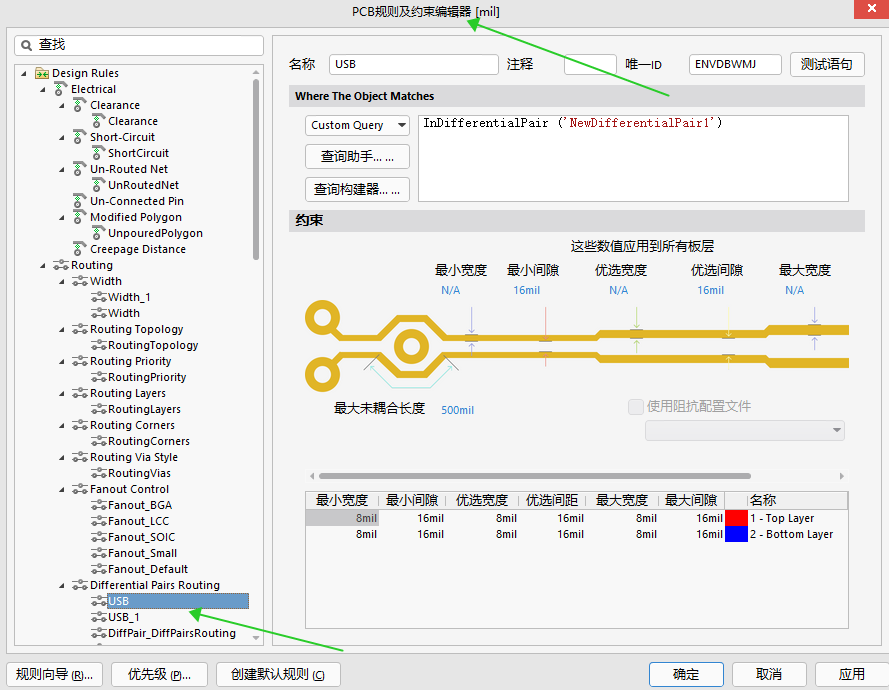

本视频采用我们的Altium designer 19软件进行我们的差分走线的等长的处理,同时简单介绍我们的差分走线和等长走线时候的注意事项,以及我们的等长目标线的确定和我们的等长的一些快捷键的小技巧。

★掌握PCB设计常用的设计技巧★熟悉PCB设计的整体流程★交互式模块化快速布局★掌握各个PCB模块的布局布线要点★掌握电源平面分割的方法及要点★掌握差分走线的设计方法★了解常见EMC的PCB处理方法

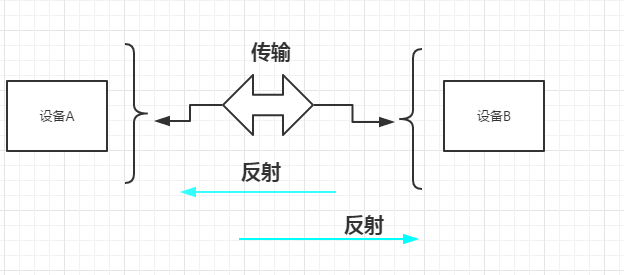

差分走线,信号换层过孔数量,等长长度把控,阻抗控制要求,跨分割的损耗,走线拐角的位置形状,绕线方式对应的插损和回损,布局不妥当造成的一系列串扰和叠层串扰,布局不恰当操作焊盘存在的stub。

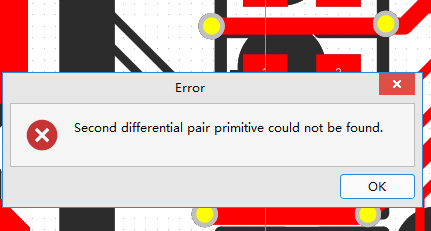

AD差分走线时出现Second differential pair primitive could not be found报错

电子设计当中,经常用到差分走线,如USB的D+与D-差分信号,HDMI的数据差分与时钟差分等。虽然现在很多设计者都是在PCB中添加差分,但是还是有许多设计者习惯在PCB中就添加好差分。那么,如何在原理图中添加差分标识呢?

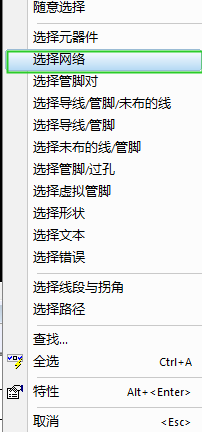

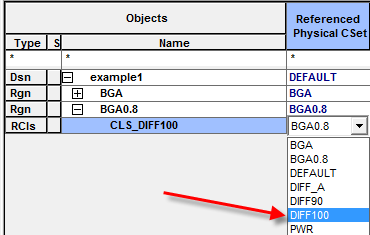

答:在进行PCB设计布线时,优先是根据阻抗线宽进行走线设计,但是在BGA区域为了方便出线,一般会添加区域走线规则,当然能够满足阻抗线宽的情况下,尽量使用阻抗线宽。这里,我们讲解一下,如何设置可以让差分阻抗线宽的优先级高于区域规则线宽,操作如下所示:

扫码关注

扫码关注