- 全部

- 默认排序

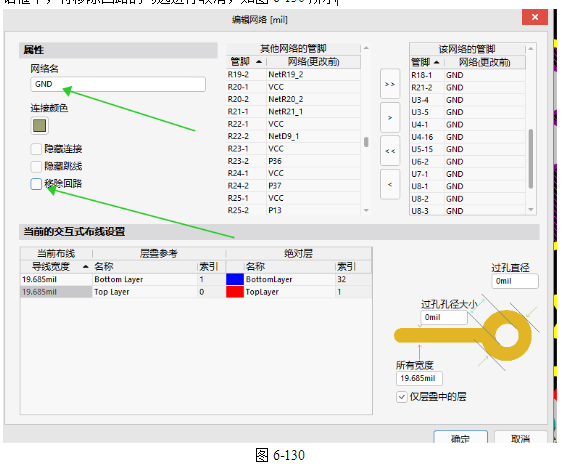

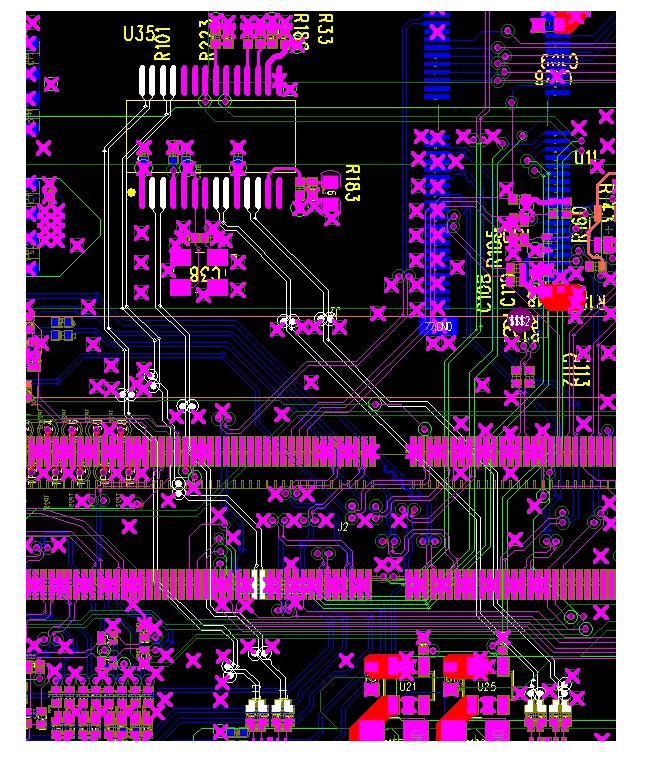

在pcb设计中由于不允许出现回路,因此会对网络进行自动移除回路的设置。然而在地线中因为要对某些信号线或差分线进行立体包地,所以会对地线单独设置不自动移除回路

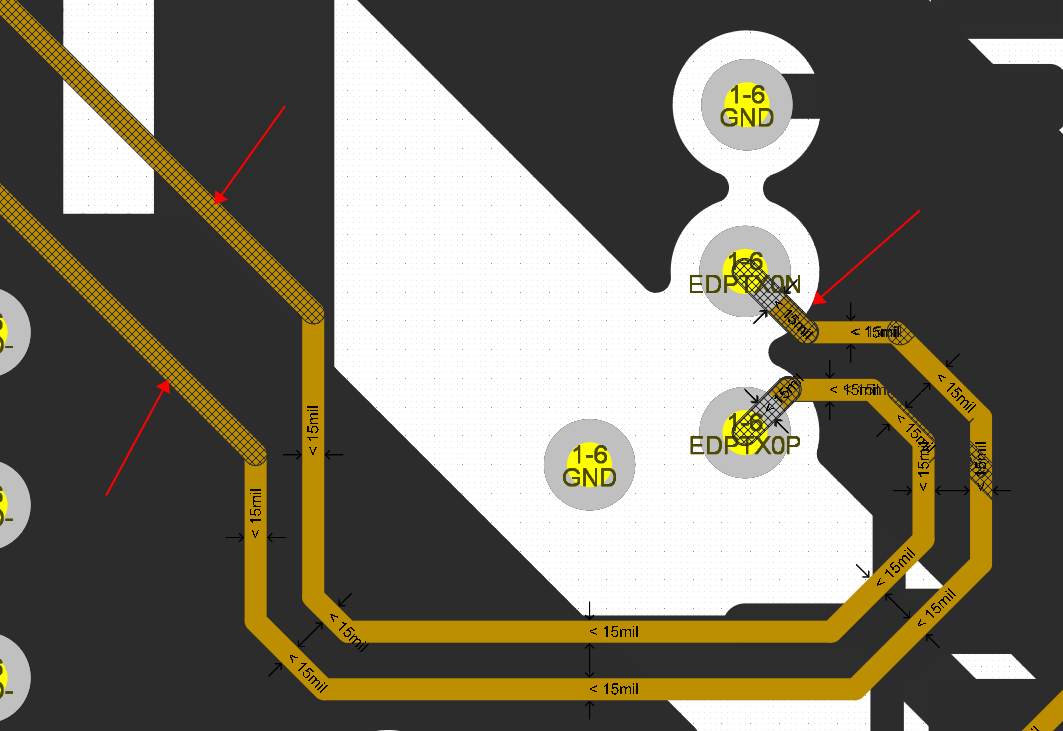

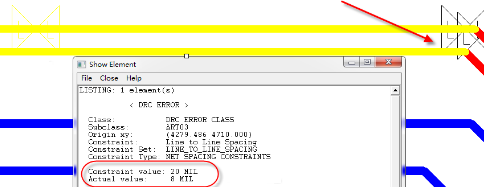

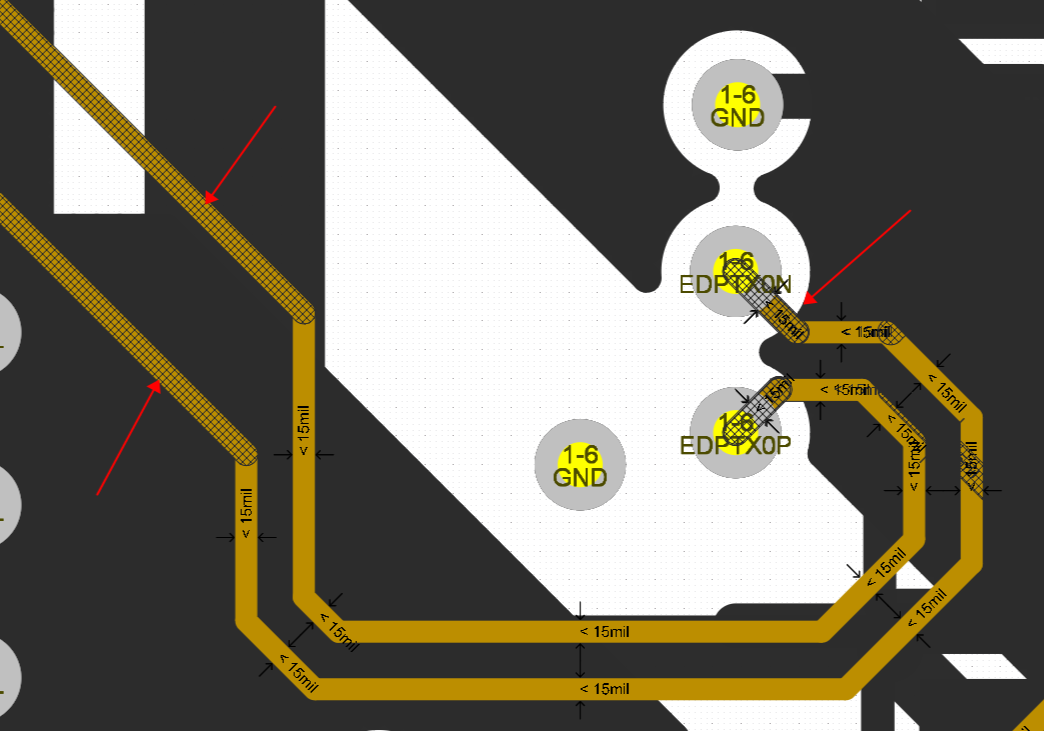

答:我们在PCB设计过程中,差分信号是比较重要的信号,一般设置差分信号到其它信号的间距是20mil,但是设置完差分信号到其它信号的间距之后,差分对内PN之间不满足20mil的间距,会报错,如图6-205所示:

答:我们在进行PCB设计的时候,对于差分信号换层,都是双击进行打孔,但是双击打孔的间距是系统默认的,有时候会导致过孔间距太近,影响信号的质量,如图6-283所示,我们是否可以手动去控制差分过孔之间的间距呢,当让是可以的,我们这里讲解一下具体的处理方法,如下所示:

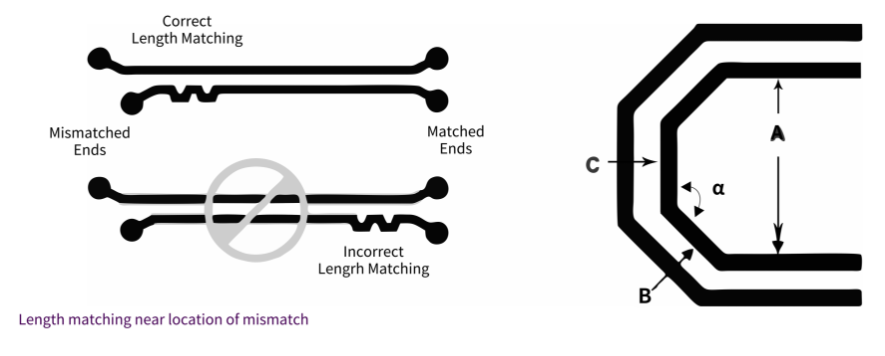

PCB设计,遇到差分线,需要做等长设计时,该怎么操作呢?在做走线等长设计的时候,我一般都是采用让走线进入蛇形走线模式,然后走出蛇形线来快速完成等长设计。

今天在设计PCB时,遇到了5对差分线。结果我花了整整一天的时间,都是在捣鼓这5对差分线。有人会问,花一天的时间去设计5对差分线,这工作效率太低了吧。人家layout工程师,三两下就可以搞定了。

Altium Designer 21全新功能差分线调节Altium Designer 21对差分线的优化不可谓不大,不同于之前版本修线时不小心修动了差分线之后,阻抗间距就立即发生了变化,重新调整间距极其麻烦,基本上只能删除重画,21版本完美

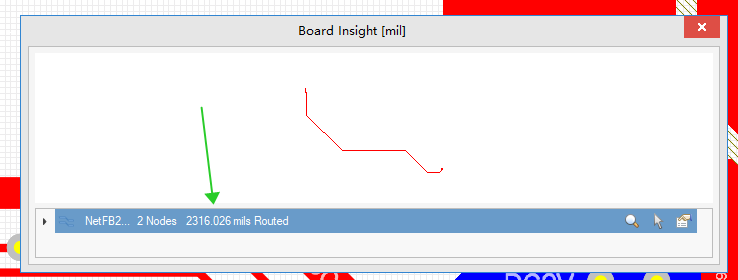

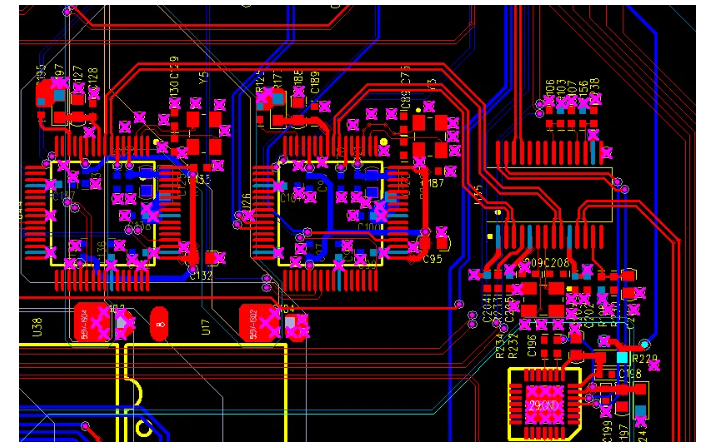

Altium Designer走差分线出现网格是什么原因?答:如图1所示,在AD软件中走差分线出现网格主要是差分线的未耦合长度没有满足差分规则所导致的,未耦合长度指的是差分线中不满足差分间距的长度。图 1 差分走线出现网格走线当出现这种错误

扫码关注

扫码关注