- 全部

- 默认排序

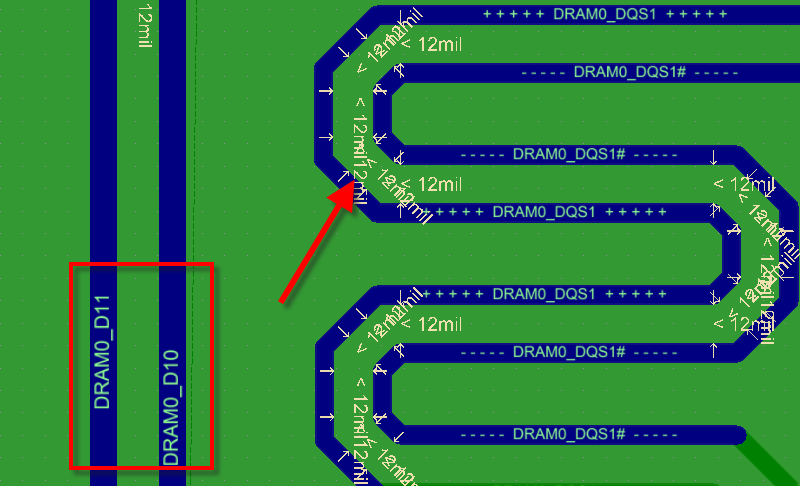

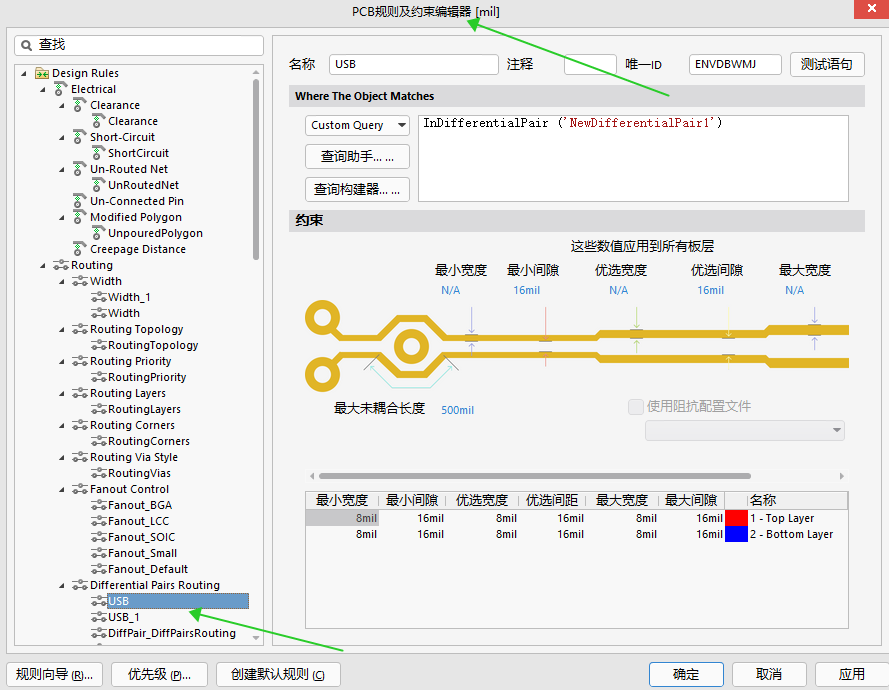

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨

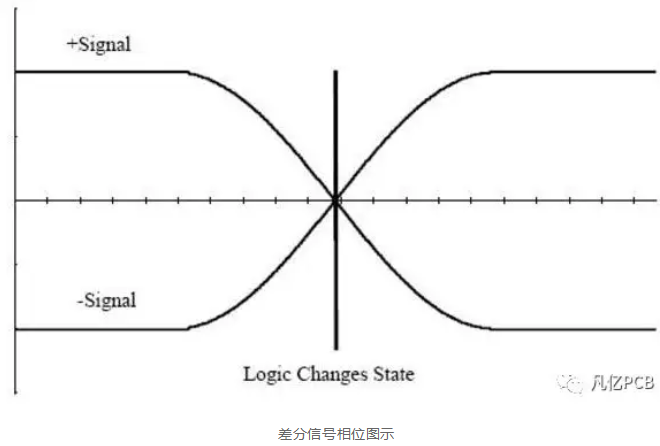

在高速PCB设计中,差分信号的应用越来越广泛,这主要是因为和普通的单端信号走线相比,差分信号具有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。作为一名(准)PCB设计工程师,我们当然需要充分理解差分信号!

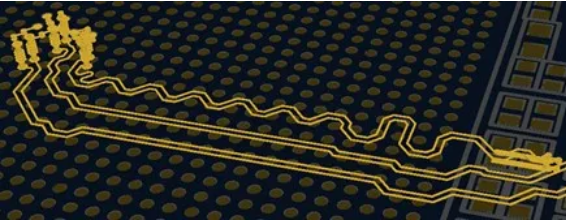

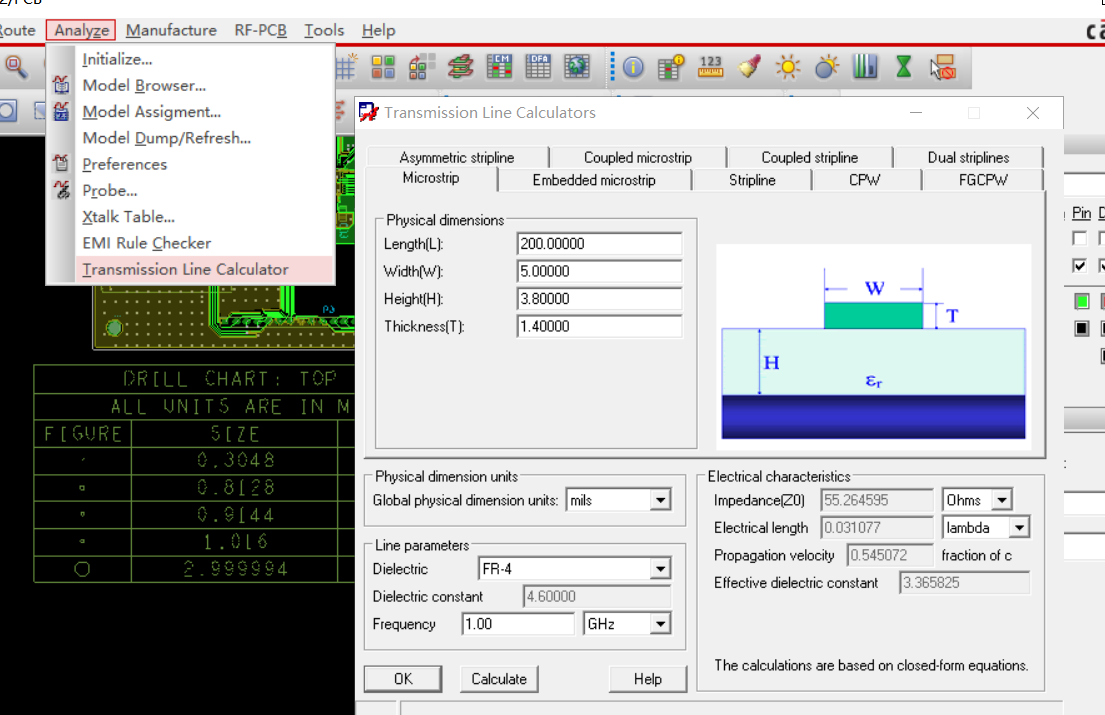

随着信号速率越来越高,PCB设计时,越来越多的数字电路 需要对走线阻抗控制、延迟等传输参数进行计算。Allegro16.6版本提供了一个内置的传输线参数计算工具,能对微带线、嵌入式微带线、带状线、差分线等多种传输数据结构进行传输参数计算。

扫码关注

扫码关注