- 全部

- 默认排序

Class就是类,同一属性的网络或元件或层或差分放置在一起构成一个类别,即常说的类。把相同属性的网络放置在一起,就是网络类,如GND网络和电源网络放置在一起构成电源网络类。把属于90欧姆的差分放置在一起,构成90欧姆差分类

前文对差分类的添加进行了详细的讲述,不再进行赘述,这里对差分规则设置进行讲述。差分规则设置分为两种方法,一种为向导法,另一种为手工法。

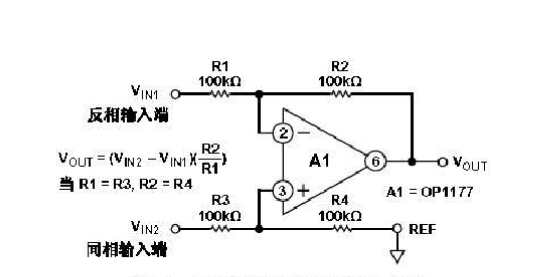

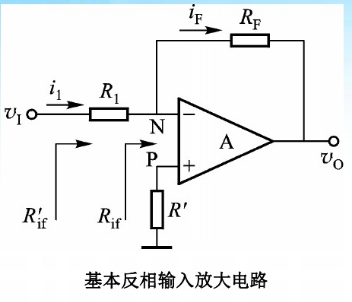

运算放大器的反相输入分析

放大器反相的输入端是指输入端和输出端的极性相反,一个简单的运放,一般包括一个信号输出端,两个高阻抗输入端,同相和反相输入端。所以,可以用运放制作同相或是反相、差分放大器。

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

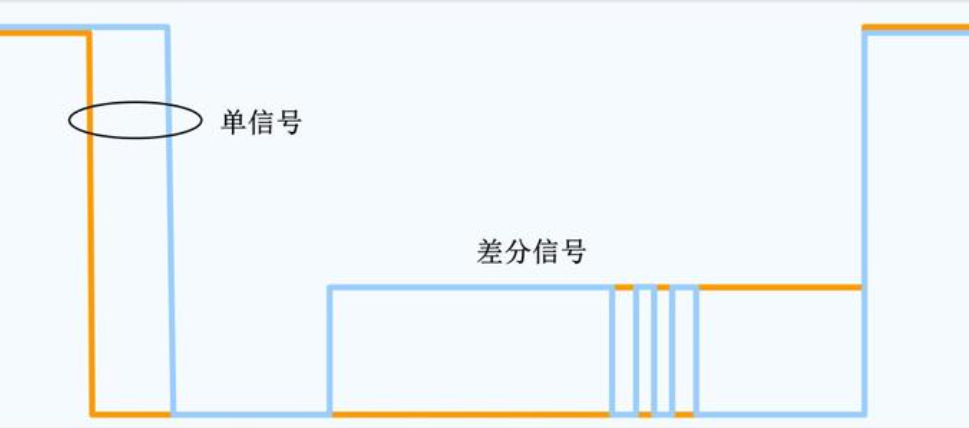

答:差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法,差分传输在这两根线上都传输信号,这两个信号的振幅相等,相位相反。在这两根线上传输的信号就是差分信号。差分信号是用一个数值来表示两个物理量之间的差异。差分信号又称差模信号,是相对共模信号而言的。我们用一个方法对差分信号做一下比喻,差分信号就好比是跷跷板上的两个人,当一个人被跷上去的时候,另一个人被跷下来了 - 但是他们的平均位置是不变的。继续跷跷板的类推,正值可以表示左边的人比右边的人高,而负值表示右边的人比左边的人高。0 表

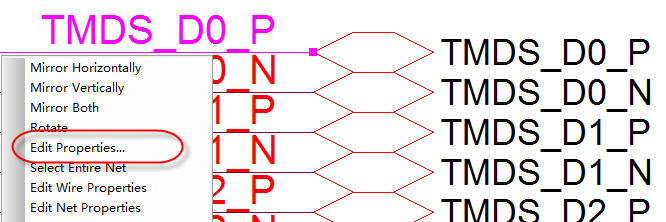

答:很多人很好奇,我们PCB文件可以添加差分信号属性,来进行走线,那原理图中可以对信号添加差分属性吗?这个当然也是可以的,下面就我们一步一步来给大家演示如何在原理图中进行差分属性的添加:第一步,首先需要在原理图中添加差分属性,选中差分信号的一根网络,然后点击鼠标右键,执行命令Edit Properties…,进行属性编辑,或者双击鼠标左键,也是一样的效果,如图3-99所示: 图3-99 信号差分属性编辑示意图第二步,进入信号属性编辑的界面,下边栏选中Schematic Ne

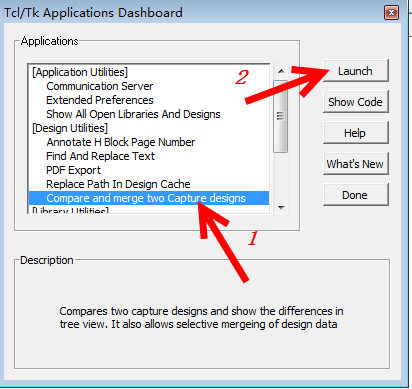

答:在电子设计中, 电路图的修改是非常频繁的,改动的多了,有时候会出现要改回去的情况,所以有时就会需要对两份原理图进行差分化的对比,操作步骤如下:第一步,首先,我们对一份原理图进行修改,修改一点点内容,做为测试之用,如图3-123与图3-124所示,方便后期查找; 图3-123 修改后的原理图示意 图3-124 修改前的原理图示意第二步,我们打开其中的任意一份原理图,选中原理图的根目录,然后执行菜单命令Accessories-Cadence TcL/Tk Utilities命

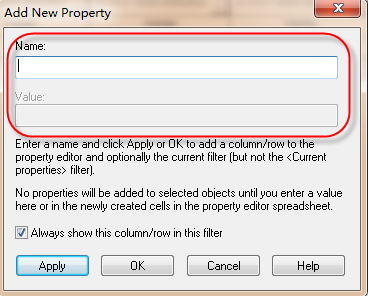

答:运用Orcad进行原理图的绘制时,除了它本身自带的这些属性以外呢,有时候会给它增加一些额外的属性,来方便别人查看你的原理图与检查原理图,例如器件的料号、ROOM属性、差分属性等,这里我们就以增加常用的ROOM属性为例,来讲解一下Orcad中怎么给元器件自定义属性。第一步,首先在原理图中,选中你需要添加属性的那一部分内容,如果是某一页的话, 直接选中这一页,点击编辑,编辑这一页的属性,如图3-187所示;如果是给某一部分模块的话,运用鼠标左键框选中这一部分模块,点击鼠标右键编辑属性即可,如图3

答:我们对于高速信号传输,比如差分信号、一组总线传输,都需要对其进行时序等长处理,在16.6版本以上,Allegro软件推出了自动等长的功能,在空间足够的情况下,是可以采用自动等长的功能,省去手动绕等长的时间,具体操作步骤如下所示:

扫码关注

扫码关注