- 全部

- 默认排序

类是某种特定类型设计的逻辑集合,是将多个元素进行的一个集合。在AD软件汇总结构类将这个概念进行了进一步的层次上升,结构类是一种特殊形式的类,可以归纳一下成员: 网络类 元件类 板层类 焊盘类 From To 类 差分对类设计通道类 多边形铺铜类 其他的结构类

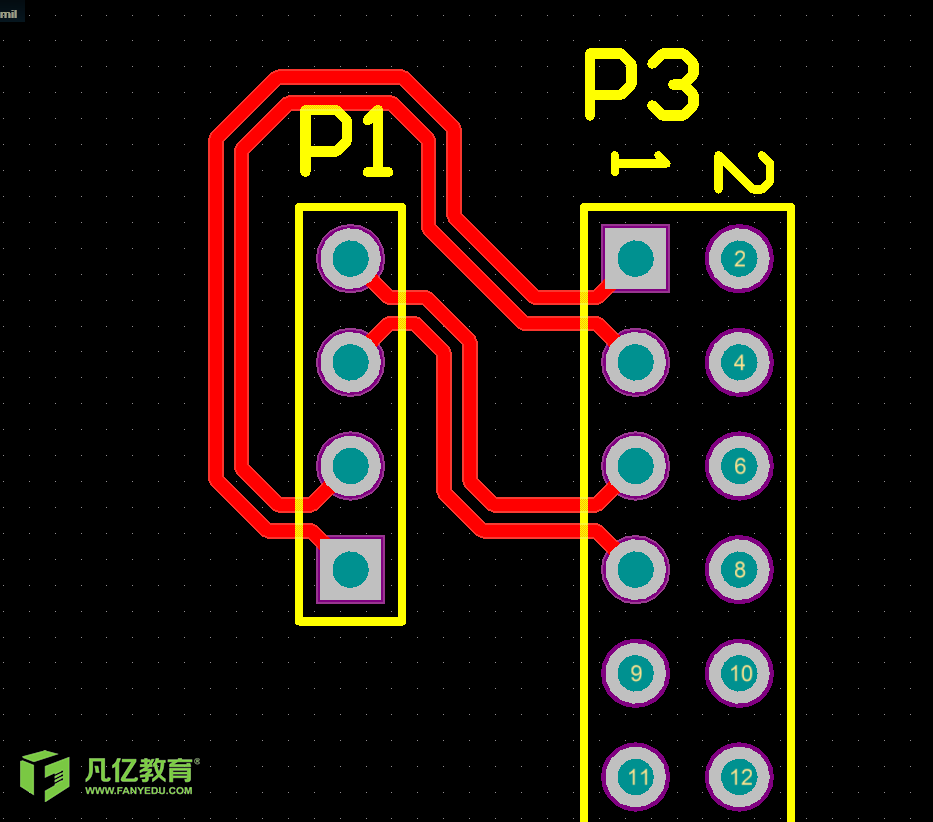

通常在做大型项目的时候我们都会遇到网络管脚号的互换,将PCB网络进行修改,然后就不知道如何直接进行PCB网络反倒,就只能在PCB里面修改好的网络了。然后在原理图里面进行一个个进行网络修改,特别是遇到几百对差分信号的时候,这样的工作量是十分巨大的。如图 我在PCB中修改A的差分和B的差分的位置,我在PCB里面进行换PIN工作

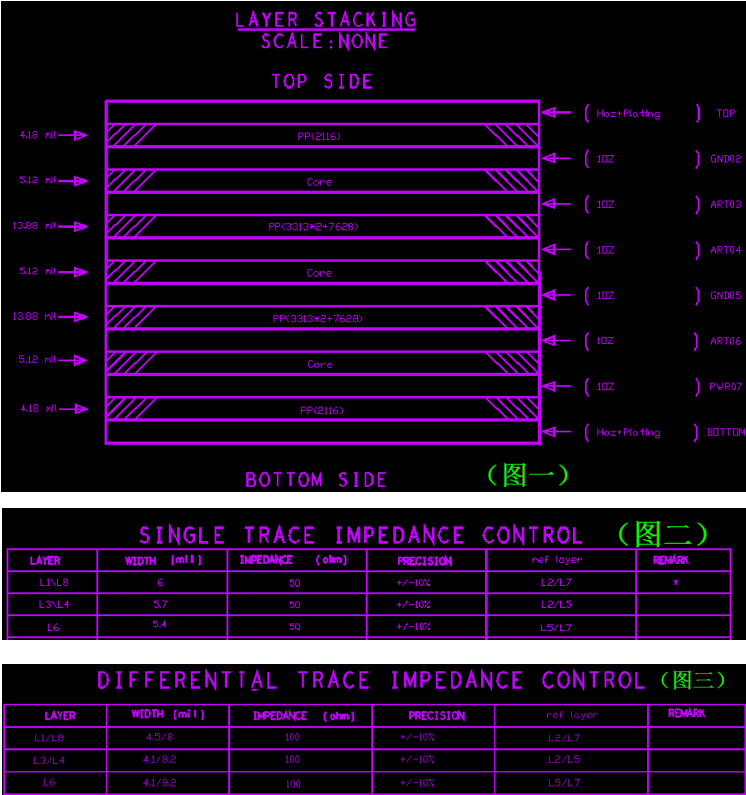

1、 需要要做阻抗的信号线,应该严格按照叠层计算出来的线宽、线距来设置。比如射频信号(常规50R控制)、重要单端50R、差分90R、差分100R等信号线,通过叠层可计算出具体的线宽线距(下图示)。2、 PCB设计的线宽线距应该考虑所选PCB生产工厂的生产工艺能力,如若设计时设置线宽线距超过合作的PCB生产厂商的制程能力,轻则需要添加不必要的生产成本,重则导致设计无法生产。一般正常情况下线宽线距控制到6/6mil,过孔选择12mil(0.3mm),基本80%以上PCB生产厂商都能生产,生

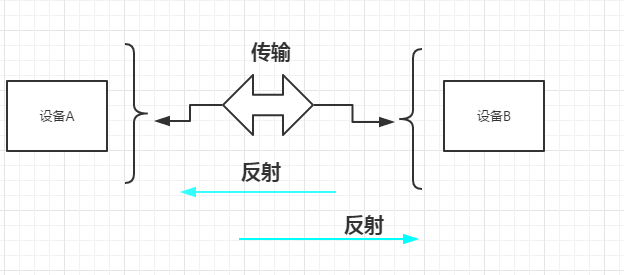

差分走线,信号换层过孔数量,等长长度把控,阻抗控制要求,跨分割的损耗,走线拐角的位置形状,绕线方式对应的插损和回损,布局不妥当造成的一系列串扰和叠层串扰,布局不恰当操作焊盘存在的stub。

电路设计之电流测量

电路设计结合这些因素,针对电流监控的常用信号链配置会涉及到一个用于放大分流电阻器两端电压的模拟前端、一个将放大的电压转换为数字表示的 ADC,以及一个系统控制器。 AFE 通常使用运算放大器或专用电流检测放大器实现,将分流电阻器两端产生的小差分电压转换为更大的输出电压,以便使用完整的 ADC 测量范围。ADC 可以是独立器件,也可以是微控制器或片上系统 (SoC) 内的片载模块,可对电压信号进行数字化处理,并将结果信息提供给控制处理器。系统控制器使用电流的数字化测量结果来优化系统性能或实现安全

模拟电路电路设计的九个阶段,类似下围棋的段位。从一段到九段都看完后,就掌握自身是哪一个时期的水平了。不容错过哦。 一开始步入这一行,对PMOS/NMOS/BJT那些的只不过是有一个大概的掌握,各类元器件的性能都不太清晰,实际电路设计成哪样的电路也没有想法,路原理图主要是看国内杂志期刊上的文章,或是依照教材上现成的电路,总感觉他们说得都是有道理。做的电路主要是是小规模的模块,做些差分运放,或是带隙基准的仿真那些的就计算着发文章,生怕到时候论文凑不够。总的来说,基本上看见运放还是发怵。感觉spic

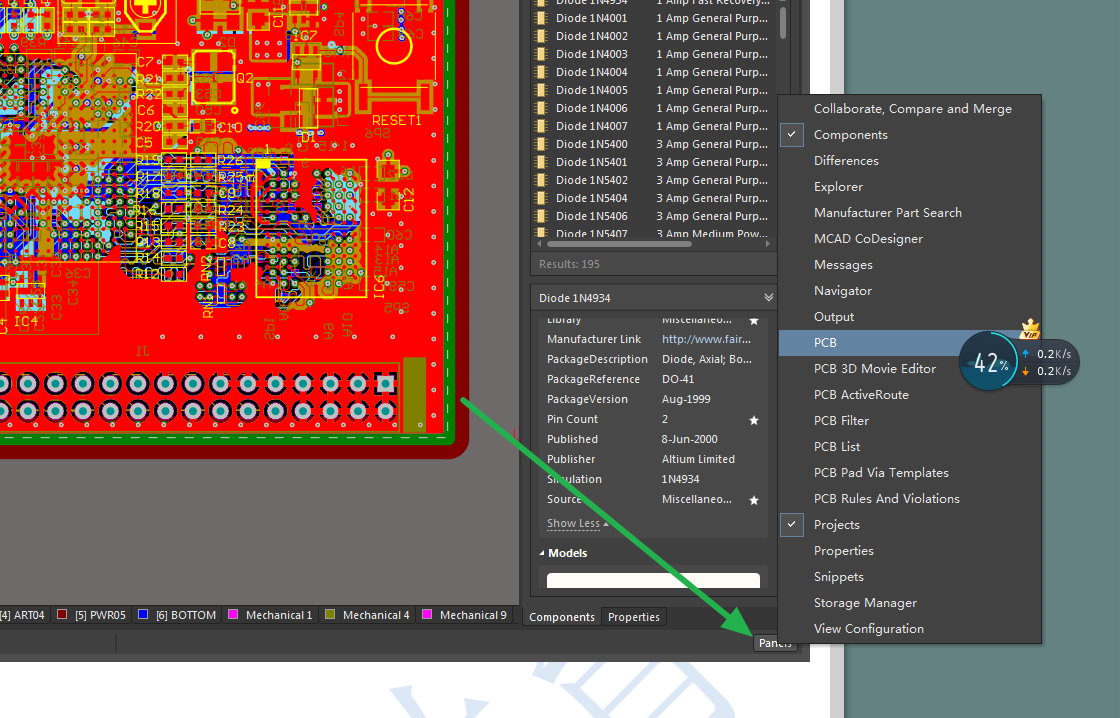

前期为了满足各项设计的要求,我们会设置很多约束规则,当一个PCB单板设计完成之后,通常要进行DRC(Design Rule Check)检查。DRC检查就是检查设计是否满足所设置的规则。一个完整的PCB设计必须经过各项电气规则检查。常见的检查项包括间距、开路以及短路的检查,更加严格的还有差分对、阻抗线等检查。

PCB设计:检查线间距时差分间距报错的处理方法 为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如图12-23所示。

扫码关注

扫码关注