- 全部

- 默认排序

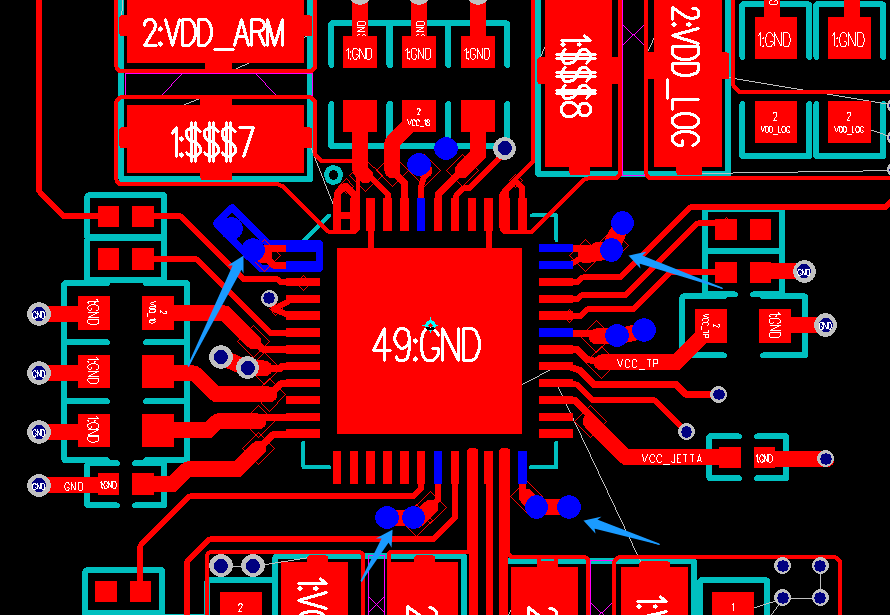

DCDC 4路输入不满足载流,一般20mil过1A2.输出铺铜尽量大一点,地网络尅直接连接在散热焊盘上3.走线需要优化一下4.元件尽量优先顶层布局5.反馈器件尽量靠近管脚放置,走一根10mil的线即可6.反馈需要加粗到10mil7.此处电源

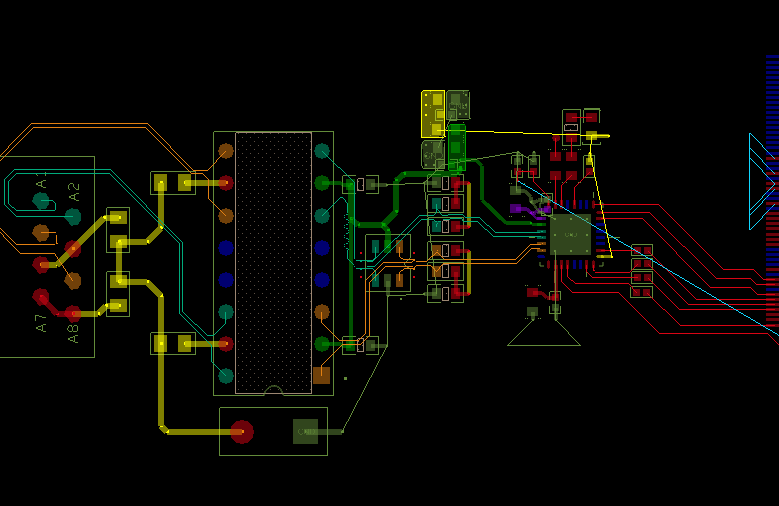

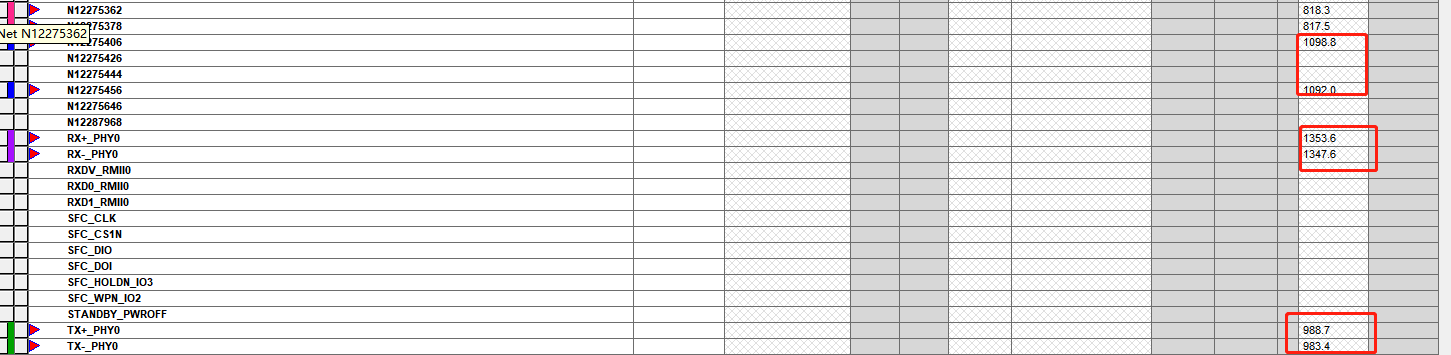

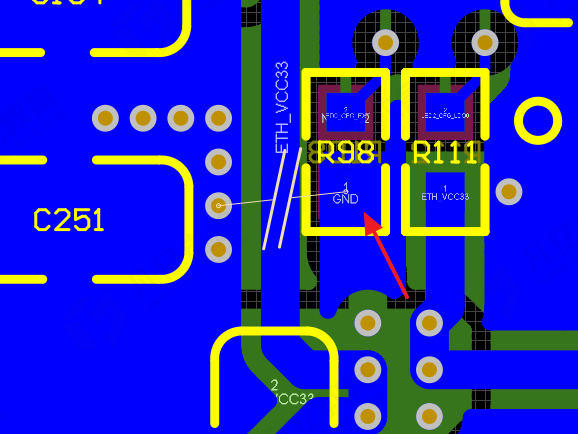

地网络在GND层欧通进行连接2.TX和RX要分别进行等长,误差100mil3.差分走线不满足差分间距要求4.锯齿状等长不能超过线距的两倍5.差分出线要尽量耦合6.差分对内等长误差5mil7.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避

随着高频高速电路使用率上升,地阻抗的控制变得愈发重要,这也要求工程师掌握地阻抗的解决方法,所以下面将谈谈如何在高频PCB设计中更好解决地阻抗问题。一般来说,地阻抗是指地面层(GND)的电流通过板底传输时遇到的电阻,地阻抗的控制对于保证信号完

差分对内不等长误差控制在5mil,差分也没有建差分对电源走线未完成,也没有整版铺铜焊盘出线不规范差分在这里没有换层为什么要打过孔这里差分应该这么走这里差分等长不要超过2倍间距,间距也要大于等于3w这里rx,tx的等长需要建等长组,rx的信号

一、硬件明明比软件更难,国内的硬件技术也不如软件,为什么硬件工程师待遇还不如软件?1、不需要太高层次的硬件设计,比如大部分小家电企业,简单的电子产品企业,单片机+简单外围设计就够了,单片机+屏幕+继电器控制+电源就是一个完整的产品板,工作2

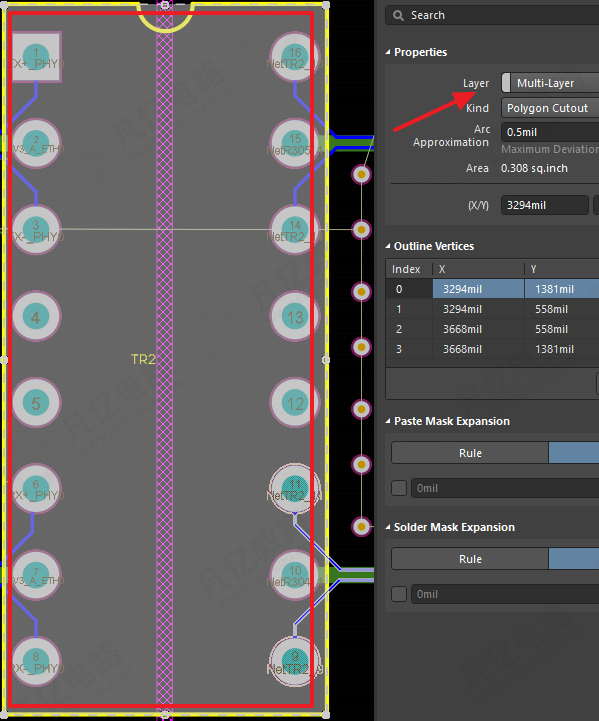

1,焊盘有开路。2.pcb存在drc4.多处孤岛铜皮和尖岬铜皮4.走线保持3w间距4.走线避免锐角5.差分换层旁边要打地过孔6.晶振布线错误,晶振的一对线要走成类差分的形式,并整体包地处理, 线尽量短如下图8.同层连接不需要打孔9.时钟线要

4月26日,第二届成都工博会顺利开展。本次展会沿用“工业引领,赋能产业新发展”主题,进一步高质量搭建制造业领域面向世界的交流合作平台,着力展现全国乃至全球制造领域新技术新产品应用场景,着力体现产业链供应链互嵌特征,知名企业齐聚一堂,一系列世

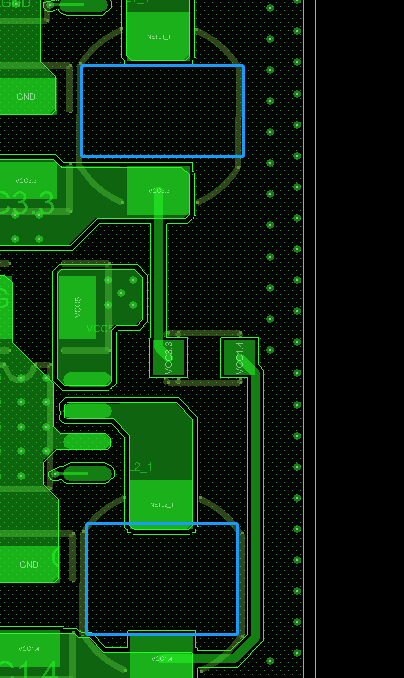

电感所在层测内部需要挖空处理2.地分割间距最少控制1mm以上,有跨接器件的地方不满足可以忽略,其他地方尽量一致3.除差分线外,其他的都需要加粗到20mil4.注意过孔尽量不要上焊盘5.注意等长线之间需要满足3W6.地址线也需要添加等长组进行

当今竞争激烈的电子市场中,由于电池与成本的限制,大部分的PCB工程师会选择单双面板来替代多层板,本文将从地平面来讨论PCB设计需要注意哪些问题。对于地平面和电流回路,需要注意如下基本事项:1、如果使用走线,应将其尽量加粗;2、PCB上的接地

1.变压器下方需要在所有层单独放置铺铜挖空,例如顶层放一个底层再放一个铺铜挖空。2.电源电容的输入输出都需要加粗载流。3.顶底层需要整版铺地铜处理4.TX等长组需要建立xSignals,前后段合并一起等长5.差分对内等长误差要控制在5mil

扫码关注

扫码关注