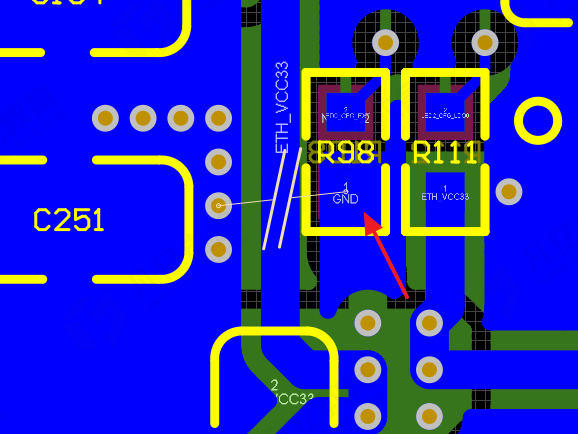

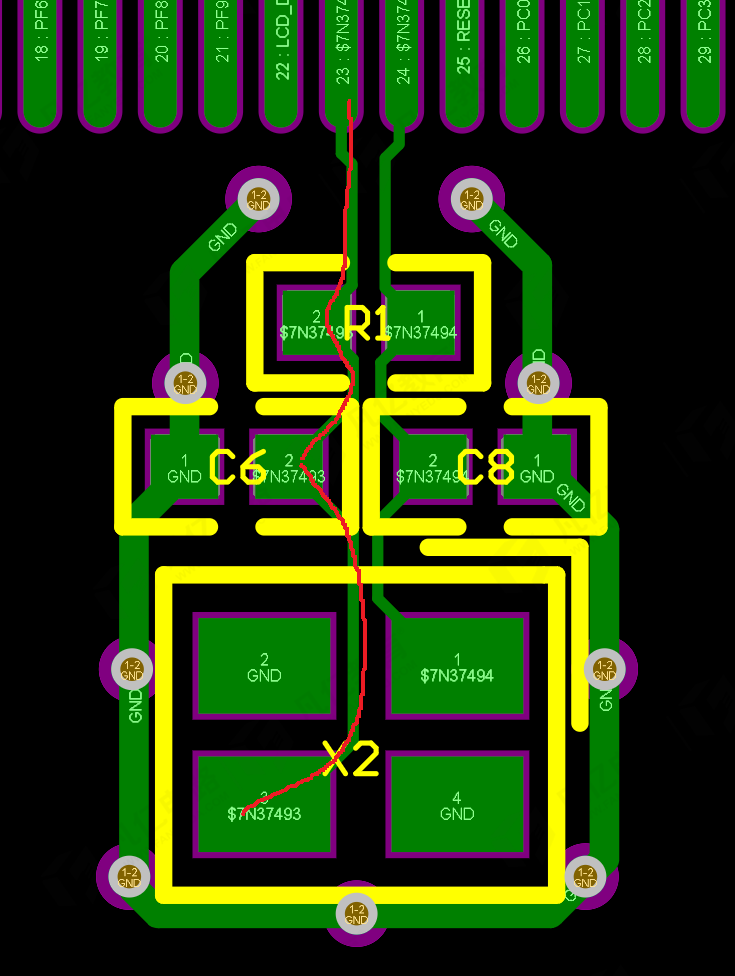

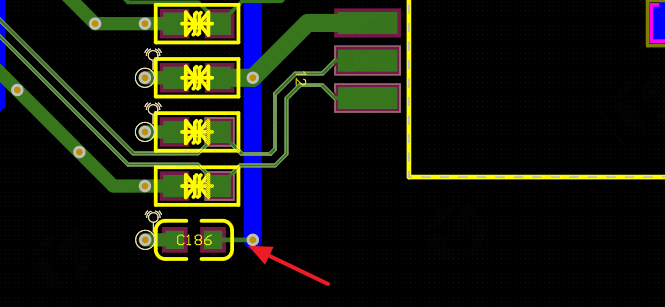

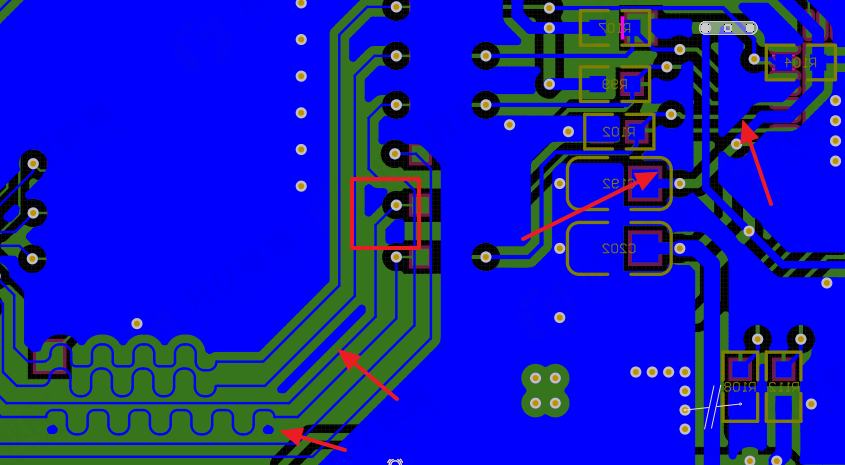

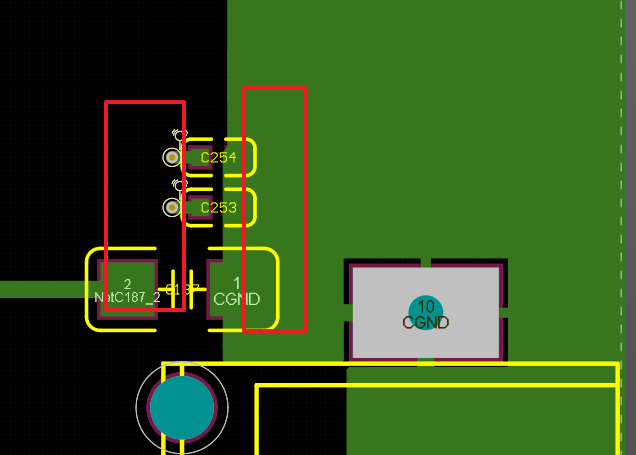

1,焊盘有开路。

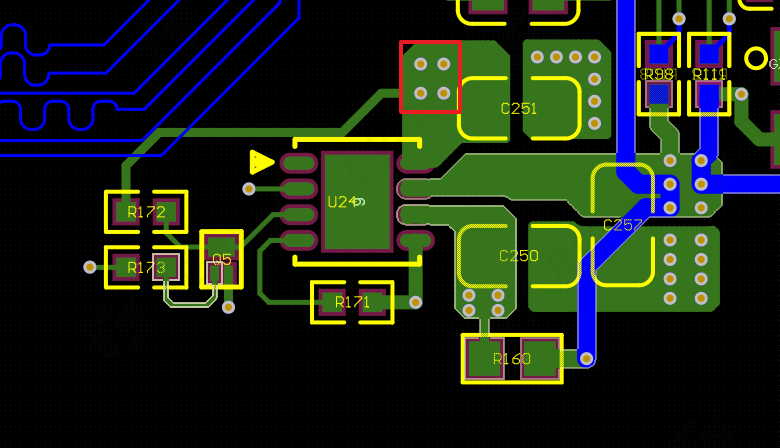

2.pcb存在drc

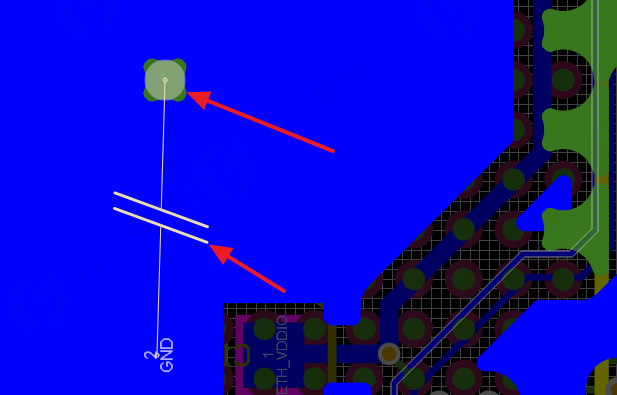

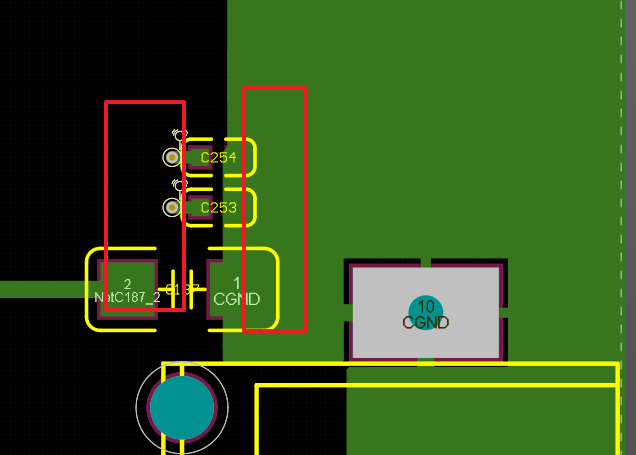

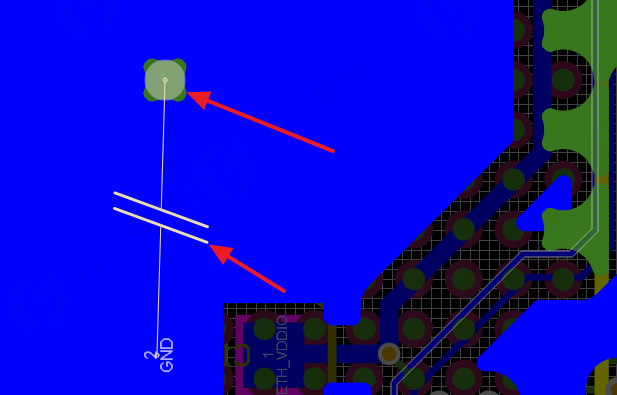

4.多处孤岛铜皮和尖岬铜皮

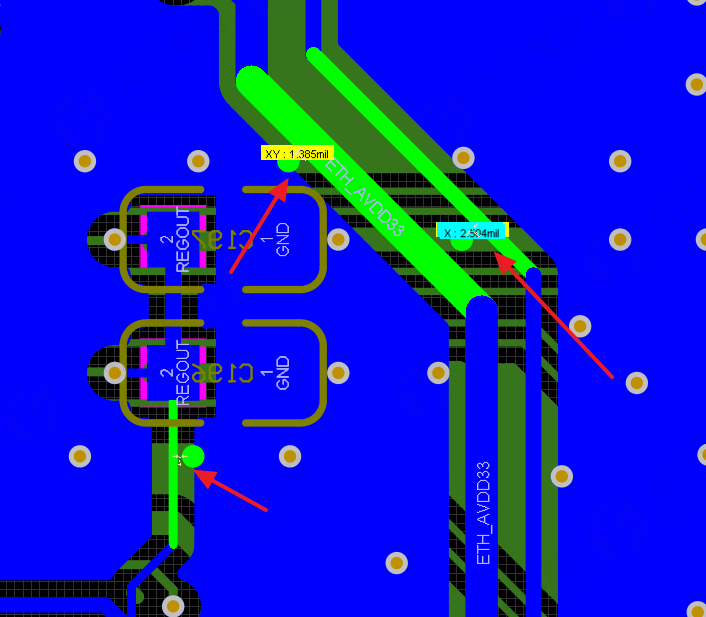

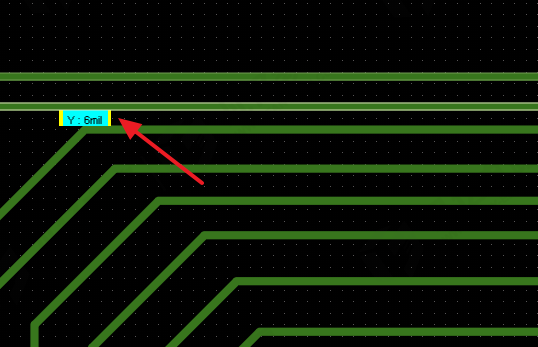

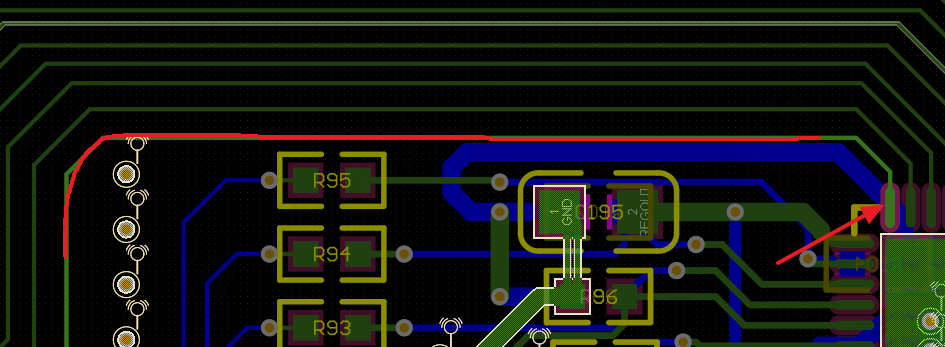

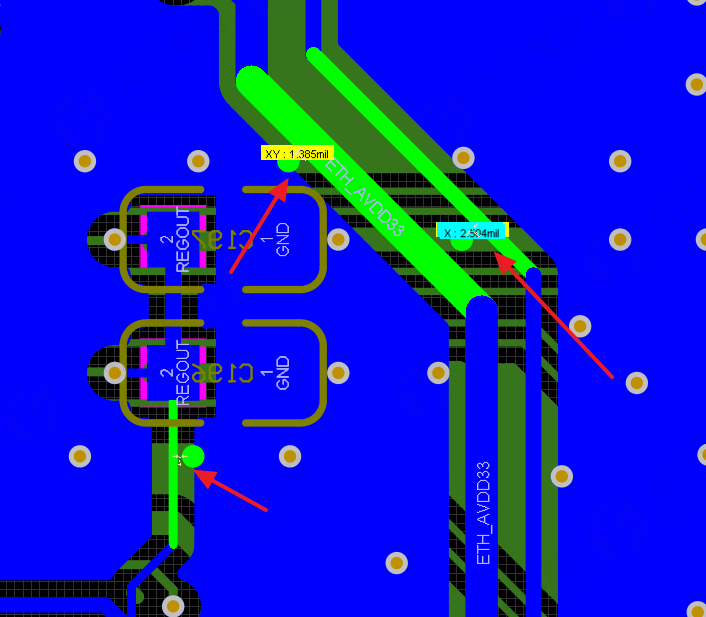

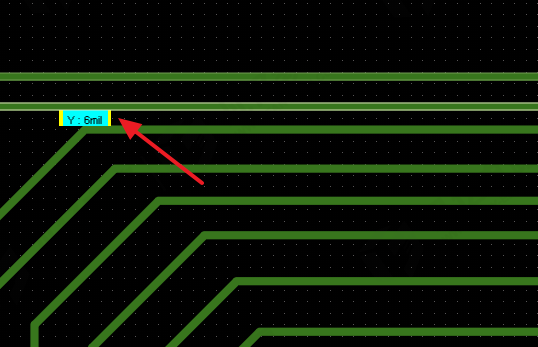

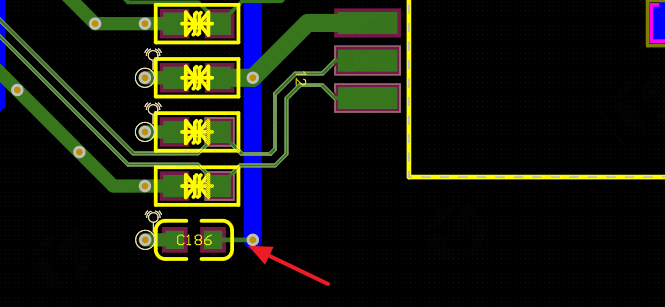

4.走线保持3w间距

4.走线避免锐角

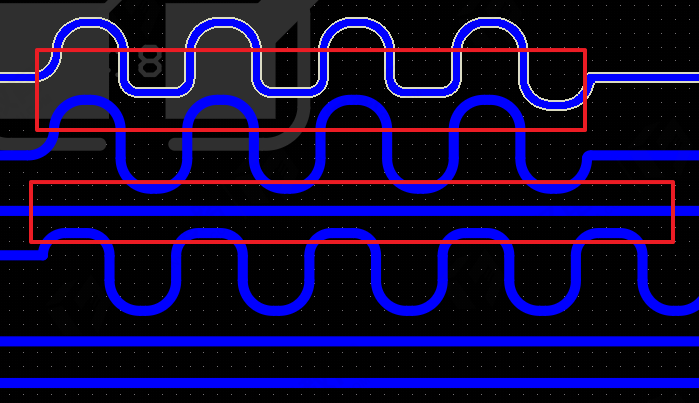

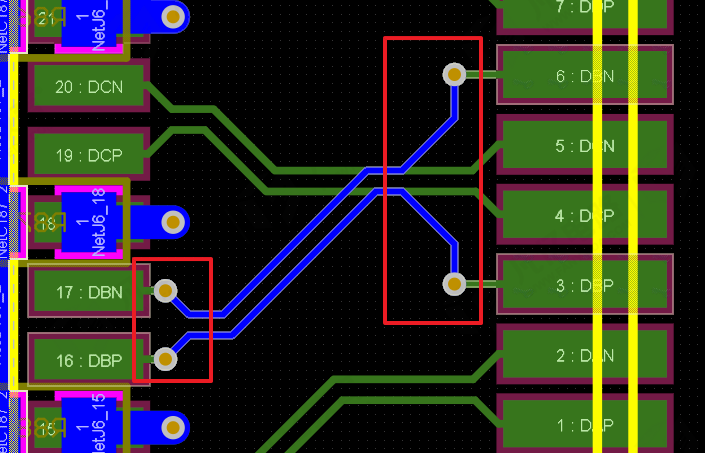

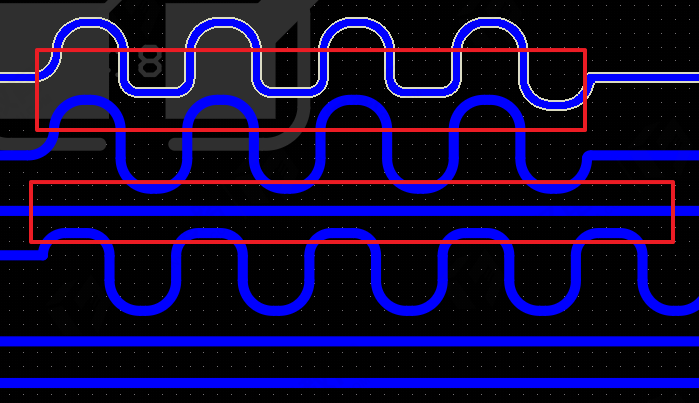

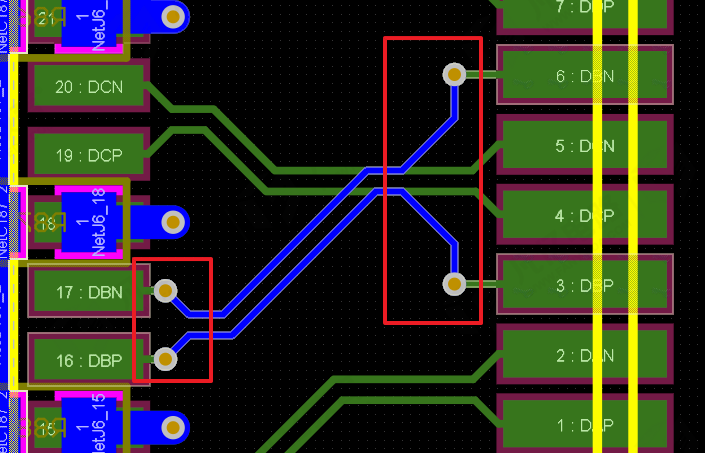

5.差分换层旁边要打地过孔

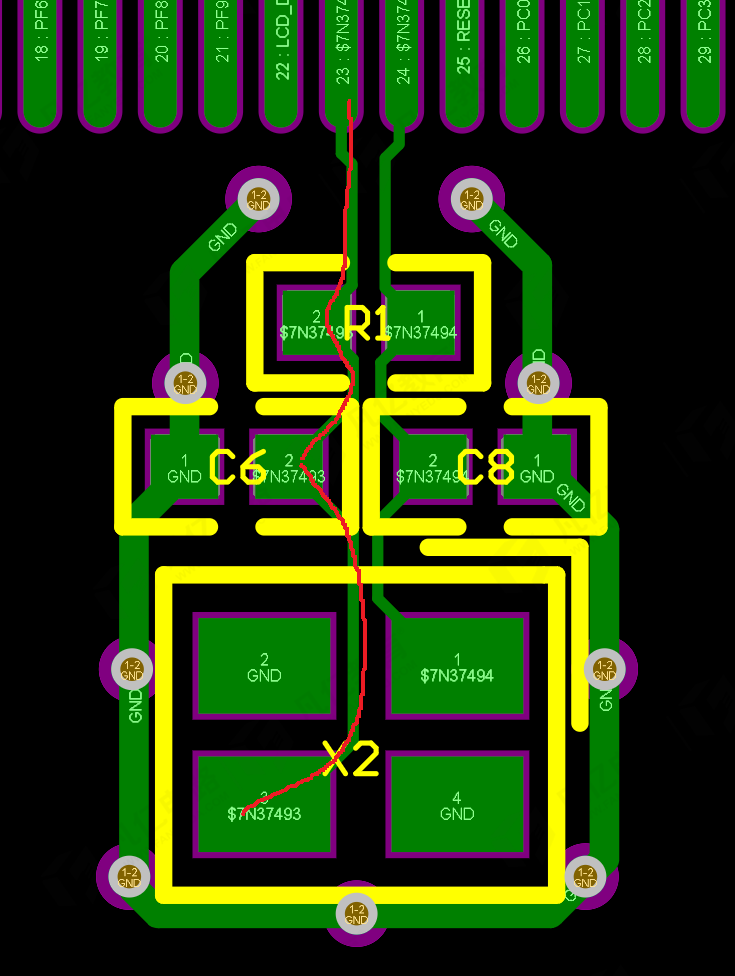

6.晶振布线错误,晶振的一对线要走成类差分的形式,并整体包地处理, 线尽量短如下图

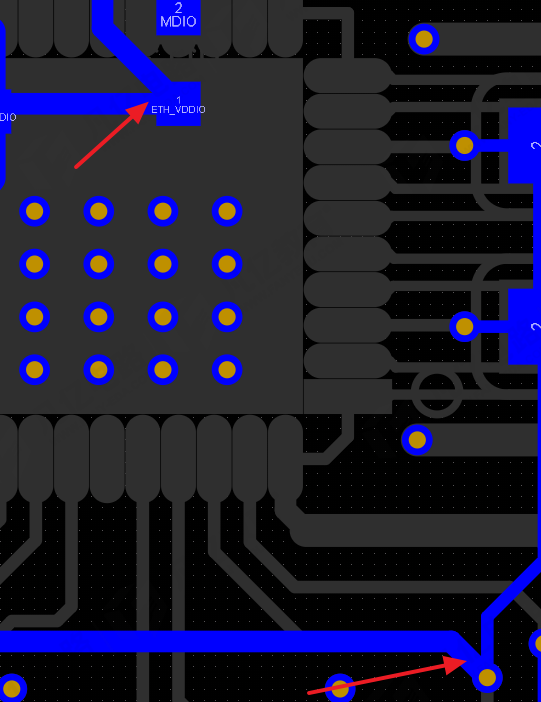

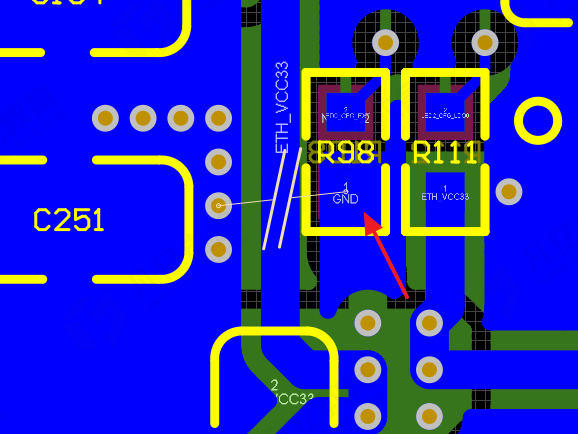

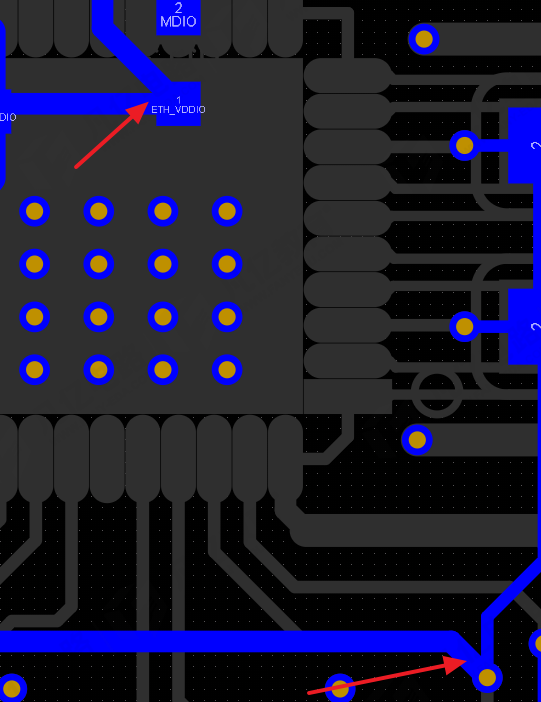

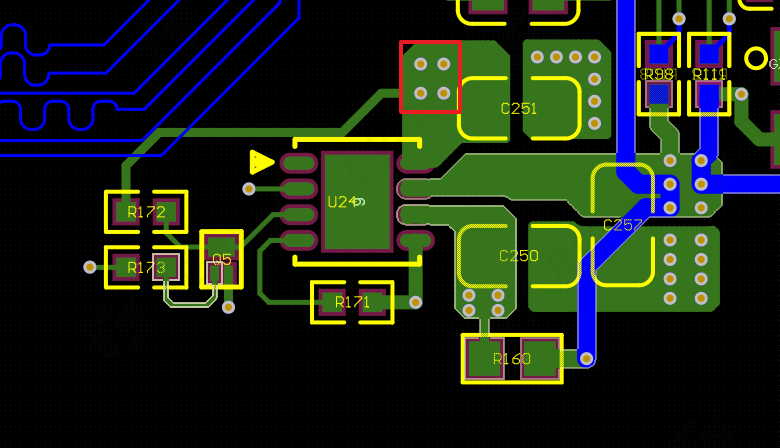

8.同层连接不需要打孔

9.时钟线要包地处理

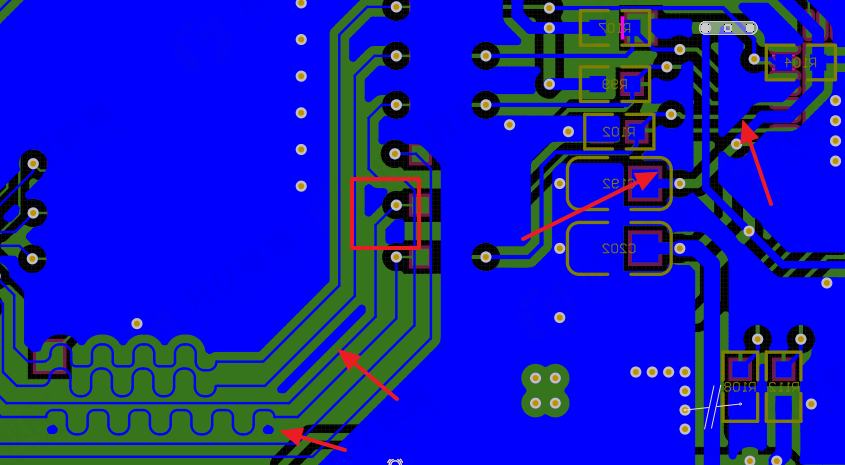

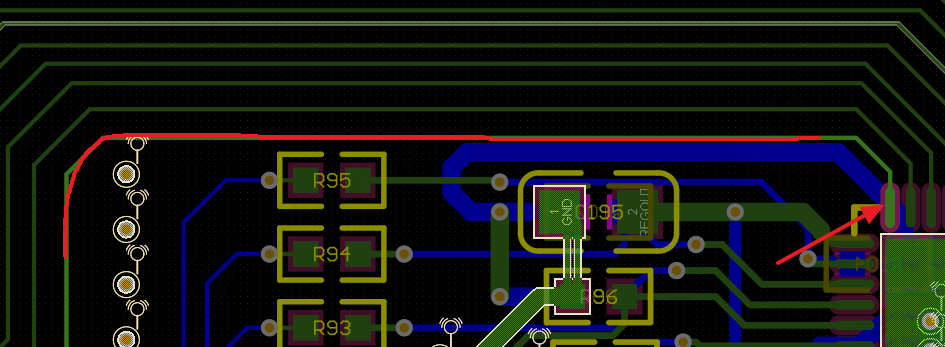

10.跨接器件两边要多打地过孔

11,变压器线出差分以外所有信号加粗到20mil,部分电容可以放底层靠近管脚放置。

以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

如需了解PCB特训班课程可以访问链接或扫码联系助教:

1,焊盘有开路。

2.pcb存在drc

4.多处孤岛铜皮和尖岬铜皮

4.走线保持3w间距

4.走线避免锐角

5.差分换层旁边要打地过孔

6.晶振布线错误,晶振的一对线要走成类差分的形式,并整体包地处理, 线尽量短如下图

8.同层连接不需要打孔

9.时钟线要包地处理

10.跨接器件两边要多打地过孔

11,变压器线出差分以外所有信号加粗到20mil,部分电容可以放底层靠近管脚放置。

以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

如需了解PCB特训班课程可以访问链接或扫码联系助教: