- 全部

- 默认排序

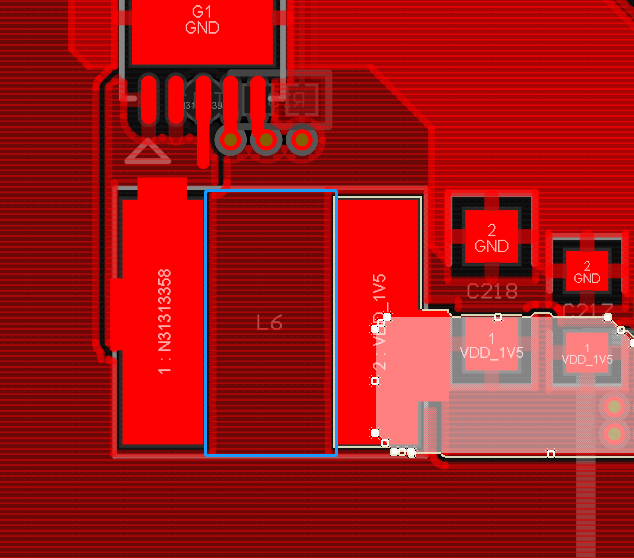

电感所在层的内部需要挖空处理2.注意过孔不要上焊盘3.器件摆放尽量对齐处理其他没什么问题以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.co

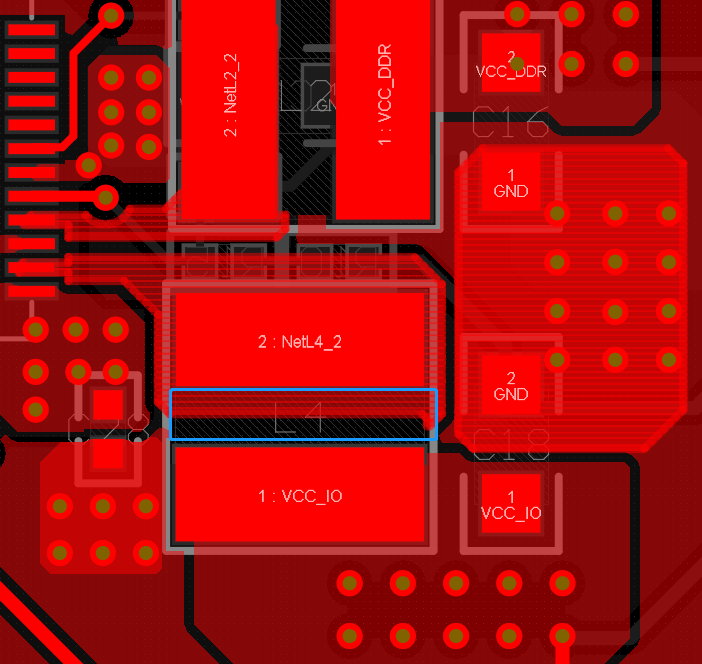

电感所在层的内部需要挖空处理2.铺铜进行包裹住焊盘,这样容易造成开路3.pcb上存在很多无网络过孔4.pcb上存在很多开路5.pcb上存在短路6.反馈从滤波电容后面取样以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特

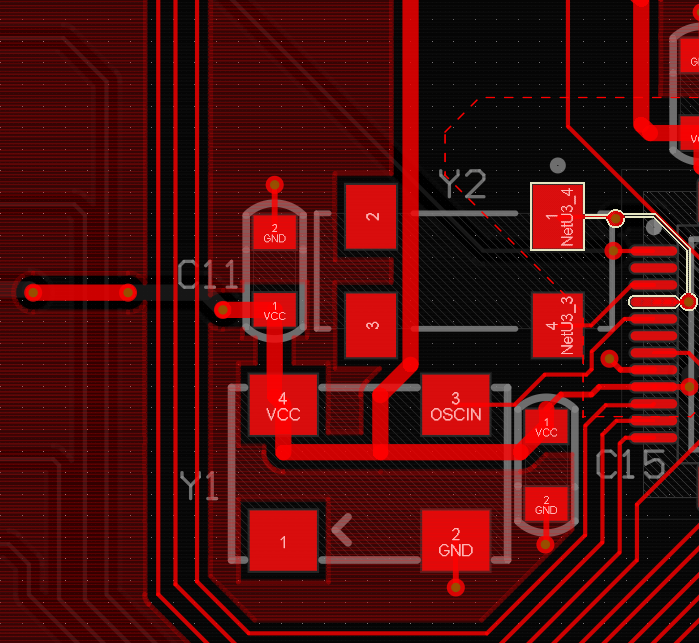

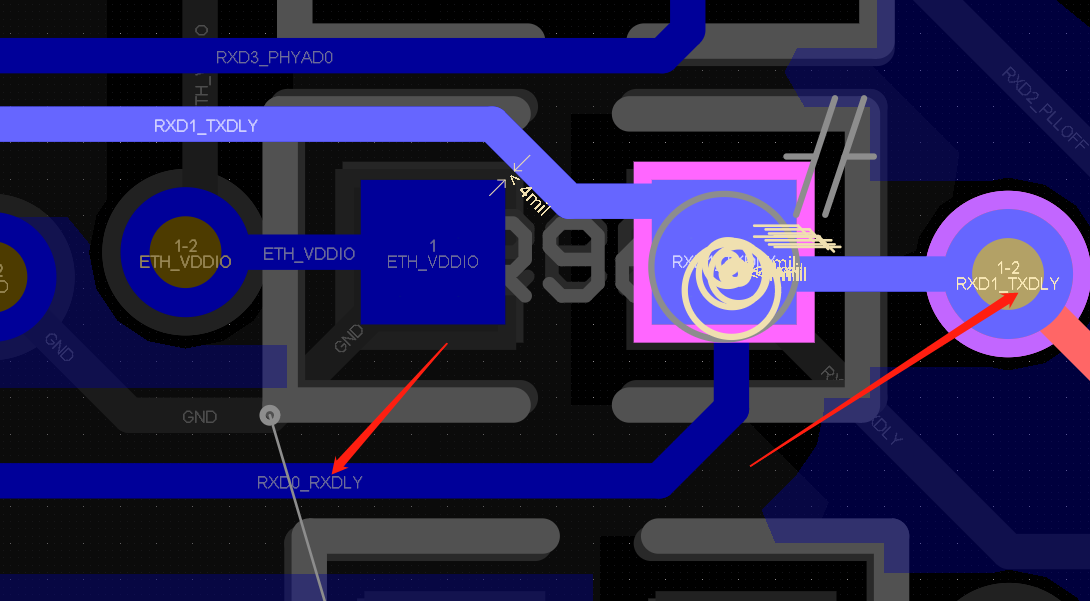

晶振需要包地处理2.此处一层连通无需打孔3.差分换层尽量在旁边打上一对地过孔,空间足够尽量包地处理4.差分出线尽量耦合5.长焊盘出线不规范,尽量从中间拉出来在耦合6.注意过孔不要上焊盘7.SD卡未添加class进行等长,误差300mil8.

电源网络就近打孔即可2.晶振包地多打地过孔,晶振下面尽量不要走线3.VGA属于模拟信号,走线需要加粗,并包地处理,下面不要穿其他信号线4.没有添加网口4对差分的class5.差分对内等长误差5mil6.变压器需要所有层挖空7.确认一下此处是

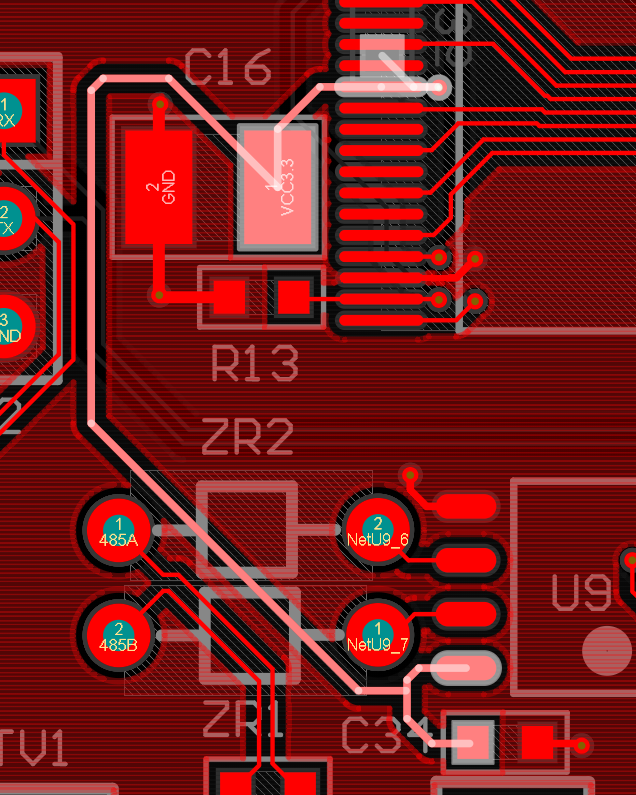

变压器下面所有层都要挖空处理xsignal等长超出误差范围差分没有做对内等长dm5这根线没有进行等长485的这个类差分可以优化一下。电感所在层要挖空处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问

串音干扰是高速PCB设计的首要解决问题之一,为减少PCB板上的串音问题,很多工程师都会提前分析设计电路,但部分工程师可能不太清楚,PCB板的分层也是串音控制重要因素之一,接下来我们来看看!在PCB设计时不重视分层,在高速PCB设计是属于重大

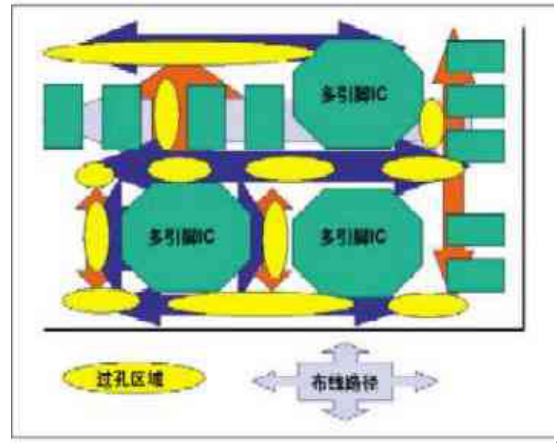

不可否认的是,尽管现在的EDA工具很强大,但随着PCB尺寸要求越来越高,器件密度大幅上涨,直接决定了PCB设计难度不低,很多工程师不可避免面对同样的问题:如何高效实现PCB的布线效率及缩短设计时间呢?1、确定PCB的层数电路板尺寸和布线层数

pcb上存在短路2.滤波电容靠近管脚放置,走线加粗3.晶振下面尽量不要走线4.此处电源不满足载流5.变压器所有层挖空6.变压器除差分信号外,其他信号都需要加粗到20mil7.差分线对内等长处理不当,锯齿状等长凸起高度不能超过线距的两倍8.走

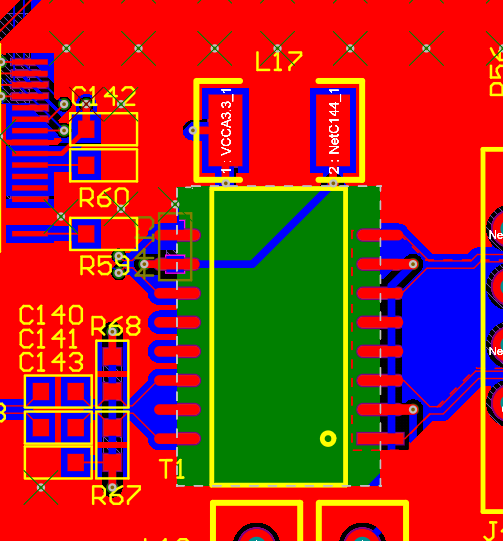

电感所在层的呢恩不需要挖空2.差分线对内等长处理不当,锯齿状等长,凸起高度不得超过线距的两倍3.注意数据线等长需要满足3W规则4.差分出线要尽量耦合5.存在多余的线头6.注意过孔不要上焊盘7.注意器件摆放过近,建议最少1.5mm8.过孔需要

3月28日下午,华为召开发布会,正式发布了2021年年度报告。华为首席财务官孟晚舟在去年获释后,首度参加华为业绩发布会,并对华为2021年财务数据进行了解析。华为轮值董事长郭平则从业务及技术发展层面进行了介绍。一、净利润1137亿元人民币,同比增长75.9%报告显示,华为实现全球销售收入6368亿元

扫码关注

扫码关注