- 全部

- 默认排序

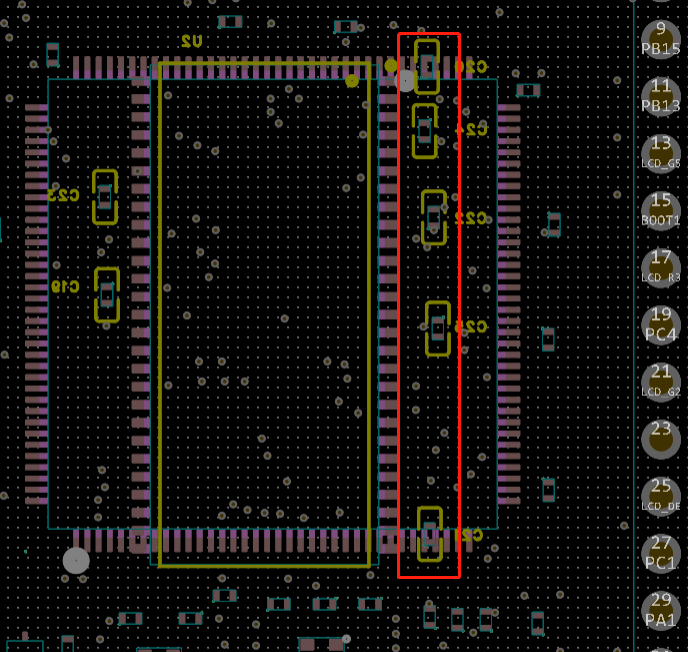

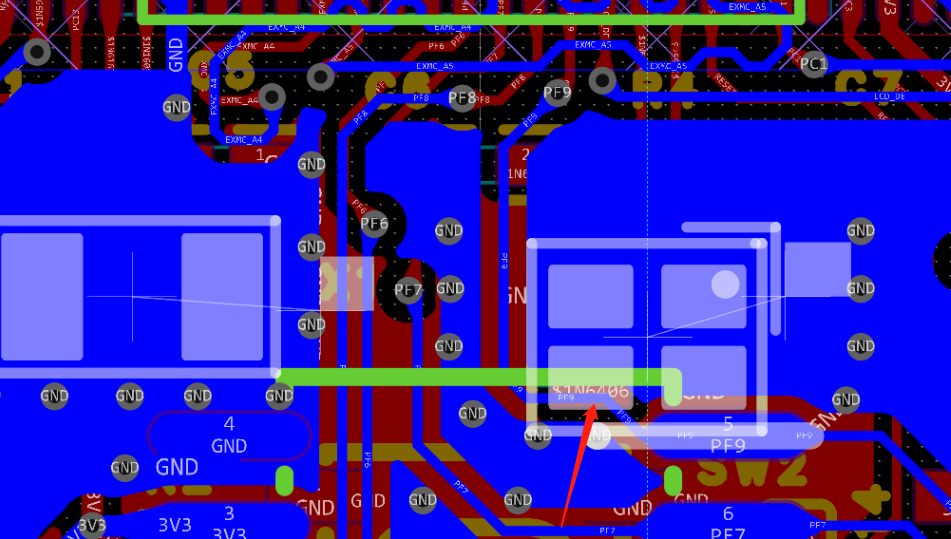

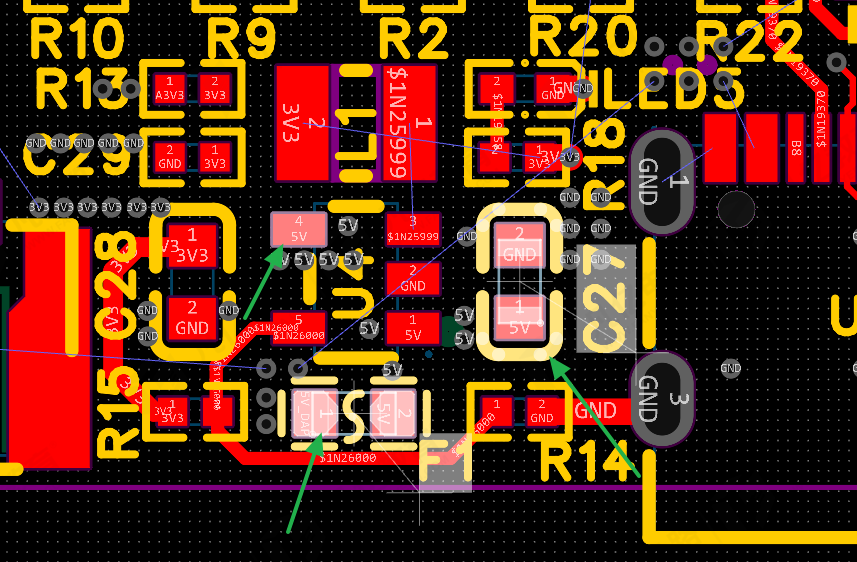

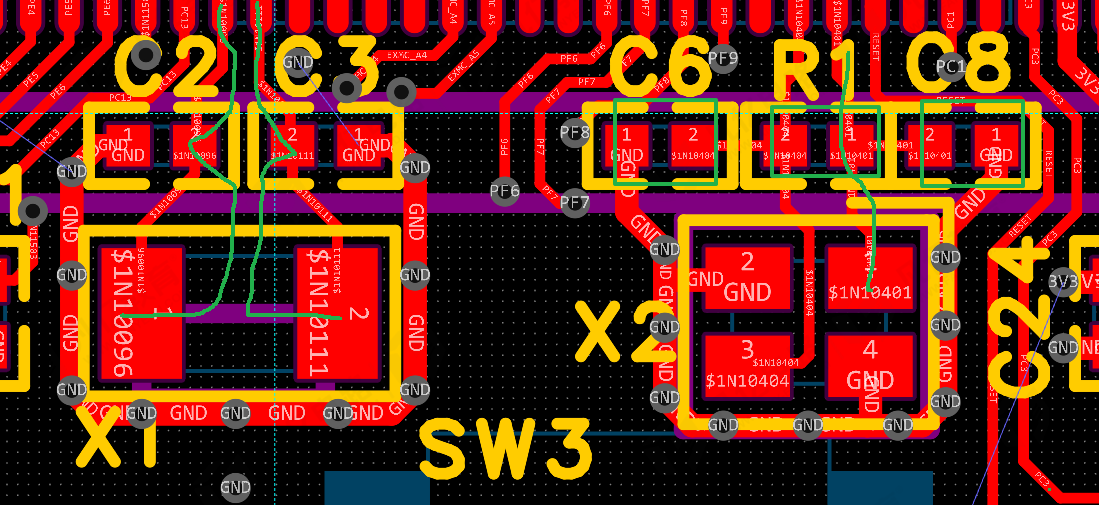

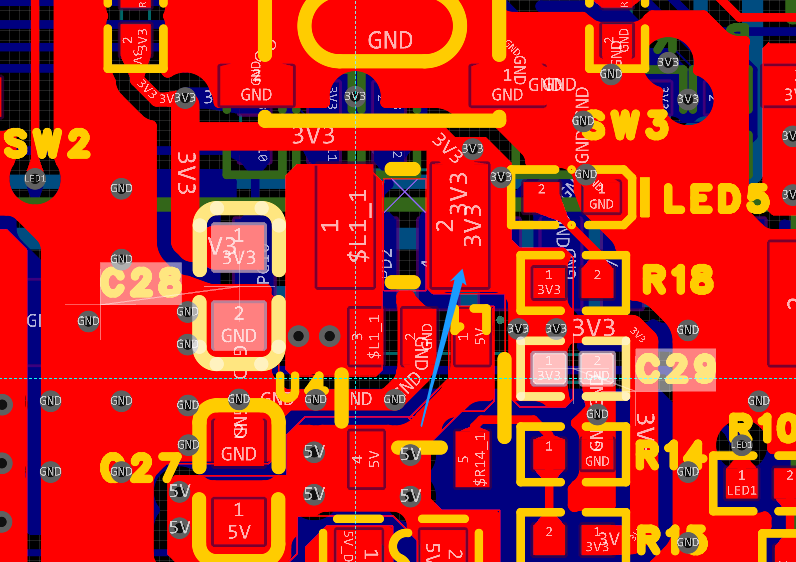

器件摆放注意局部对齐处理2.注意器件干涉3.电源输出的滤波电容要靠近输出管脚放置4.电源输入输出换层打孔处理不当,输入应该打在滤波电容的前面,输出打在滤波电容的后面5..差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍6.确认一下此处

差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍2.器件摆放尽量对齐处理3.晶振走线需要走类差分处理4.电源输入的滤波电容应该靠近输入管脚(4脚)放置5.此处在一层走线即可,建议铺铜处理6.时钟包地需要在地上间隔150mil-200m

晶振下面尽量不要走线2.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍3.器件摆放尽量对齐处理4.电源输入的滤波电容应该靠近输入管脚(4脚)放置5.此处一层连通无需打孔6.线宽突变,确认一下具体线宽,尽量保持统一7.时钟包地上间隔需

自从美国商务部发布了主要针对DRAM芯片和NAND闪存芯片的中国技术出口限制,该限制内容为芯片制造商在采购生产设备时,若涉及到美国供应商,将受到严格审查,涉及范围有18nm或以下的DRAM芯片、128层或以上的NAND闪存芯片、14纳米或以

PCB的阻焊层(solder mask),是指印刷电路板子上要上绿油的部分。阻焊开窗的位置是不上油墨的,露出来的铜做表面处理后焊接元器件的位置,不开窗的位置都是印上油墨的防止线路氧化、漏电。PCB阻焊层开窗的三个原因1.孔焊盘开窗:插件孔焊

电源输入电容应该靠近管脚放置输出电容电阻应该靠近管脚放置到电感后面输出3.3v晶振布局错误,晶振的一对线要走成类差分的形式, 线尽量短如下图。typec的LCD_R4、LCD_R5要走差分阻抗控制90欧姆做对内等长,差分走线尽量减少打孔换层

晶振布局、布线错误,晶振的一对线要走成类差分的形式, 线尽量短如下图。typec的LCD_R4、LCD_R5要建立差分对走差分阻抗控制90欧姆做对内等长,换层需要靠近过孔打回流地过孔,D7、D8应该尽量靠近typec管脚放置。TF卡所有信号

电源输出的滤波电容要靠近输出管脚放置2.USB的电容放置不到位,应该线经过电容在连接到USB器件,差分出线要耦合出线,走在一起3.器件干涉4.SDRAM的滤波电容尽量保证一个管脚一个5.顶底层器件干涉,顶层器件是插件,你底层也放器件,后期不

自从华为和中芯国际等中企受到美国无理的打压,国人开始重视半导体供应链的独立自主,作为半导体顶层产业的核心集成电路设计产业更是被寄托希望,新的一年,中国集成电路设计产业该如何保持优势,应付未来的挑战?若是要解决现状问题和应对未来挑战,首先要正

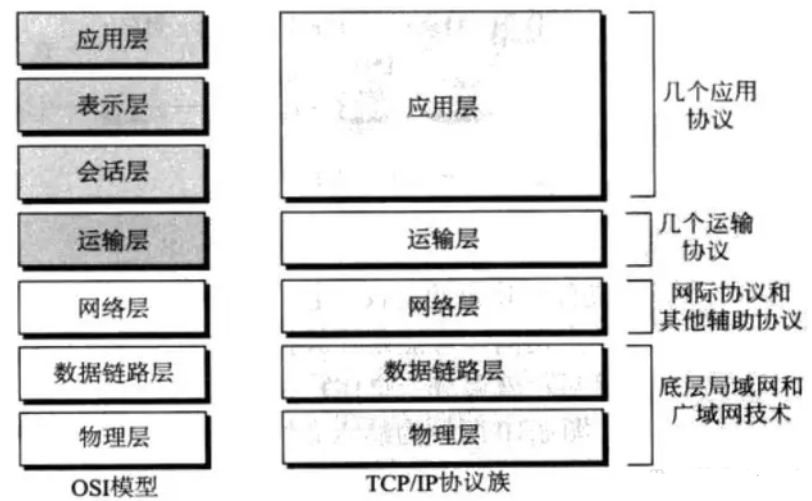

计算机网络是个非常复杂的系统,相互通信的两个计算机必须高达协调工作,但这种协调是很复杂的,分层机制就可以将网络里庞大复杂的问题都转换成若干个局部较小的问题,而这些剧镖较小问题比较易于研究和查找,这也是为什么OSI网络模型和TCP/IP等如此

扫码关注

扫码关注