- 全部

- 默认排序

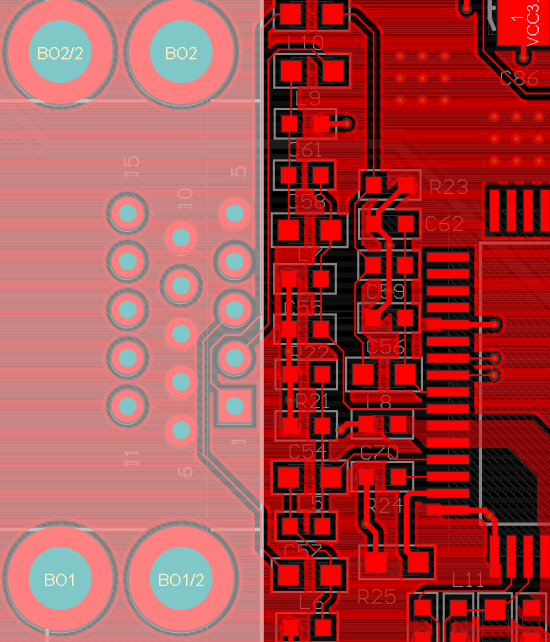

VGA模拟信号要一字型布局,走线加粗处理2.晶振需要走内差分,走线要尽量短,晶振尽量顶层走线,包地要包完整3.差分对内等长不能超过线距的两倍,包地要在地线上打孔4.跨接器件旁边需要多打地过孔,器件摆放可以在优化一下5.反馈需要从最后一个电容

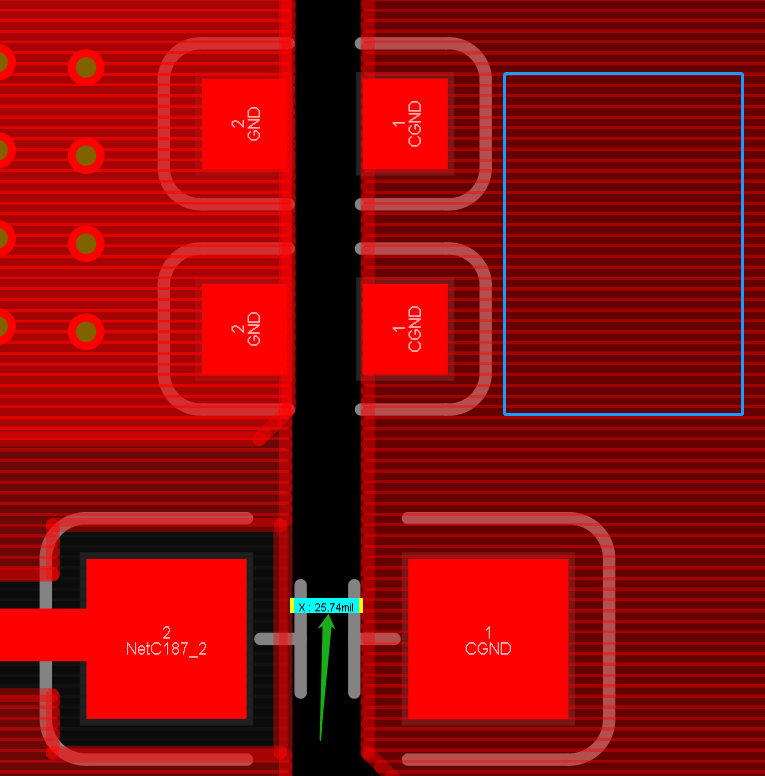

走线并未完全连接,要连接到焊盘中心:注意铜皮尽量钝角,不要直角:铺了铜皮连接,里面就不用走线了:注意电源模块对应的GND过孔也是打在最后一个输出电容的管脚后面:注意下布局,电源模块布局走线优先于主干道,布局布线优先级最高,路径尽量短:电感内

散热孔要两面开窗处理rx等长误差控制在100以内差分这里优化一下以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm?s

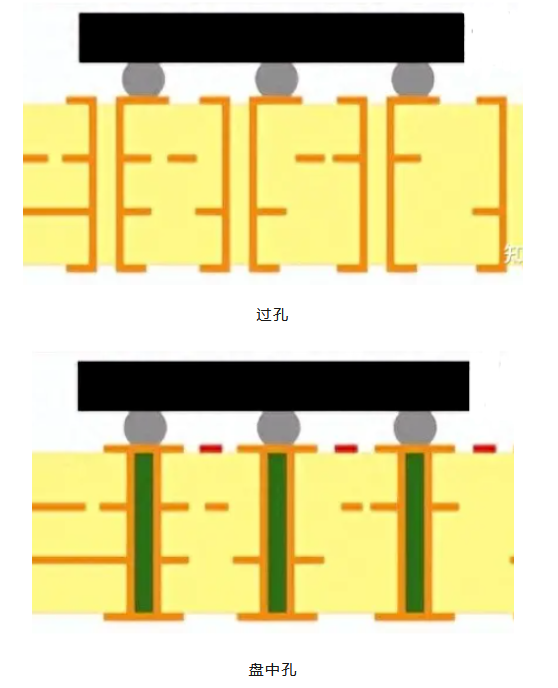

对很多电子工程师来说,DFM(可制造性分析)毫无疑问是PCB设计中的重要组成部分,它可确保电路的性能提升和可靠性,它所涉及的范围非常广,其中之一是很多人都没听说过的盘中孔,下面来介绍下盘中孔,希望对小伙伴们有所帮助。需要注意的是,本文所提到

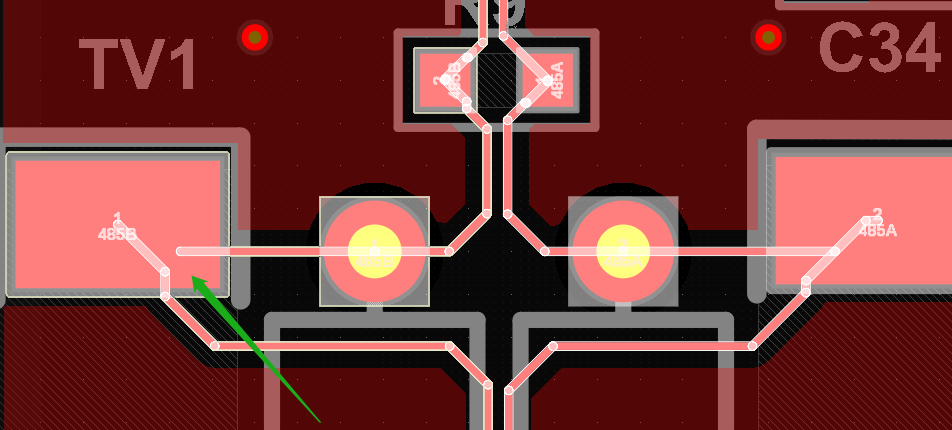

1.差分不耦合,没有差分效果,出焊盘尽快耦合2.差分对内等长不规范,应按照等长规范手动绕线3.差分换层,在过孔旁边打两个回流地过孔,此处rx、tx中间应用地走线打孔隔开4.差分对内等长误差要求控制在5mil范围内5.时钟线包地中间不要插入一

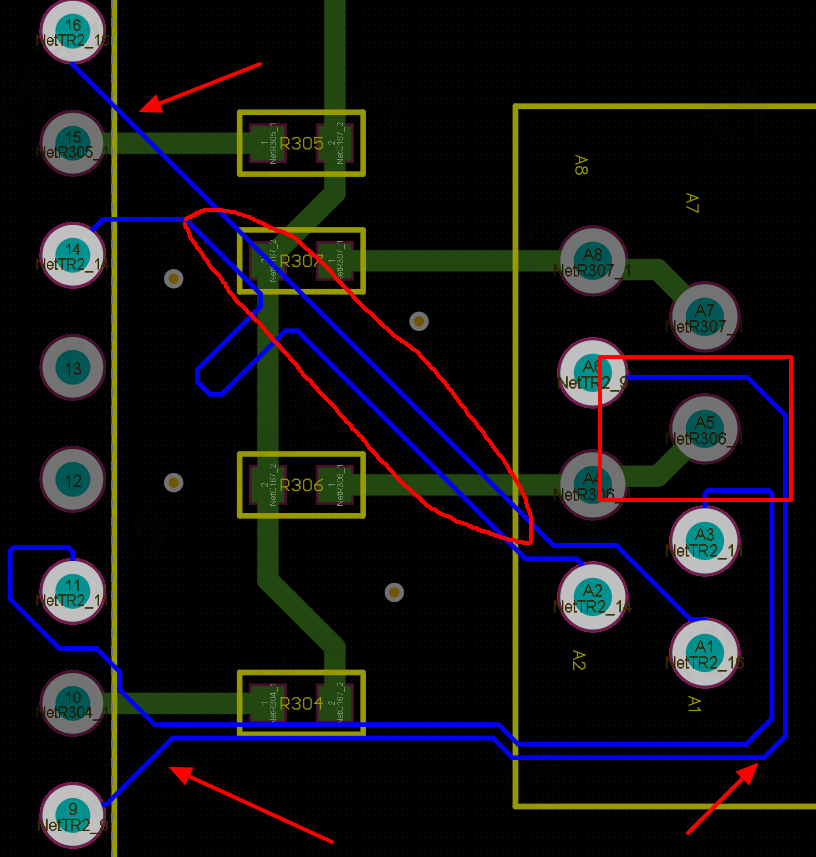

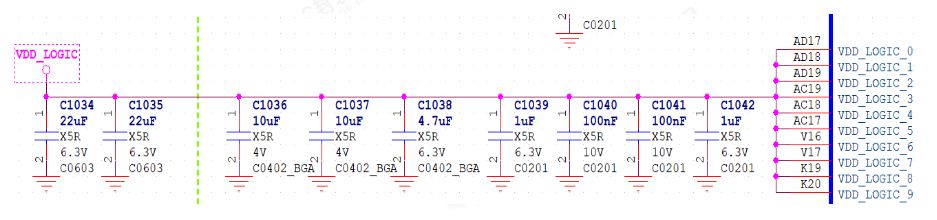

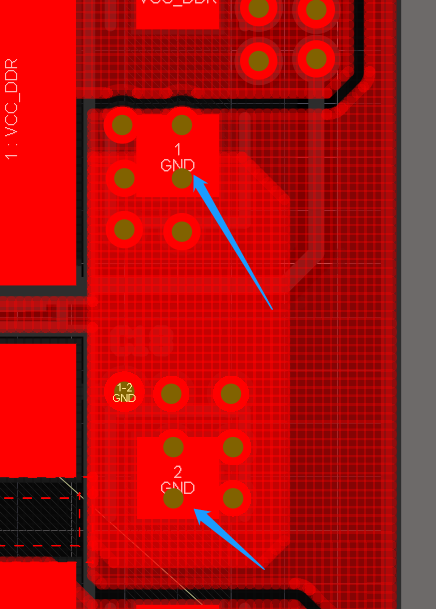

RK3588 VDD_LOGIC电源PCB设计1、VDD_LOGIC的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚路径都足够。2、如图1所示,原理

在电子设备中,PCB板是用于支撑和连接电子元件的关键组件,但如果板上过孔太多,会带来很多不良影响,如信号干扰、微波损耗等,那么针对这个过孔多的问题,如何合理排列使之效率最大化?1、过孔的排列方式有哪些?①直线排列最常见的排列方式,将过孔按照

跨接器件旁要多打地过孔,间距分割要满足2mm,有器件的地方可以不满足2.注意差分换层要在旁边打上回流地过孔3.存在多处开路4.焊盘出现不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.确认一下此处是否满足载流6.RX,TX等长存在

1、VDD_NPU的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。2、VDD_NPU的电源在外围换层时,要尽可能的多打电源过孔(7个以

注意过孔不要上焊盘2.铺铜尽量把焊盘包裹起来,这样容易造成开路3.反馈信号需要走10mil4.电感下面尽量不要走线和放置器件5.注意输入输出要尽量满足载流,载流计算都是以最窄出计算的走线需要优化一下,尽量从焊盘中间出线注意除中间的散热过孔外

扫码关注

扫码关注