- 全部

- 默认排序

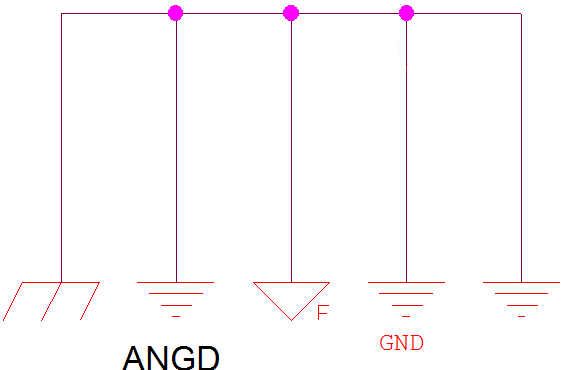

答:我们使用Orcad软件进行原理图的绘制的时候,总会遇到这样的问题:我们有多个地,网络名称是不同的,但是我们后面是统一连接在一起的,这时候最终导入到PCB之后,只会显示一个网络名称,我们想知道最终显示网络名称的优先级是什么呢?我们这里呢,一一给大家揭开这个谜底:第一步,我们绘制这样一张原理图,放置很多地,使用不同的网络名在同一张原理图中,如图3-238所示,它们所连接的网络分别为AGND、GND、GND_EARTH、GND_POWER等; 图3-238 各类不同的地放置示意图第二步,

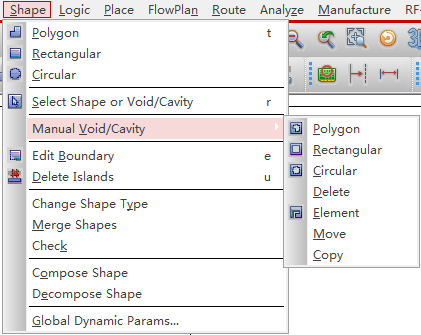

答:在PCB设计过程中,对于大电流的电路或者是网络,我们都会采用铺铜的方式去解决。在Allegro软件中,铺铜的命令有好多个,如图5-126所示,为了更方便的学习好铜皮处理的各个命令,这里我们讲述一下铜皮处理的相关命令具体含义:

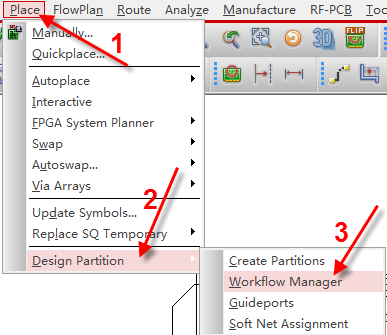

答:我们遇到比较复杂的PCB设计时候,需要我们进行协同设计,分为主设计这以及从设计者,采用的是Allegro软件自带的 Team Design功能,Team Design功能是一种用于团队设计的功能模块,它可将一块复杂的PCB板分成多个部分,通过分区合作设计,在需要的时候可以全自动导入,可以大大提高设计的效率,缩短设计周期。我们下面详细介绍一下Team Design功能的使用,具体如下:

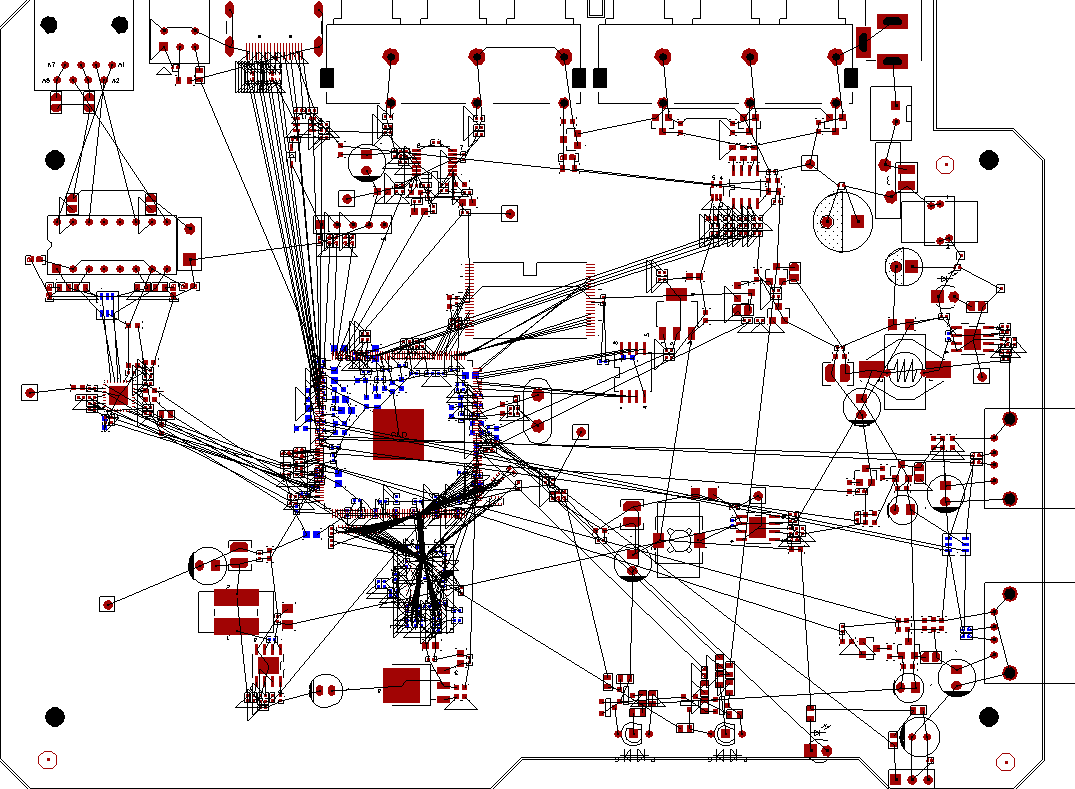

答:飞线,是根据原理图的连接关系,导入到PCB中进行版图设计的一种指引关系,指引PCB工程师去连接不同的网络。这里介绍一下,Allegro软件中显示飞线与关闭飞线的几种方式,具体如下:首先,执行菜单命令,Display-Show Rats,是显示飞线的命令,如图6-70所示,在下拉菜单中有多个选项,我们对几个常用的命令进行介绍;

答:我们在进行设计的时候,如果是在同一层进行铺铜处理,当出现有两个或者两个以上的铜皮重叠的情况出现,如图6-106所示,A铜皮与B铜皮重叠在一起,A铜皮的优先级要高于B铜皮,所以A铜皮是保持原来的形状的,B铜皮会自动避让一块。

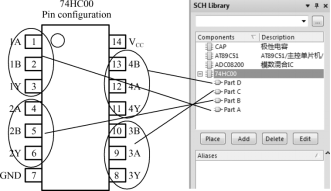

答:当一个元件封装包含多个相对独立的功能部分(部件)时,可以使用子件。原则上,任何一个元件都可以被任意地划分为多个part(子件),这在电气意义上没有错误,在原理图的设计上增强了可读性和绘制方便性。

浪潮集团作为云计算、大数据服务商,旗下拥有浪潮信息、浪潮软件、浪潮国际三家上市公司,业务涵盖云数据中心、云服务大数据、智慧城市、智慧企业等业务板块,形成了覆盖基础设施、平台软件、数据信息和应用软件四个层面的整体解决方案服务能力,全面支撑政府、企业数字化转型,已为全球一百二十多个国家和地区提供IT产品和服务。

二极管选型的多个关键要素

在二极管外加正向电压时,在正向特性的起始部分,正向电压很小,不足以克服PN结内电场的阻挡作用,正向电流几乎为零。当正向电压大到足以克服PN结电场时,二极管正向导通,电流随电压增大而迅速上升。

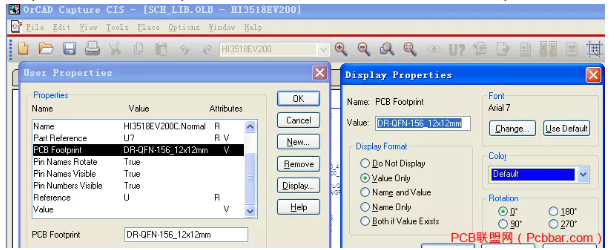

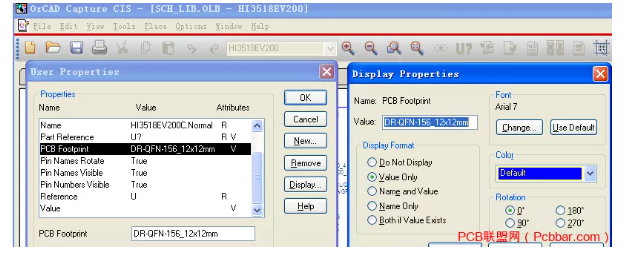

出现的原因:在原理图库中绘制了一个带有多个part的封装(HI3518EV200),但未设置PCB Footprint。在dsn空间的一个原理图内,通过Edit Part修改改器件的PCB Footprint时候,会因为dsn空间内的元器件封装与sch_lib.olb元件库的封装不同,导致会把修改后的封装保存到dsn空间内的Design Cache,并将名字修改为HI3518EV200_x。

出现的原因:在原理图库中绘制了一个带有多个part的封装(HI3518EV200),但未设置PCB Footprint。在dsn空间的一个原理图内,通过Edit Part修改改器件的PCB Footprint时候,会因为dsn空间内的元器件封装与sch_lib.olb元件库的封装不同,导致会把修改后的封装保存到dsn空间内的Design Cache,并将名字修改为HI3518EV200_x。

扫码关注

扫码关注