- 全部

- 默认排序

答:在绘制原理图时,放置出来的元器件,在图纸上都是显示器件的参数的,就是Vaule值,如图2-53所示,对于单个的属性参数,我们双击那个参数,会弹出Display Properties的对话框,如图2-54所示,在下面的对话框选择是否需要显示参数即可,Do Not Display表示都不显示;Value Only表示只显示Value值,也就是封装名称;Name and Value表示都显示。 图2-53 显示参数值原理图部分示意图 图2-54 显示参数设置

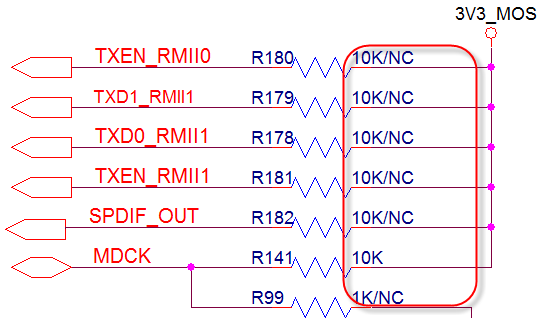

答:orcad当前设计中,所用到库在原理图页面下方的Design Cathe里,在绘制原理图时,可能很多部分是从别的原理图拷贝而来,所以Design Cathe中就会存在一些非法字符,从而影响网表的输出,我们就需要将Design Cathe中的非法字符消除,消除的步骤如下:第一步,点击菜单File→New Library,新建一个库在当前设计的路径下,注意保存的时候不要在路径上出现非法字符,如含有括号、百分号等;第二步,在Design Cathe中找到库路径中含有非法字符的那个库文件,选中库文件

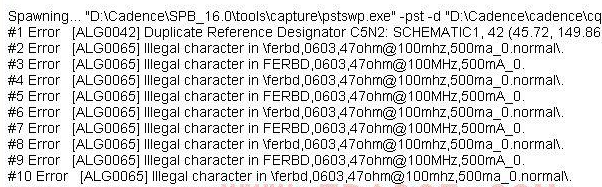

答:orcad进行电气DRC检测时,如图3-64所示,需要对检查的每一项参数进行设置,每个参数的含义如下所示: 图3-64 电气规则检查参数设置示意图Check single node nets:检查设计中的单端网络;Check no driving source and pin type…:检查器件属性无源管脚与有源管脚的连接是否正确;Check duplicate net name :检查重复的网络名称;Check off-page connector connect:检测分页图纸

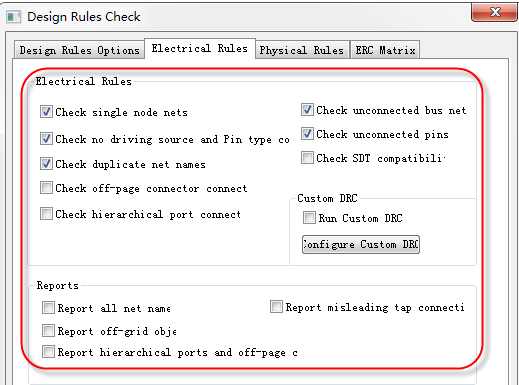

答:层次式电路设计(Hierarchical Design),通常是在设计比较复杂的电路和系统时采用的一种自上而下的电路设计方法,即首先在一张图纸上设计电路总体框图,然后再在另外层次图纸上设计每个框图代表的子电路结构,下一层次中还可以包括框图,按层次关系将子电路框图逐级细分,直到最低层次上为具体电路图,不再包括子电路框图,如图3-107所示,是一个大概的层次式原理图的框架。 图3-107 层次式原理图示意图层次式原理图一种先进的原理图设计方法,使用符号代表功能,并且能够重复

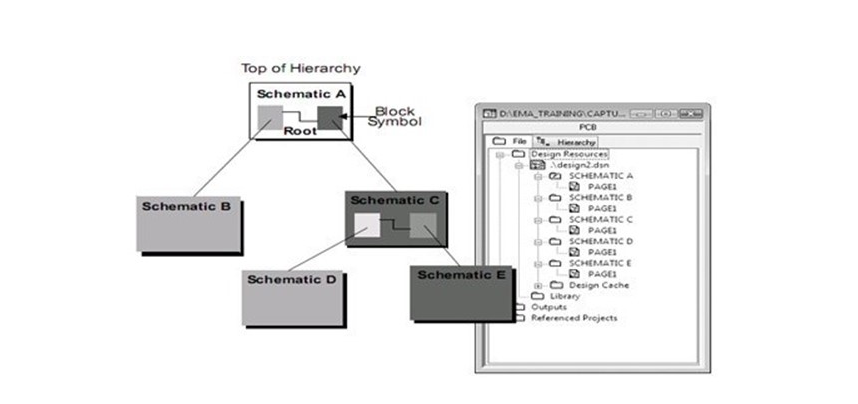

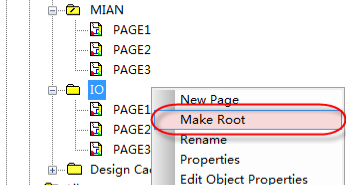

答:在使用Orcad软件绘制原理图时,通常会把一个工程下面对应的不同部分的原理图绘制在一起,如图3-184所示,这样方便后期的检查与查看,这样做有一个问题,你会发现输出网表的时候,不能全部输出,一下子只能输出一个文件的网表。这里我们给大家讲述一下怎么输出所有文件的网表: 图3-184 原理图不同的工程示意图第一步,我们选中原理图的根目录时,点击输出网表的命令,输出的网表都是最上面的那个MIAN的三页图纸的网表;第二步,我们需要输出下面的IO的三页图纸的网表,需要将IO原理图

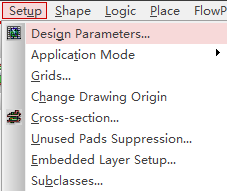

答:我们使用Allegro软件进行设计PCB图纸之前,需要对整个设计的参数进行设置,需要执行菜单命令Setup-Design Parameters,如图5-50所示:

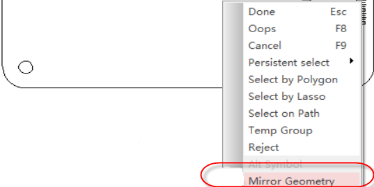

答:一般结构工程师在绘制结构图纸的时候,都会有顶视图与底视图之分,我们导入到PCB之后,是需要将底视图左右镜像处理的,因为PCB里面的背面是从正面透视看过去的,所以将底视图镜像之后,就是是跟PCB界面是一致的,对底层的DXF文件镜像处理的操作步骤,具体如下所示:

常用VIEW视图快捷命令:命令快捷键功能说明适合文件VD当设计图页不在设计目视范围内,可快速归位适合所有对象VF对整个图纸文档进行归位放大Page up以鼠标指针为中心进行放大缩小Page down以鼠标指针为中心进行缩小选中的对象VE可以

1开关电源设计前各参数以NXP的TEA1832图纸做说明。分析电路参数设计与优化并到认证至量产。所有元器件尽量选择公司现有的或者量大的元件,方便后续降成本。●输入端:FUSE选择需要考虑到I^2T参数。保险丝的分类,快断,慢断,电流,电压值

电路图,是通过电路元件符号绘制的电子元件连线走向图,它详细的描绘了各个元件的连线和走向,各个引脚的说明,和一些检测数据。PCB图,是电路板的映射图纸,它详细描绘了电路板的走线,元件的位置等。看电路图首先看电源部分,理解电路在什么电源的情况下

扫码关注

扫码关注