- 全部

- 默认排序

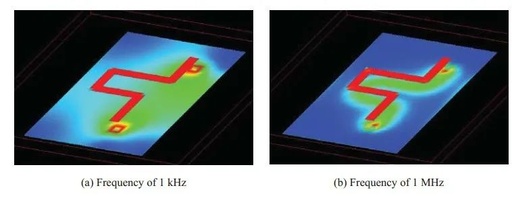

电流的路径是个环路。因此,每个电流信号有来肯定有回。要获得最佳的PCB设计,需要了解信号的回流的实际路径。电路的信号完整性和EMC性能,直接与电流环路形成的电感相关,而电感大小则主要与环路的面积相关。在做PCB设计时,比较容易忽略回流的实际路径,因为它不像信号路径(通常是微带线)那么形象。微带线的回

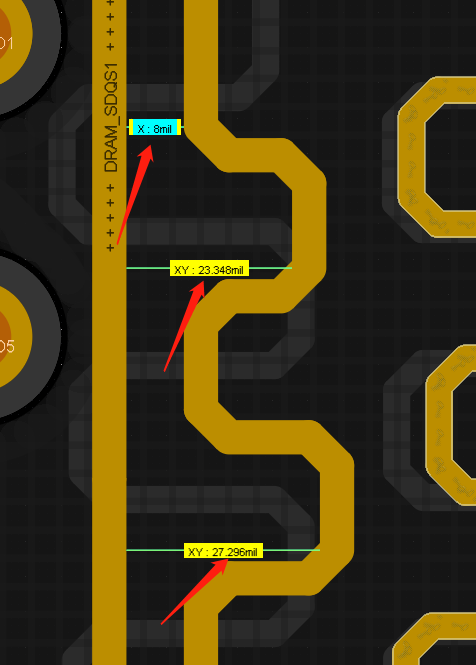

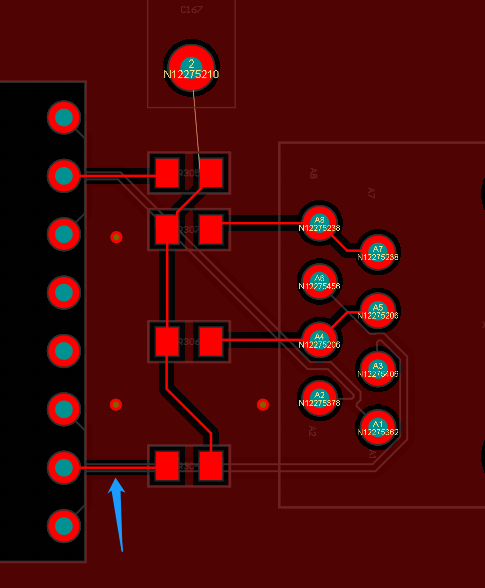

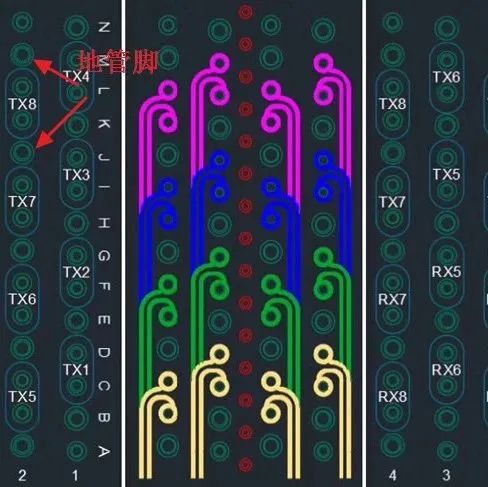

差分对内等长凸起高度不能超过线距的两倍2.注意T点的间距要求,后期自己看视频在了解一下3.地网络需要就近打孔,缩短回流路径4.VREF的电源最少要加粗到15mil以上5.此处不满足载流6.注意差分走线要尽量耦合,满足差分间距要求,控好阻抗7

EMC的PCB设计技术

除了元器件的选择和电路设计之外,良好的印制电路板(PCB)设计在电磁兼容性中也是一个非常重要的因素。PCB EMC设计的关键,是尽可能减小回流面积,让回流路径按照设计的方向流动。最常见返回电流问题来自于参考平面的裂缝、变换参考平面层、以及流经连接器的信号。跨接电容器或是去耦合电容器可能可以解决一些问

布局没什么问题。拉出焊盘之后注意差分走线保持耦合,重新走下:差分打孔换层两侧打上地过孔,缩短回流路径:建议差分每组直接走GND线包地处理:差分从过孔拉出注意耦合, 连接处重新走下:差分组组内等长误差没什么问题了。以上评审报告来源于凡亿教育9

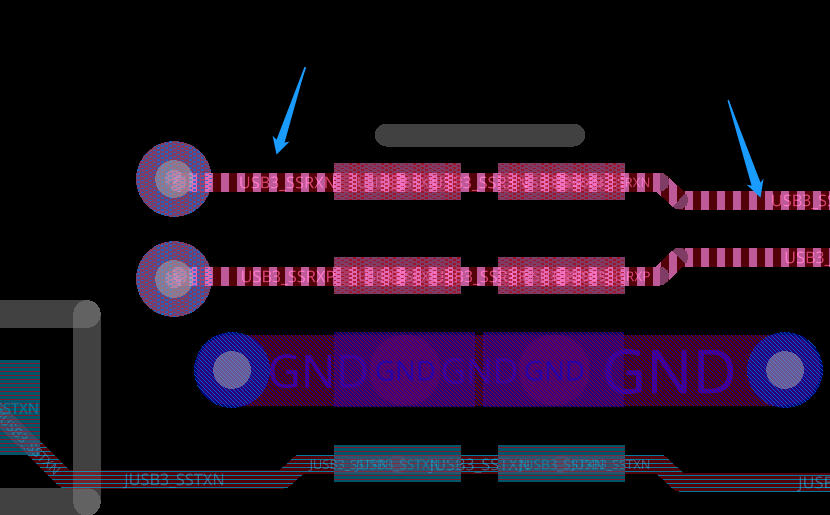

还存在飞线,注意电源信号处理:差分打孔换层的过孔两边注意添加地过孔,缩短回流路径:注意差分对内等长误差为5MIL:差分组跟组不用等长,组内等长就可以了:单端信号的TX RX需要组内等长,没有设置:自己后期去设置下组内等长,在拉等长。以上评审

差分信号打孔换层 注意两侧打上地过孔,缩短回流路径:注意器件尽量整体中心对齐:过孔注意间距,不要造成平面割裂:变压器上除了差分信号 其他的加粗20MIL:差分对内等长误差控制在5MIL:RX TX需要对内做等长以上评审报告来源于凡亿教育90

网口除差分信号外,其他的都需要加粗到20mil2.差分信号需要进行对内等长,误差5mil3.存在多处开路4.焊盘尽量从四个角出线,后期自己优化一下5.地焊盘需要就近打孔,缩短回流路径6.焊盘出现不规范,焊盘中心出线至外部才能拐线处理,避免生

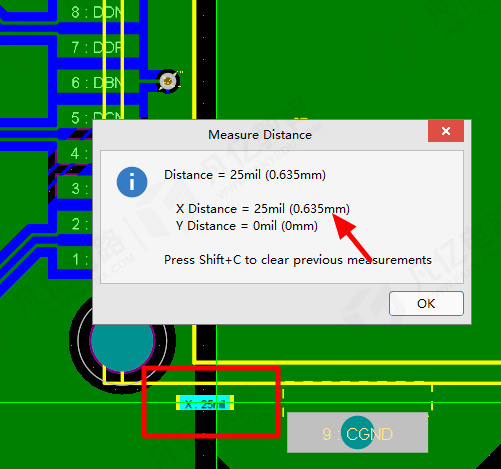

cgnd到gnd分割距离要2mm以上cgnd到gnd跨接处,两端多打过孔底层gnd铜皮被走线分割,导致多处孤岛铜皮,两层板尽量走线在一层,留一个尽量短的回流路径过孔不要上小器件焊盘多处尖岬铜皮等长绕线不要绕出直角以上评审报告来源于凡亿教育9

建议顶底层可以铺上大地铜:铜皮注意这种尖角:注意此处的铜皮 不要铺到晶振内部,晶振需要净空:晶振包地处理沿着器件丝印边框打孔:跨接器件两边可以多打地过孔:差分打孔换层的两侧可以放置地过孔,缩短回流路径:此处晶振净空调整下:等长之间注意保持3

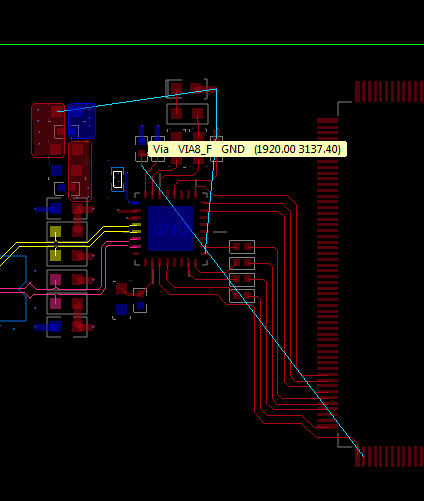

PCB工程师注意啦:通常pcb上的打过孔换层会引起镜像平面的非连续性,这就会导致信号的最佳回流途径被破坏。我们都知道,信号打孔换层会改变信号的回流路径,如果信号换层,回流路径也跟着换层,但是在信号换层处过孔不能将信号回路连通起来,将引起信号回路面积增大,从而导致EMC问题。如下图所示,描述了信号打孔

扫码关注

扫码关注