- 全部

- 默认排序

随着FPGA的不断开发,其功能越来越强大,也给其布线带来了很大的便捷性—管脚的调整。 对于密集的板卡,走线时可以不再绕来绕去,而是根据走线的顺序进行信号的调整,然后通过软件编程来校正信号的通信就可以了。在调整FPGA管脚之前必须熟悉几点注意事项。

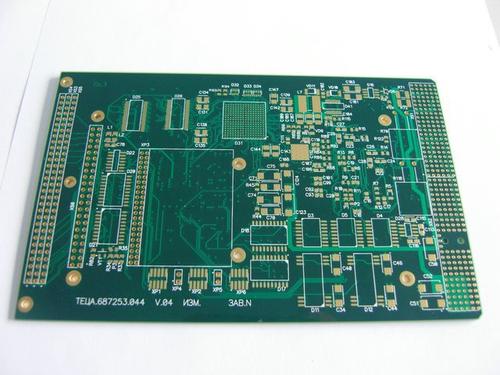

一、8 层 Allegro T 点星型拓核心板课程详情这个是一个非常经典的 T 点星型拓核心板设计,主要采用飞思卡尔 IMX6 主控芯片,4 片DDR3 同层设计,采用 DDR3 常见的 T 点拓扑结构,讲解了 DDR3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等。

此Altium Designer视频是专门针对 DDR3 设计来的,采用飞思卡尔 IMX6 主控芯片, 4 片 DDR3 同层设计,采用 DDR3 常见的 T 点拓扑结构,一个大 T 点两个小 T 点的方式。讲解了 DDR3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等,让学习者知其然知其所以然。

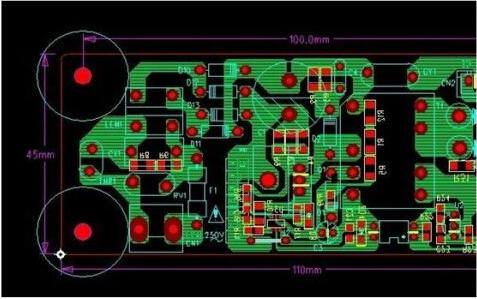

一、课程详情这个是一个Cadence Allegro非常经典的 6 层一阶盲打孔设计,基于三星系列 S3C6410 ,全程讲解了通过Cadence Allegro,运用-阶盲埋孔的技术进行工控核心板卡的 PCB 设计教程视频,从前期的原理图导入,到后期输出生产文件( GERBER)的全过程。

一、PADS8层DDR3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层PCB设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

扫码关注

扫码关注

![电子设计:FPGA入门有哪些关卡?[零基础学FPGA设计-理解硬件编程思想]](https://api.fanyedu.com/uploads/image/46/fea5fd3cf4173d2a32b854a34fbeb9.png)