- 全部

- 默认排序

本文使用两个示例演示了如何使用ZPL创建用户自定义解。 第一个示例介绍了如何创建ZPL解以确保序列文件中像面的曲率半径等于系统的Petzval曲率。第二个示例介绍了如何在非序列元件编辑器 ( Non-Sequential Component

本文介绍如何使用Zemax编程语言 (ZPL) 创建宏来计算和绘制用户自定义的性能指标。 在本示例中,系统的环带垂轴色差 (Zonal Transverse Chromatic Aberration, ZTCA) 将被分析。在解释了需要使用

4月14日,为充分发挥劳模和工匠人才、工会先进集体和个人示范引领作用,树立典型、鼓励先进,全面推进福田区劳模和工匠人才创新工作室创建和福田区工会组织建设工作,深圳市福田区2023年劳模和工匠人才创新工作室现场交流会在新一代产业园召开。福田区

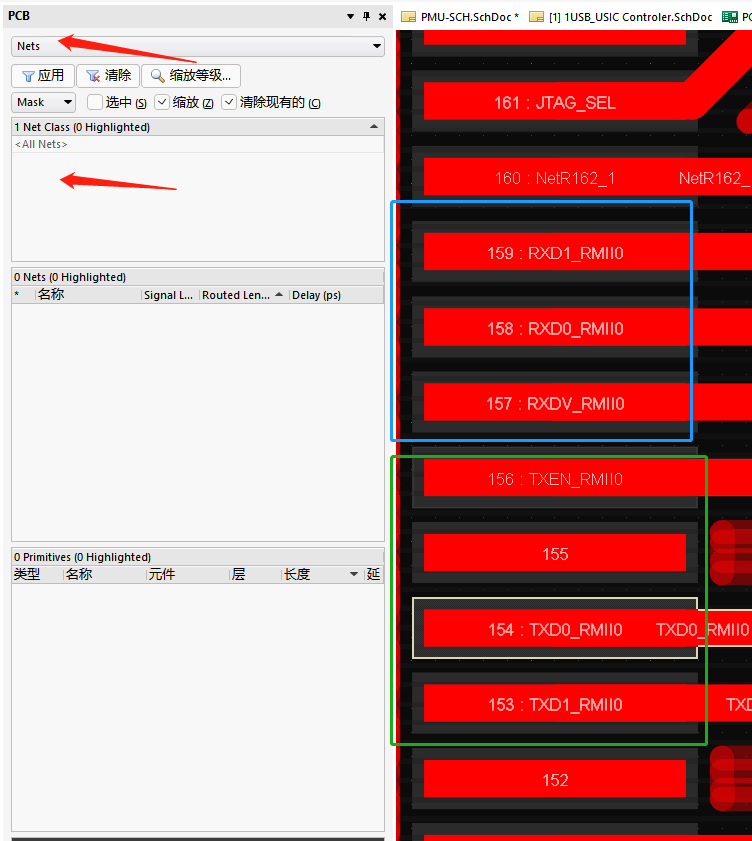

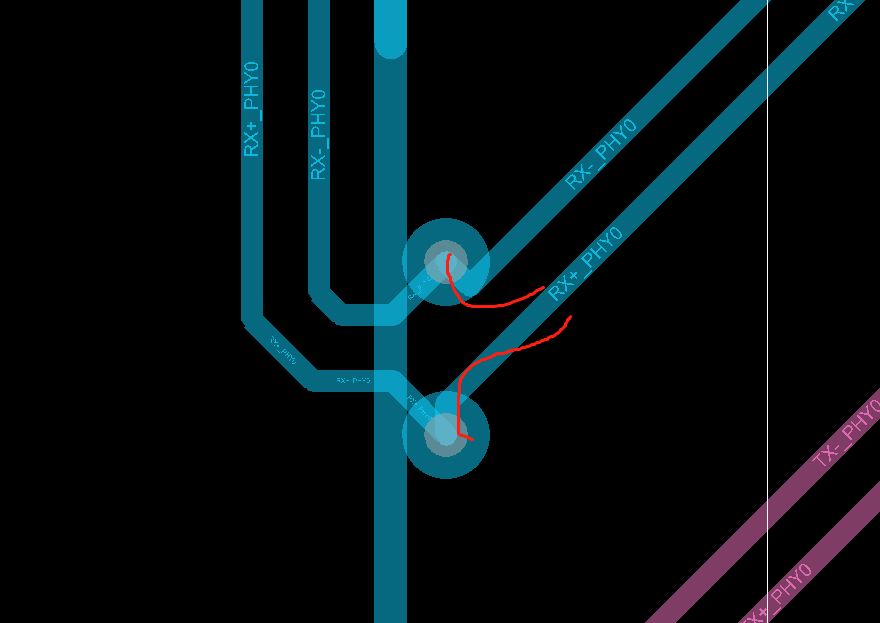

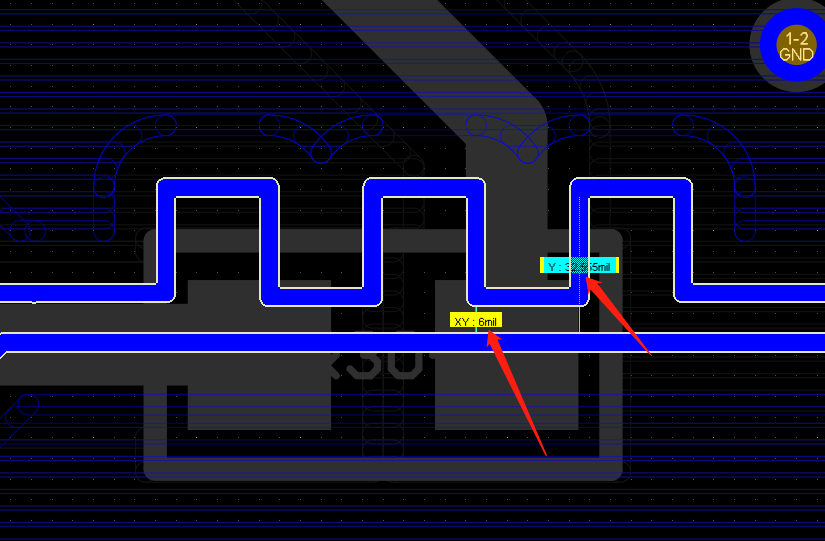

未创建TX和RX的class,分别等长误差100mil2.时钟信号要进行连通并包地处理3.焊盘出现需要优化一下4.变压器所有层需要挖空处理5.差分对内等长误差5mil6.差分出线要尽量耦合7.没有添加差分对的class8.pcb上存在多处开

跨接器件旁边尽量多打过孔,地分割间距尽量1mm,有器件的地方不满足可以忽略2.差分对内等长误差5mil3.差分走线需要优化一下4.晶振走内差分,需要包地处理5.走线没有连接到焊盘中心,存在开路6.未创建RX和TX class,误差范围100

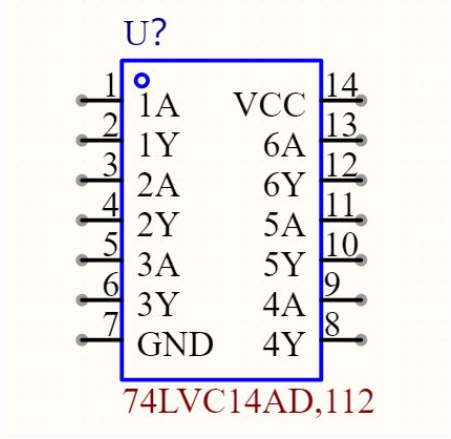

一、元件符号概述如图1所示,元件符号是元件在原理图中的表现形式,主要由元件边框、管脚(包括管脚符号和管脚名称)、元件名称及说明组成,通过放置的管脚来建立电气连接关系。元件符号中管脚序号是和电子元件实物的管脚一一对应的。在创建元件的时候,图形

一、PCB布局和组装PCB设计的第一步都是创建电路图,一旦电路图完成,PCB设计和布局阶段开始。任何电路设计都是在纸上或电路设计软件中呈现,以便于理解,但对于PCB设计却可以不必满足此类要求。尽管电路图和PCB设计上的连接保持不变,PCB布局功能更强大,旨在节省空间并遵循不同的指导原则。有许多不同

1.差分走线要注意耦合2.RX和TX需要创建等长组进行分别等长3.小电容靠近管脚摆放4.注意走线不要有小线头以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item

通过在建筑内集成各种系统,工程师可以设计出能够应对未来的建筑。智能建筑洞察工程师和设计师必须实现两件事才能创建智能建筑。智能建筑有助于提高能源效率,因为所有工程系统都受到控制和测量。想象一个带有智能控件的工作区。通过与Microsoft O

差分线锯齿状等长不能超过线距的两倍2.差分对内等长误差5mil3.差分出线要尽量耦合4.走线需要优化一下5.RX和TX要创建class,进行等长处理,误差100mil6.时钟信号需要包地处理7.注意除了散热过孔其他的都可以盖油处理8.注意线

扫码关注

扫码关注