- 全部

- 默认排序

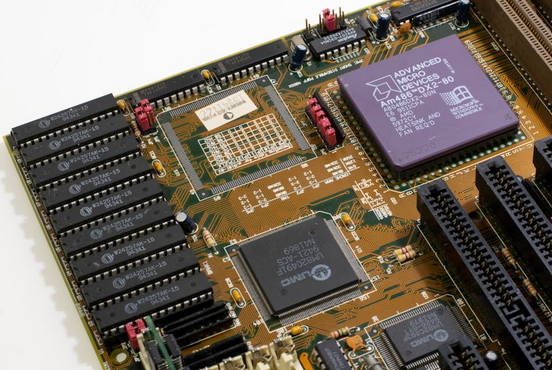

仅看近30年的发展,以PC为代表的行业几度繁荣而后归于平静,从最早的百兆级处理器速度倍频直到今天的几个GHz级别,总线位宽从16位扩展到今天的64位,以Intel为首的行业龙头公司将CPU的处理能力整整提升了成百上千倍。 在总线宽度和处理器速度达到瓶颈后的近10年里,整个行业将突破的战场放在了高速接口上,外部串行高速接口的速率从Gbps迅速飞升到几十个Gbps,为了实现更高的吞吐量,还采用了复杂的高阶调制和增加链路宽度的办法。这一切简直是以“迅雷不及掩耳盗铃之势”汹涌而至,作为“攻城狮”的你做

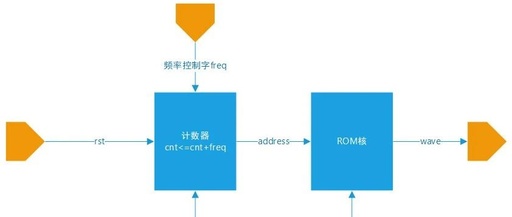

【通信篇】DDS信号源

DDS信号发生器简介DDS即为直接数字频率合成(Direct Digital Synthesis)技术,借助DDS技术和数模转换器,能够输出任意形状、任意频率的波形。DDS在实现信号发生器制作、信号倍频,以及在调制系统中产生载波等方面具有重要作用。DDS信号发生器原理 如何输出任意波形输出任意波形的

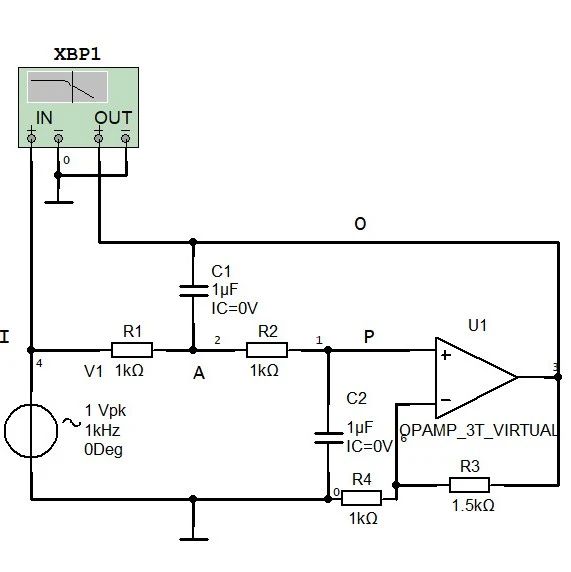

滤波器的阶数越高,则可以得到越陡峭的频率响应,使得在通带内尽量不衰减信号,而在阻带内尽可能多地衰减信号。上一节我们讲的一阶有源滤波器,在对数坐标系上,其阻带内的衰减是20dB/十倍频程;如果想要更好的衰减效果,需要用更高阶的滤波器。1)二阶有源低通滤波器一种最简单的二阶滤波器如下图:其实质是两个一阶

锁相环(PLL)是一种反馈控制电路,通过不断比较外部参考信号和内部振荡信号的频率与相位,进而调整内部振荡信号的参数,以此实现两者之间的同步,在需要调整输出频率的倍数时,锁相环有特定技术来实现倍频功能,那么这个技术是如何实现?1、锁相环的基本

开发板使用LPC2136芯片,晶振采用14.7456MHz的,后来改成10.0000MHz就出错了, 使用14.7456MHz时参数如下: #define Fosc 14745600 #define Fcclk (Fosc * 3) #define Fcco (Fcc

扫码关注

扫码关注