- 全部

- 默认排序

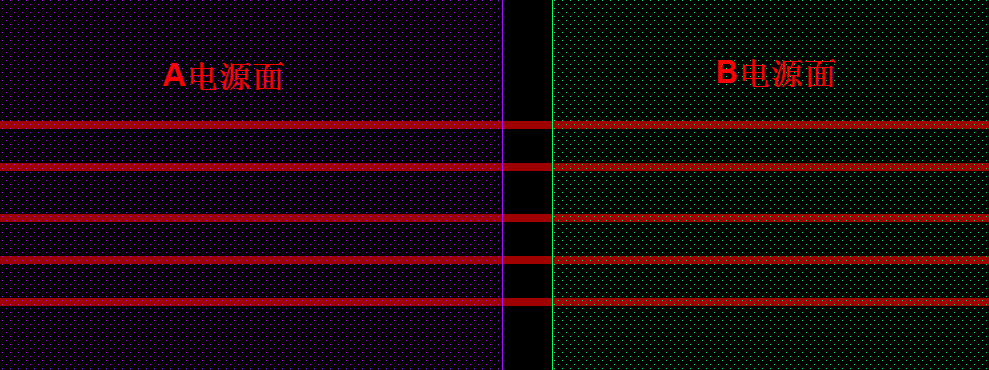

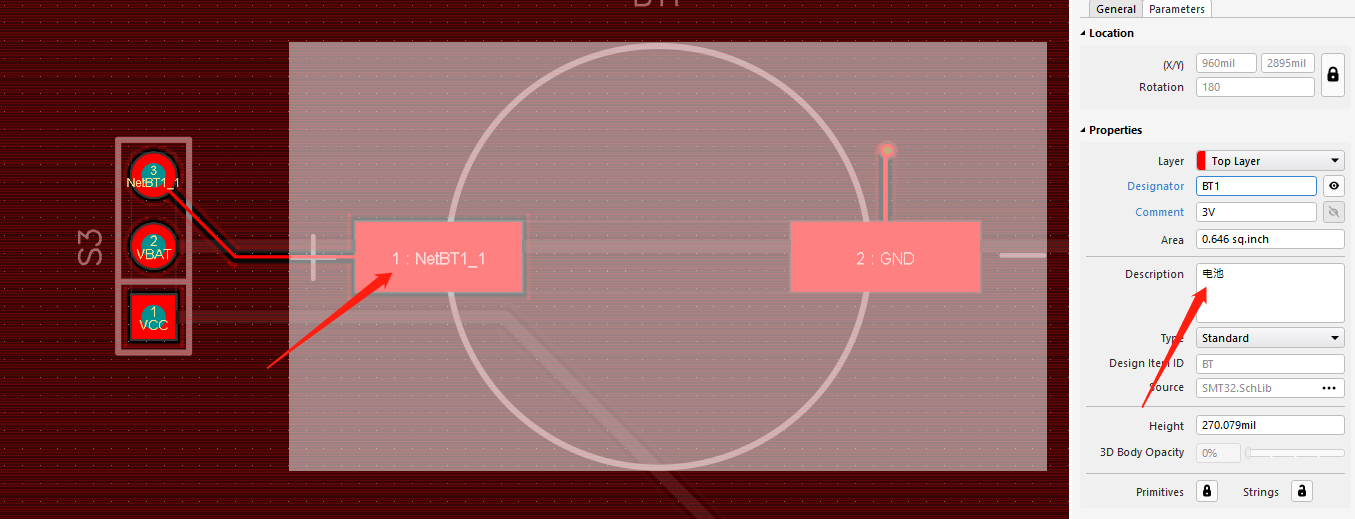

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。

在高速PCB设计中,差分信号(DIFferential Signal)的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。为什么这样呢?和普通的单端信号走线相比,差分信号有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。差分信

在高速PCB设计中,差分信号(Differential Signal)的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计。为什么这样呢?和普通的单端信号走线相比,差分信号有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。布线要

2层stm32开发板评审

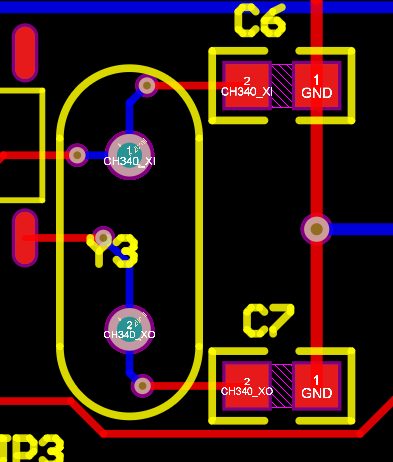

晶振这里不用打过孔进行换层,晶振要包地处理并打地过孔晶振的走线要类差分走线走线不要从焊盘中间出现容易造成虚焊。确认电源部分的走线是否满足载流要求485的信号走线100R差分或者走加粗类差分处理232这里所接的电容属于升压电容走线需要加粗处理

地缘信号走线需要加粗处理,尽量满足载流2.SD卡需要靠近板框放置3.SD卡信号线需要进行等长处理,误差300mil4.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.晶振需要走内差分,并包地处理,在地线上均匀的打上地过孔

在PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割现象示意图跨分割,对于低速信号可能没有什么关系,但是在高速

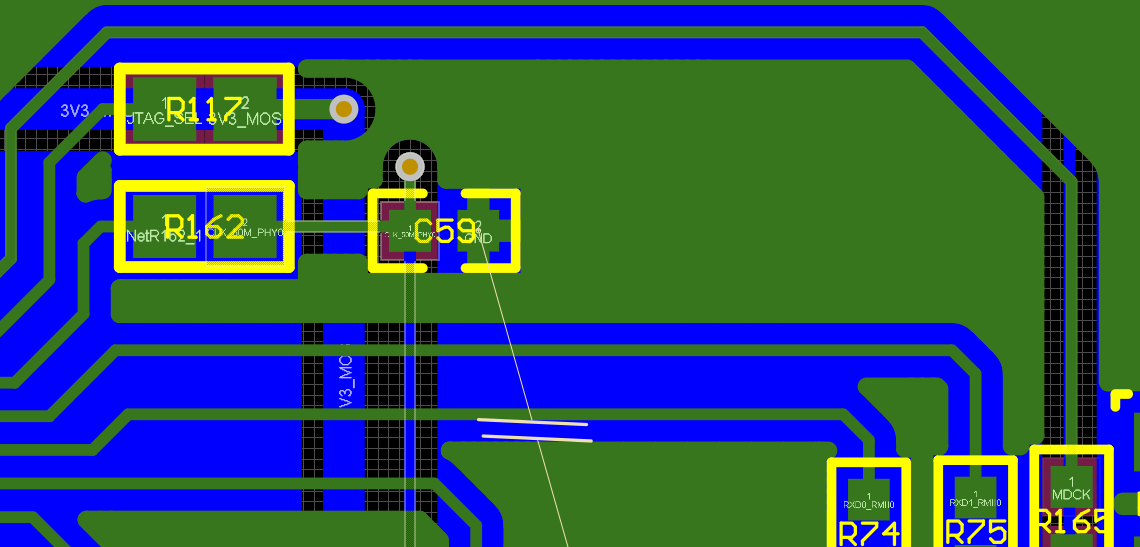

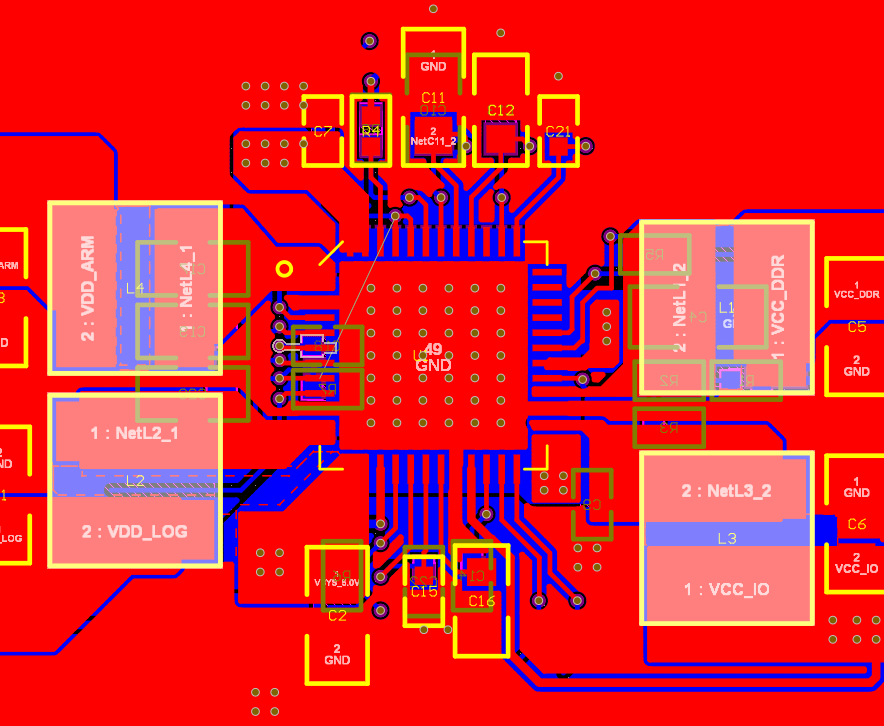

1.存在开路,孤岛铜皮没有连接出去。2.芯片中间过孔没有连接出去导致天线报错。3.多处孤岛铜皮和尖岬铜皮。4.电容地网络要和电源一样加宽载流。5.差分焊盘出线尽量耦合6.差分走线不耦合7.时钟信号走线要包地处理8.走线尽量短9.TX、RX没

随着信号上升沿时间的减小,信号频率的提高,电子产品的EMI问题,也来越受到电子工程师的重视。高速pcb设计的成功,对EMI的贡献越来越受到重视,几乎60%的EMI问题可以通过高速PCB来控制解决。1高速信号走线屏蔽规则如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果

注意地址线之间等长需要满足3W2.电感中间挖空,中间就尽量不要铺铜,后期自己调整一下3.模拟信号走线需要加粗反馈线需要加粗到10mil.丝印,过孔尽量不要上焊盘5.过孔需要盖油处理6.顶层BGA里面额铜可以挖掉以上评审报告来源于凡亿教育90

电感底部不能放置器件以及走线,重新布局下,可以将电容塞到芯片底部:这种孤铜都去除下:走线注意规范不要出现锐角以及直角:DCDC输出主干道的铜皮尽量加宽一点:放置完铜皮挖空之后需要重新灌铜才能自动避让挖空区域:反馈信号走线又是直角:铺铜也注意

扫码关注

扫码关注