- 全部

- 默认排序

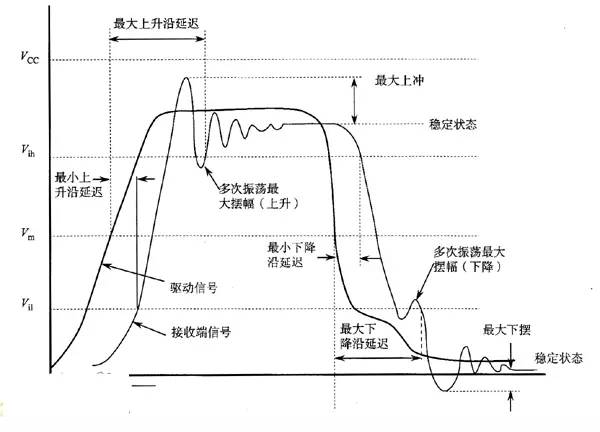

信号完整性的定义定义:信号完整性(Signal Integrity,简称SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同引起的。当电路中信号能以要求的时序、持续时间和电压幅度到达接收端时,该电路就有很好的信号完整性。当信号不能正常响应时,就出现了信号

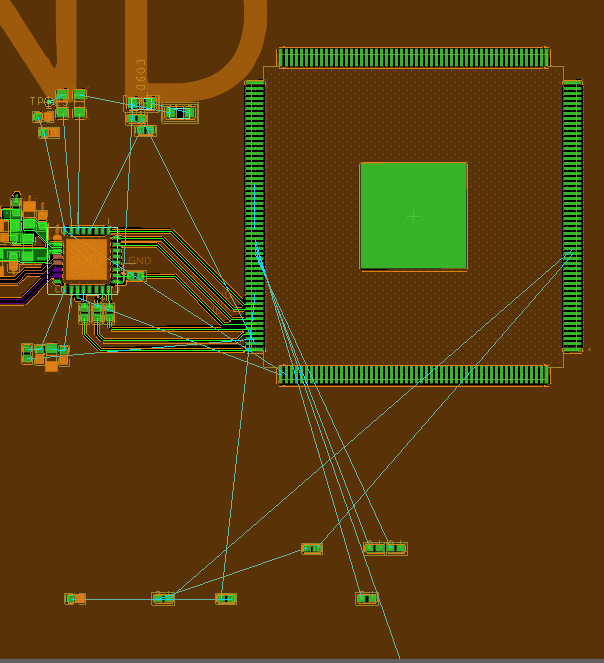

数据线分组错误,一组应该是9根信号线2.注意数据线等长之间需要满足3W规则3.短接网络进行等长的,后期记得更新一下pcb,恢复正常网络4.地网络需要就近打孔,或者调整一下布局利用BGA里面地网络,尽量保证一个焊盘一个过孔以上评审报告来源于凡

器件跟信号线还没有设计完全:器件之间注意间距,不要干涉了:注意器件需要整体对齐处理:此处器件重新放置下,注意整体对齐:器件就近IC管脚边放置:后期自己重新整体布局都优化下。差分打孔换层两边注意放置GND过孔:差分走线一定要耦合,此处完全不耦

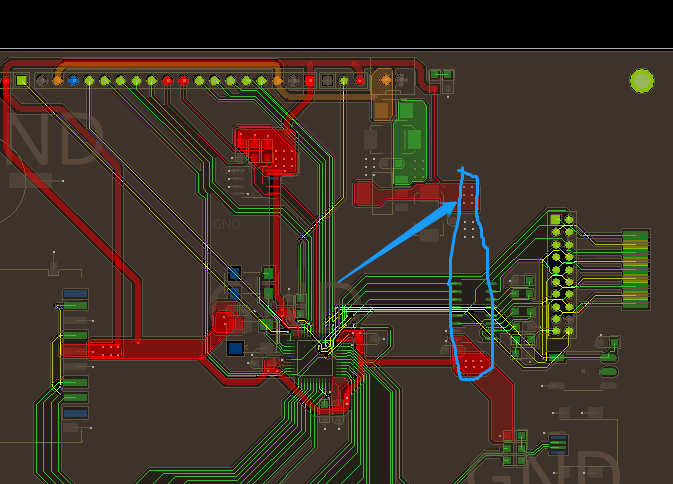

电源输出要从输出电容后面进行连接2.晶振需要包地处理,下面不要走别的信号线,包地需要打孔3.RS232 的升压电容走线需要加粗处理4.电源走线尽量加粗导20mil,满足载流5.USB尽量包地处理,并间隔100-150mil打上地过孔6.注意

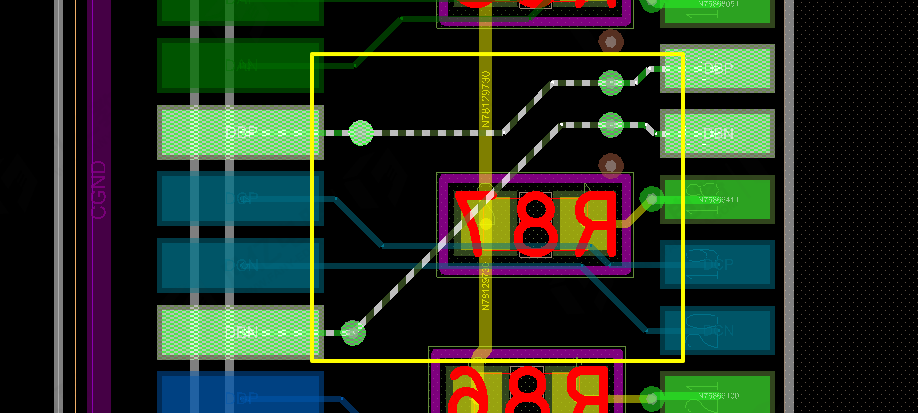

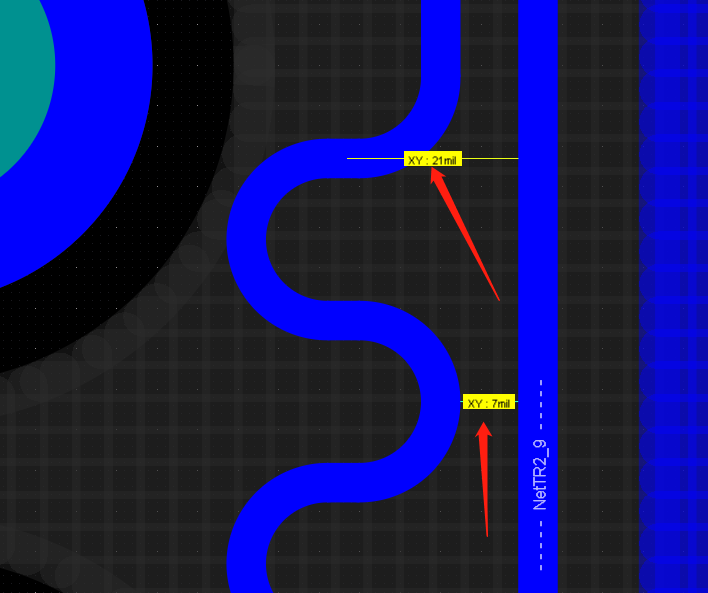

差分走线尽量耦合差分应建立对内等长规则控制对内等长5mil误差范围变压器除差分对以外所有走线加粗到15mil以上晶振布线应走类差分形式芯片主电源输入走线应加粗过孔到焊盘应保持一定间距,不要靠的太近以太网芯片到CPU的RX、TX信号线要分别建

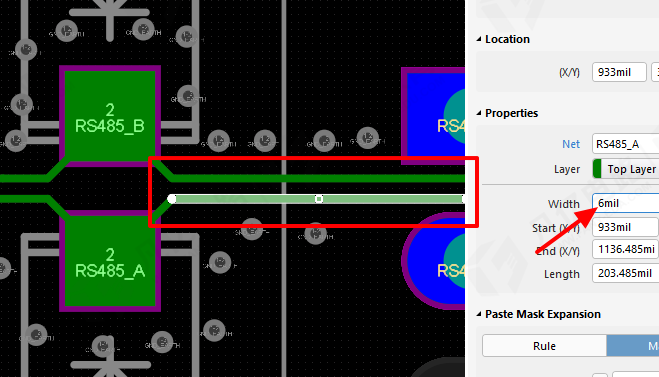

485信号线应按加粗类差分处理,走线最少加粗到8mil以上232的C+C- V+V-所接电容属于升压电容,走线按电源走线加粗tx、rx信号走线用gnd打孔隔开以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程

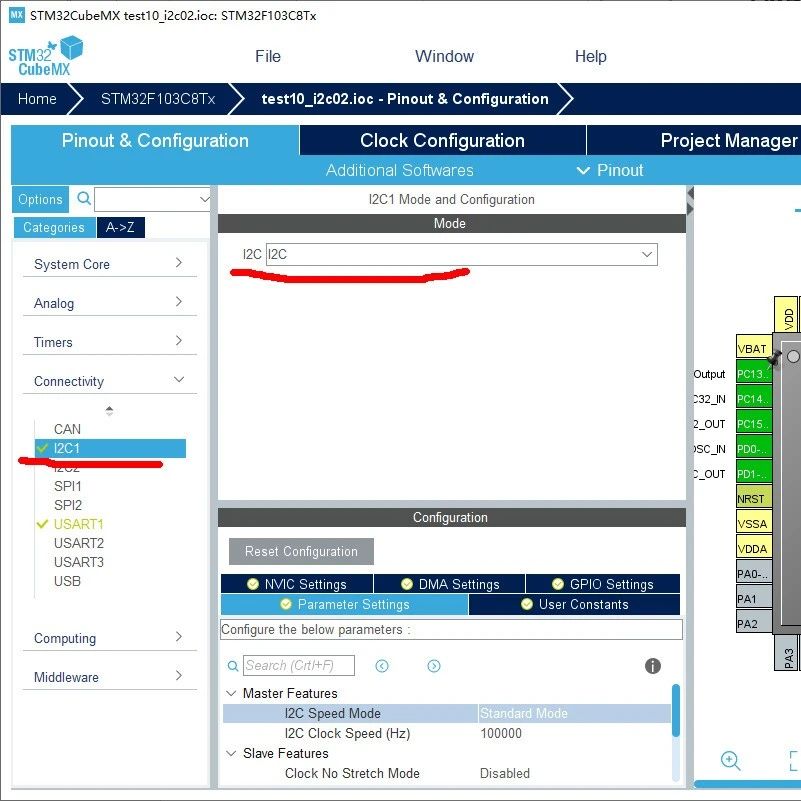

本节我们介绍I2C总线,并使用stm32的I2C总线来访问加速度传感器ADXL345。1)I2C基础知识I2C总线通信比较适合设备内部各芯片间的通信,它只需要两根信号线。I2C可以挂载多个主机和从机,通信总是由主机发起。每个从机都有唯一的地址,主机通过地址决定访问哪个从机。I2C总线的两根线,SCL

在设计PCB时,经常会遇到高速差分线,比如USB、HDMI、LVDS、以太网等等,高速差分线不仅要求信号线的正端和负端信号线宽及线间距保持一致,还需要对差分信号线进行阻抗控制。控制差分信号线的阻抗,对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰

注意差分对内等长凸起高度不能超过线距的两倍2.变压器需要挖空所有层处理3.焊盘里面不要出现多余的线头4.电容靠近管脚摆放,均匀分配5.变压器挖空里面尽量不要走线6.注意tx分组少信号线7.焊盘要开窗处理,要不然不能进行上锡焊接,后期自己处理

在电子电路中,很多大佬会经常串联小电阻,保持后续的项目进行,当然很多电子小白不太清楚,其背后蕴含着多种功能及作用。1、分压作用串联在电路中的电阻,无论其阻值大小,都会起到分压的作用。这是因为在串联电路中,各电阻上的电流是相同的,而电阻两端的

扫码关注

扫码关注