- 全部

- 默认排序

硬件电路设计如何少走弯路

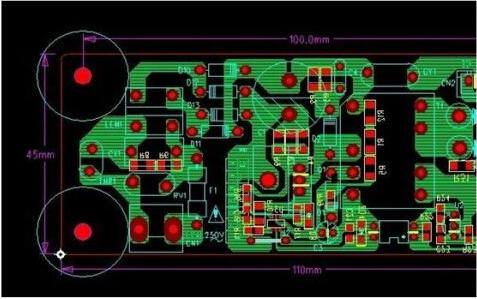

在网上许多关于硬件电路的经验、知识让人目不暇接。像信号完整性,EMI,PS设计准会把你搞晕。别急,一切要慢慢来。 凡亿PCB视频教程小编想通过和大家探讨一些自己关于硬件电路设计方面的心得,来个“抛转引玉”,献给那些刚开始或即将开始设计硬件电路的人,让大家在“硬件电路设计”这条路上少走“弯路”。1总体思路设计硬件电路,大的框架和架构要搞清楚,但要做到这一点还真不容

在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错。那么如何区分高速信号和普通信号呢?很多人觉得信号频率高的就是高速信号,实则不然。我们知道任何信号都可以由正弦信号的N次谐波来表示,而信号的最高频率或者信号带宽才是衡量信号是否是高速信号的标准。在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错

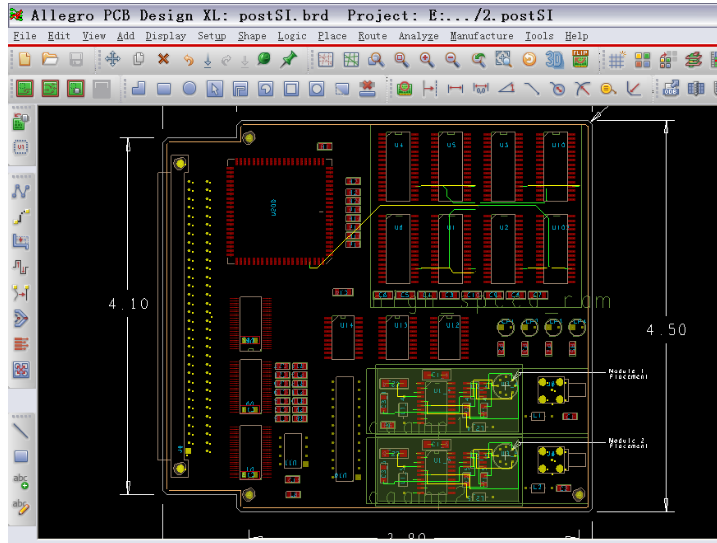

一、8 层 Allegro T 点星型拓核心板课程详情这个是一个非常经典的 T 点星型拓核心板设计,主要采用飞思卡尔 IMX6 主控芯片,4 片DDR3 同层设计,采用 DDR3 常见的 T 点拓扑结构,讲解了 DDR3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等。

此Altium Designer视频是专门针对 DDR3 设计来的,采用飞思卡尔 IMX6 主控芯片, 4 片 DDR3 同层设计,采用 DDR3 常见的 T 点拓扑结构,一个大 T 点两个小 T 点的方式。讲解了 DDR3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等,让学习者知其然知其所以然。

一、PADS8层DDR3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层PCB设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

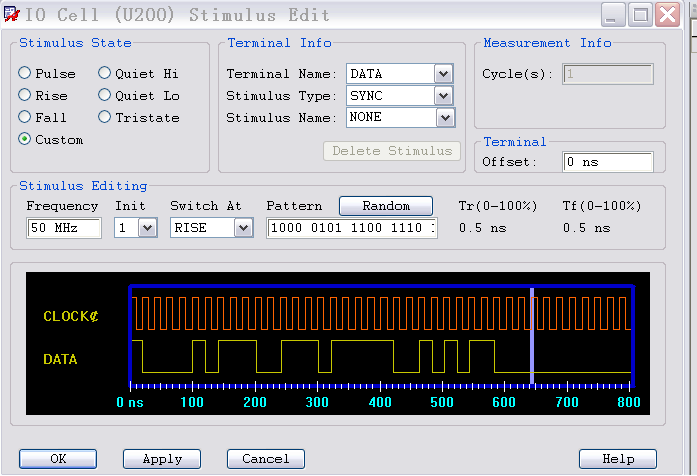

SI分析的前期准备完成之后,就可以进行信号完整性分析了,执行Analyze/SI EMI Sim/Probe命令,然后选择需要进行SI分析的网络或者差分对(模型分配中必须设置好差分对),如下图所示:

关于信号完整性的绪论

随着信息宽带化和高速化的发展,以前的低速PCB已完全不能满足日益增长信息化发展的需要,人们对通信需求的不断提高,要求信号的传输和处理的速度越来越快,相应的高速PCB的应用也越来越广,设计也越来越复杂。

信号完整性是指信号在信号线上的质量。信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的。特别是在高速电路中,所使用的芯片的切换速度过快、端接元件布设不合理、电路的互联不合理等都会引起信号的完整性问题。具体主要包括串扰、反射、过冲与下冲、振荡、信号延迟等。

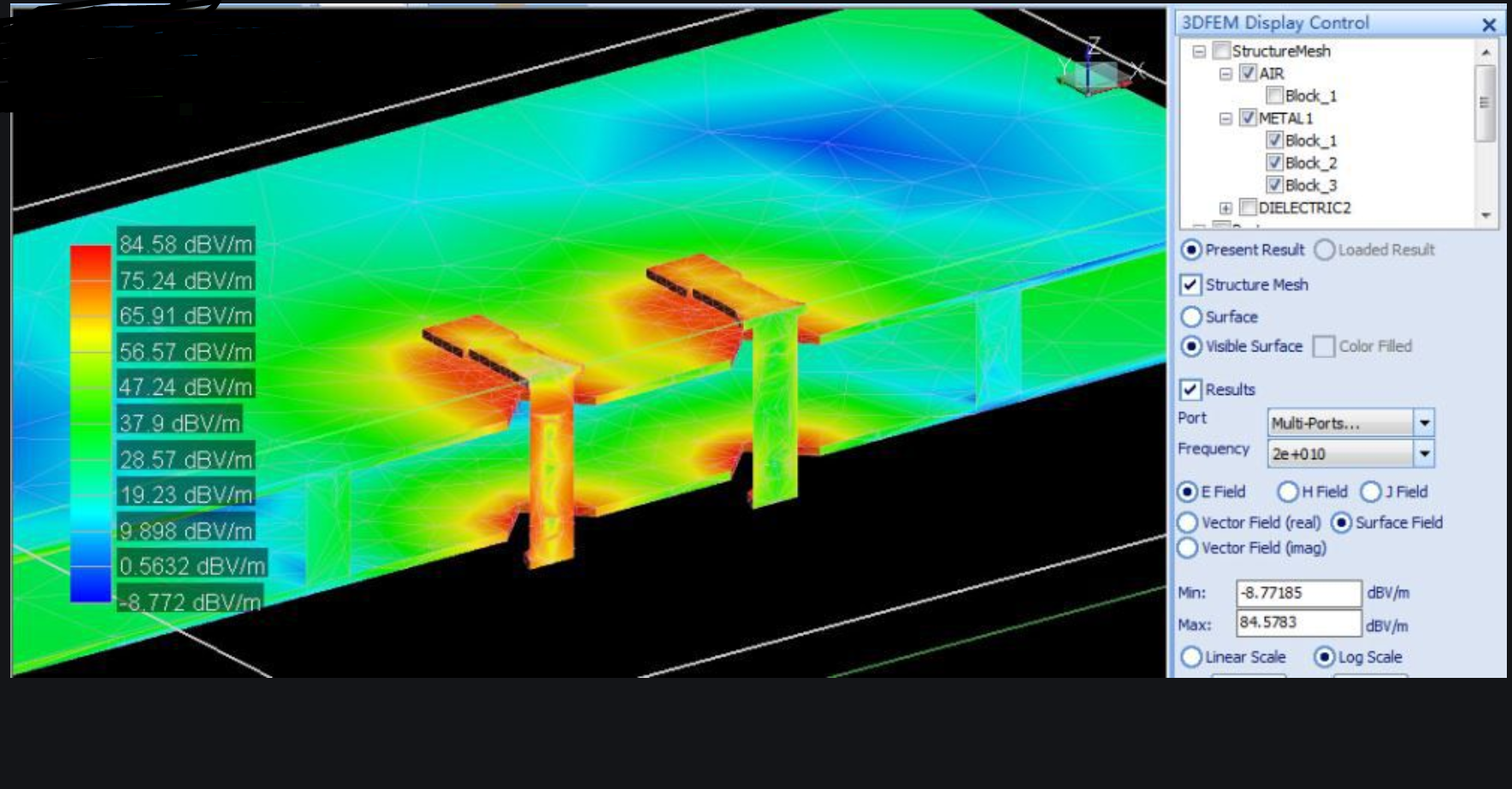

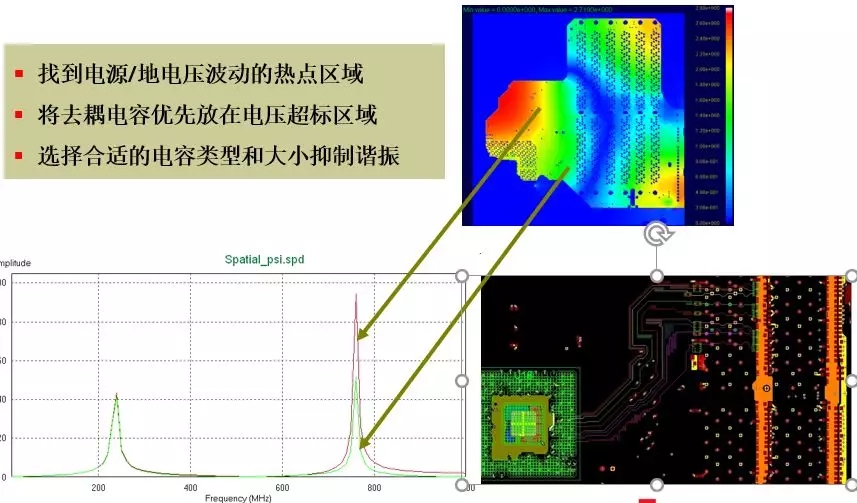

Sigrity PowerSI是IC封装和PCB设计快速准确的全波电磁场分析,作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带 S参数提取以及频域仿真。PowerSI可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压

扫码关注

扫码关注