- 全部

- 默认排序

高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

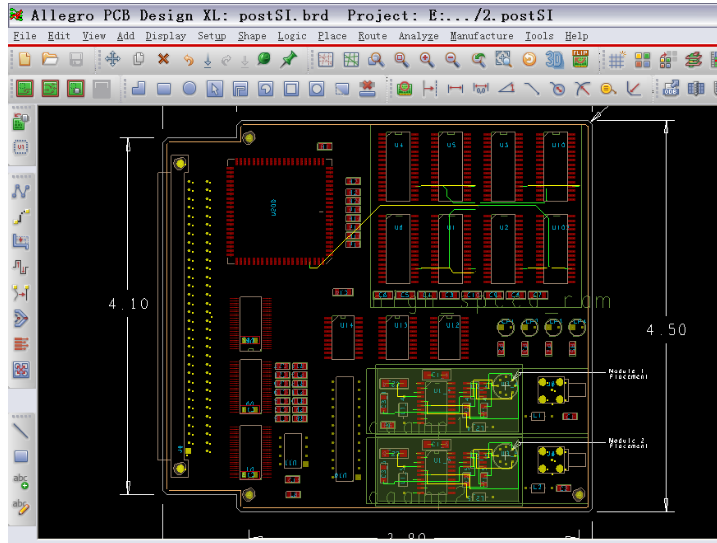

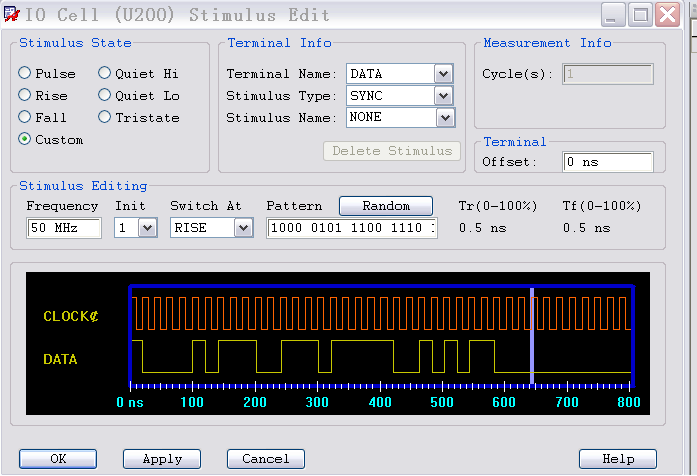

SI分析的前期准备完成之后,就可以进行信号完整性分析了,执行Analyze/SI EMI Sim/Probe命令,然后选择需要进行SI分析的网络或者差分对(模型分配中必须设置好差分对),如下图所示:

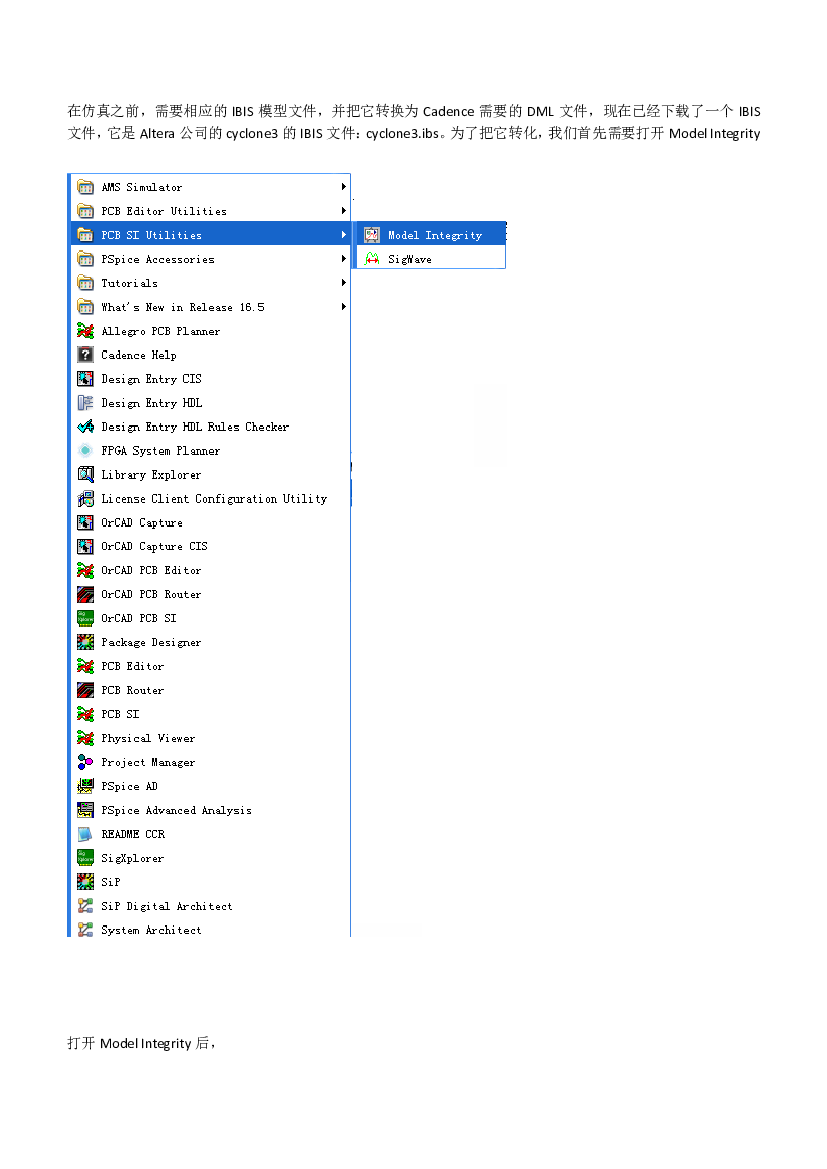

一个layout工程师学习信号完整性之路本人最早接触SI仿真的时候,只是进行一个简单的流程操作,其中涉及到的原理、模型知之甚少,再后来慢慢的接触到了深一点的东西开始自己搭建电路了解到了IBIS。用于电路仿真的模型有好多,可能IBIS是最常用

系统级信号完整性(SI)仿真是高速PCB设计的重要概念,其存在间接联系着高速PCB电路设计的正常运行,但有很多小白不清楚,甚至错将系统级SI仿真和普通的SI混为一谈,这是错误的思维误区,我们要尽量避免。一般来说,现在的EDA信号完整性根据主

随着信号速度的提高和板子尺寸的缩小,信号完整性(SI)和电源完整性(PI)分析愈发重要,但也越来越难以调试,“了解SI&PI仿真、如何做好SI和PI仿真”等已成为当代工程师需要面对的问题,下面的内容或许能给些灵感。1、SI仿真SI仿真是对高

随着电子技术的高速发展,信号完整性(SI)和电源完整性(PI)仿真的重要性日益凸显,虽然SI仿真主要关注的是信号的完整性和时序,而PI仿真关注的是电源和地的稳定性和可靠性,但依然有很多工程师不太清楚它们在板级和芯片级别有什么区别,所以下面将

朋友,如果你想学习Altium Designer(AD)那么请先了解下我国AD教学的现状与痛点:①知识体系落后教材多基于AD旧版本,未覆盖AD23/AD24新功能(如多板设计、高级SI仿真)。缺乏系统化课程,学生仅掌握基础操作,无法应对高速

扫码关注

扫码关注